本文要點

電子產品中有許多噪聲源,可能出現在系統內部和外部。

噪聲耦合抑制技術在電路設計層面和物理布線中實施,以抑制特定的噪聲源。

可以通過布線前和布線后仿真來評估噪聲耦合抑制技術的有效性。

任何在示波器上仔細觀察過低電平信號讀數的人都會熟悉電子電路中可能出現的噪聲。出現的各種固有的噪聲源在低信號電平下十分明顯。在其他以典型邏輯電平運行的系統中,由于電磁干擾和電路之間的耦合,會產生外在噪聲。這些噪聲源都需要一個特定的電路或策略來降低耦合強度或減少噪聲,或兩者兼而有之。

噪聲耦合抑制技術涉及設計特定電路、使用特定的器件,或在物理布線中放置一些結構來抑制特定的噪聲源。對于 PCB 設計師來說,修改物理布線以盡量抑制各種噪聲源非常簡單。本文將介紹可以使用哪些工具來抑制系統中不同類型的噪聲。

將噪聲耦合抑制技術與噪聲源相匹配

噪聲通常是指出現在互連或電路中的任何不需要的信號,并且可以有多個來源。有時,除非掌握必要的信息,否則很難為特定的噪聲確定具體的來源。當在電路或互連中檢測到噪聲時,最好了解是哪種耦合機制帶來了不必要的噪聲。

所有的電子噪聲最后都會導致在接收器上讀到不需要的信號,這意味著某種機制在受干擾電路或互連中誘發了一些電壓/電流。噪聲通過三種可能的機制耦合:

傳導:由于噪聲源和受干擾電路之間的直接接觸,在一個電路中產生的任何噪聲電流都可以傳導到另一個電路。

電場耦合:一般是指由于電場的存在而在電介質中感應出位移電流。在電路模型方面,電場耦合指的是通過寄生電容耦合。

磁場耦合:變化的磁場可以通過法拉第定律在導體中誘發電流,而不需要噪聲源和受干擾電路之間有直接接觸。

第一種被稱為傳導型 EMI,它依賴于噪聲源和受干擾互連/電路之間的直接接觸。后兩種會將輻射型 EMI 耦合到電路中,這是指沒有傳導到受干擾電路或互連的噪聲。

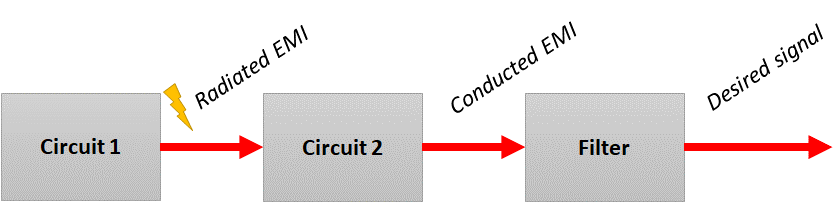

由于輻射型 EMI 可以誘發電流和電壓,一開始的輻射型 EMI 可以作為傳導型 EMI 被接收。這意味著有兩種方法來消除電子電路中的噪聲:

防止輻射型 EMI 以電容和電感方式誘發電路中的噪聲。

抑制任何傳導型 EMI,不管它是如何在電路中產生的。

接下來了解一下可以抑制電子系統中這兩種類型噪聲的布線策略。

濾波電路

濾波電路是消除傳導型 EMI 的經典方法,因為濾波器直接作用于電路中的電壓/電流。濾波器可以是寬帶的,如低/高通濾波器,或極窄帶的,如陷波濾波器。EMI 濾波器可以是單一器件,如共模扼流圈,或是涉及多個器件的復雜電路。這些電路可以針對單一頻率或較寬的頻率范圍來使用。

濾波電路可以消除源自輻射型 EMI 的傳導型 EMI。通過這種方式,濾波電路抑制了來自電路 1 和電路 2 的任何噪聲耦合。

印刷屏蔽結構

這個方法聽起來略顯陌生,但它通常是指 PCB 上任何可以對輻射型 EMI 提供屏蔽的結構。這些結構的目的是改變 PCB layout 中的寄生效應,從而阻斷電磁感應的電流。這種結構的例子包括:

電子帶隙結構

表層覆銅接地

額外的平面層

沿著波導或天線饋線等重要互連的過孔柵欄

重新設計互連結構

這種方法的目標是抑制導致磁耦合或電耦合的寄生效應。要成功做到這一點,需要從物理布線中提取寄生電容和電感的模型。互連阻抗取決于自電感和自電容的值,而寄生效應總是會導致互連阻抗與期望值有所偏差。一些額外的印刷結構或重新設計互連的幾何形狀有助于減少寄生效應,并減少通過輻射型 EMI 耦合到互連的任何噪聲的強度。

總結

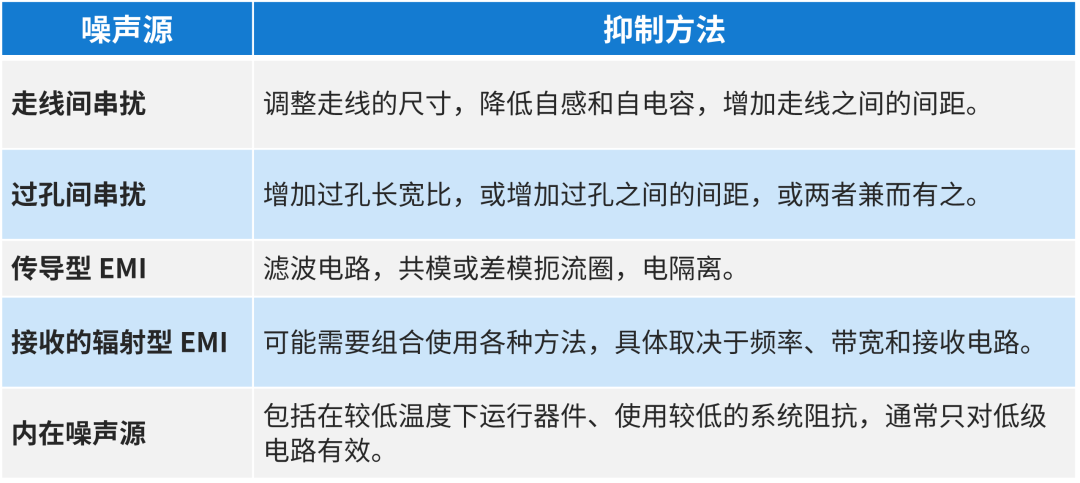

綜上所述,沒有哪種特定的技術可以抑制所有形式的噪聲耦合。在系統中使用哪種具體的噪聲耦合抑制技術,取決于所涉及的特定噪聲源和電路間耦合的功率。我們通過下列表格對上文討論的噪聲源和抑制方法進行了簡要總結。

如果有了合適的降噪技術,并準備在系統中進行驗證,最好在做原型設計之前使用仿真來對設計進行評估。傳導型 EMI 可以在電路仿真中用 SPICE 進行檢查。對于其他噪聲源而言,除非有一個準確的電路模型來描述系統,否則無法在電路層面上進行檢查。因為這些其他的抑制機制取決于精確的物理布線,所以需要用 3D 場求解器來全面評估許多噪聲抑制技術的有效性。對于 PCB 設計工程師來說,最好的場求解器應用可以直接在 PCB 設計工具內使用,并能直接根據布線數據運行模型。

-

電子產品

+關注

關注

6文章

1303瀏覽量

61181 -

電路

+關注

關注

173文章

6083瀏覽量

178746 -

噪聲

+關注

關注

13文章

1161瀏覽量

49396

發布評論請先 登錄

技術資訊 I 柔性電路設計

一種基于低噪聲電源管理架構的射頻采樣系統設計方案

技術資訊 I 新一代器件的混合信號設計

單片機抗干擾技術的常用方法

薄膜射頻/微波定向耦合器技術解析

在高密度高功率設計中采用Pickering公司新型靜電屏蔽技術, 有效抑制噪聲干擾

技術資訊 I 感應電能傳輸系統中的磁耦合電路

村田磁珠電感:高頻噪聲抑制解決方案

如何減小DAC電路的耦合影響?

海洋儀器電源抑制比測試方案26800元起

技術資訊 I 面向電路的噪聲耦合抑制技術

技術資訊 I 面向電路的噪聲耦合抑制技術

評論