SN65LV1023A-EP與SN65LV1224B-EP:10 - 66MHz LVDS 串行器/解串器的深度剖析

在高速數(shù)據(jù)傳輸領(lǐng)域,LVDS(低壓差分信號)技術(shù)憑借其低功耗、高抗干擾能力等優(yōu)勢,成為了眾多工程師的首選。今天,我們就來詳細探討一下德州儀器(TI)的SN65LV1023A - EP和SN65LV1224B - EP這兩款10 - 66MHz的10位LVDS串行器/解串器芯片組。

文件下載:sn65lv1224b-ep.pdf

一、特性亮點

1. 穩(wěn)定可靠的基線控制

這兩款芯片采用了單一裝配/測試站點和單一制造站點的設(shè)計,確保了產(chǎn)品的一致性和可靠性。同時,它們具備 - 55°C至125°C的擴展溫度性能,能夠在惡劣的環(huán)境條件下穩(wěn)定工作。此外,還提供了增強的制造源減少(DMS)支持和產(chǎn)品變更通知,讓工程師們在使用過程中更加放心。

2. 低功耗設(shè)計

在66MHz的工作頻率下,芯片組的功耗典型值小于450mW,這對于需要長時間運行的設(shè)備來說,能夠有效降低能源消耗,延長電池續(xù)航時間。

3. 快速同步與鎖定功能

支持同步模式,能夠?qū)崿F(xiàn)更快的鎖定。通過發(fā)送特定的同步模式,解串器可以在確定的時間內(nèi)鎖定到串行器的信號,確保數(shù)據(jù)的準確傳輸。同時,還配備了鎖定指示器,方便工程師實時監(jiān)控設(shè)備的工作狀態(tài)。

4. 無需外部元件

PLL(鎖相環(huán))無需外部元件,簡化了電路設(shè)計,減少了電路板的面積和成本。

5. 靈活的封裝選擇

提供28引腳的SSOP和節(jié)省空間的5×5mm QFN封裝,滿足不同應(yīng)用場景的需求。

6. 可編程邊緣觸發(fā)

時鐘具有可編程邊緣觸發(fā)功能,可根據(jù)實際應(yīng)用靈活調(diào)整數(shù)據(jù)的采樣時機。

7. 易于PCB布局

采用直通式引腳排列,方便進行PCB布局,減少了布線的復(fù)雜性。

二、功能描述

1. 工作狀態(tài)

芯片組具有初始化模式、同步模式、數(shù)據(jù)傳輸模式、掉電模式和高阻抗模式五種工作狀態(tài)。

初始化模式

在施加電源電壓$V{CC}$后,芯片的輸出進入高阻抗狀態(tài),片上上電電路禁用內(nèi)部電路。當$V{CC}$達到2.45V時,每個設(shè)備的PLL開始鎖定到本地時鐘。串行器的本地時鐘是外部提供的發(fā)送時鐘(TCLK),解串器則需要在REFCLK引腳施加本地時鐘。

同步模式

解串器的PLL必須與串行器同步才能接收有效數(shù)據(jù)。同步可以通過兩種方式實現(xiàn):

- 快速同步:串行器能夠發(fā)送特定的同步模式,由六個1和六個0以輸入時鐘速率切換組成。通過SYNC1和SYNC2輸入選擇發(fā)送同步模式,接收到有效的SYNC1或SYNC2脈沖(寬于6個時鐘周期)后,會發(fā)送1026個周期的同步模式。

- 隨機鎖定同步:解串器可以在不需要串行器發(fā)送特殊同步模式的情況下鎖定到數(shù)據(jù)流,支持開環(huán)應(yīng)用和熱插拔功能。不過,由于數(shù)據(jù)流的特性,鎖定時間會有所變化,無法準確預(yù)測。

數(shù)據(jù)傳輸模式

初始化和同步完成后,串行器從輸入$D{INO}-D{IN 9}$接收并行數(shù)據(jù),使用TCLK輸入鎖存數(shù)據(jù)。根據(jù)TCLK_R/F引腳選擇的時鐘邊緣,對數(shù)據(jù)進行采樣,并在內(nèi)部添加起始位和停止位,將數(shù)據(jù)幀化后以12倍TCLK頻率從串行數(shù)據(jù)輸出(DO±)發(fā)送。

掉電模式

當不需要數(shù)據(jù)傳輸時,可以使用掉電模式降低功耗。串行器和解串器進入掉電狀態(tài)后,PLL停止工作,輸出進入高阻抗狀態(tài),將負載電流禁用,電源電流降低到毫安級。退出掉電模式后,需要重新初始化和同步設(shè)備。

高阻抗模式

當DEN引腳為低電平時,串行器進入高阻抗模式,驅(qū)動輸出引腳(DO +和DO -)進入高阻抗狀態(tài);當REN引腳為低電平時,解串器進入高阻抗模式,接收器輸出引腳$R{outo}-R{outg}$和RCLK進入高阻抗狀態(tài)。

2. 同步模式生成(SN65LV1023A)

同步模式生成的工作方式如下:當SYNC1或SYNC2保持高電平至少6T($T = 1$個參考時鐘周期)后,會在串行線上生成10 - 26T的同步模式。在這10 - 26個周期的同步模式傳輸期間,不需要保持SYNC1或SYNC2為高電平。

同步模式生成有兩種使用情況:

- 情況一:SYNC1或SYNC2保持高電平至少6T,但不超過10 - 26T時,同步模式生成器僅生成一次10 - 26T的同步模式,串行線上跟隨同步模式的數(shù)據(jù)應(yīng)反映并行輸入。

- 情況二:SYNC1或SYNC2連續(xù)保持高電平至少1038T時,理論上應(yīng)該能觀察到連續(xù)的同步模式。但實際情況中,如果SYNC1或SYNC2保持高電平1039T,設(shè)備會連續(xù)生成2052T($= 10 - 26T + 10 - 26T$)的同步模式。

三、電氣特性與參數(shù)

1. 絕對最大額定值

了解芯片的絕對最大額定值對于確保設(shè)備的安全運行至關(guān)重要。例如,$V{CC}$到GND的電壓范圍為 - 0.3V至4V,LVTTL輸入和輸出電壓范圍為 - 0.3V至($V{CC}+0.3V$),LVDS接收器和驅(qū)動器的輸入輸出電壓范圍為 - 0.3V至3.9V等。超過這些額定值可能會導(dǎo)致設(shè)備永久性損壞。

2. 推薦工作條件

在推薦的工作條件下使用芯片,可以保證其性能的穩(wěn)定性和可靠性。例如,DVCC和AVCC的電壓范圍應(yīng)在3V至3.6V之間,雖然內(nèi)部將它們分開,但只要兩者都在該范圍內(nèi),$|DVCC - AVCC|$的差異不會影響芯片的正常工作。

3. 電氣特性

包括LVCMOS/LVTTL直流規(guī)格、LVDS直流規(guī)格、串行器和解串器的電源電流等參數(shù)。這些參數(shù)為工程師在設(shè)計電路時提供了重要的參考依據(jù),例如在選擇電源和計算功耗時,需要考慮這些電氣特性。

4. 時序要求與開關(guān)特性

串行器和解串器的時鐘周期、高低時間、輸入轉(zhuǎn)換時間、抖動等時序要求,以及LVDS輸出的轉(zhuǎn)換時間、數(shù)據(jù)建立和保持時間等開關(guān)特性,對于確保數(shù)據(jù)的準確傳輸和設(shè)備的正常工作至關(guān)重要。工程師在設(shè)計時鐘電路和數(shù)據(jù)傳輸路徑時,需要根據(jù)這些特性進行合理的布局和布線。

四、應(yīng)用信息

1. 差分走線與終端匹配

芯片的性能受到傳輸介質(zhì)特性的影響。建議使用受控阻抗介質(zhì),并在傳輸線的接收端使用與介質(zhì)特性阻抗匹配的終端電阻。采用平衡電纜(如雙絞線或緊密排列的差分走線)可以減少共模噪聲的影響,同時保持電纜或走線的長度匹配,有助于減少偏斜。

2. 拓撲結(jié)構(gòu)

串行器可以采用多種拓撲結(jié)構(gòu)進行工作,常見的有單端接點對點連接、多點連接和多串行器/解串器在同一差分總線上的多點配置。不同的拓撲結(jié)構(gòu)具有不同的特點和應(yīng)用場景,工程師需要根據(jù)實際需求進行選擇。

五、總結(jié)

SN65LV1023A - EP和SN65LV1224B - EP這兩款芯片組在高速數(shù)據(jù)傳輸領(lǐng)域具有出色的性能和豐富的功能。它們的低功耗、快速同步、靈活的工作模式以及易于布局等特點,使其成為了眾多應(yīng)用場景的理想選擇。在實際設(shè)計過程中,工程師需要充分了解芯片的特性和參數(shù),根據(jù)具體的應(yīng)用需求進行合理的電路設(shè)計和布局,以確保設(shè)備的穩(wěn)定性和可靠性。

各位工程師朋友們,在使用這兩款芯片的過程中,你們遇到過哪些問題或者有什么獨特的應(yīng)用經(jīng)驗?zāi)兀繗g迎在評論區(qū)分享交流!

發(fā)布評論請先 登錄

德州儀器高速差分接收器:SN65LVDS系列深度剖析

深入剖析SN65LVDS95 LVDS 串行器:特性、應(yīng)用與設(shè)計要點

SN65LVDS94 LVDS 串行解串接收器:設(shè)計與應(yīng)用全解析

SN65LV1023A/SN65LV1224B:10 - 66MHz 高速 LVDS 串行器/解串器的深度剖析

探索SN65LVDS95 - EP LVDS SERDES發(fā)射器:特性、應(yīng)用與設(shè)計要點

10 - MHz至66 - MHz,10:1 LVDS串行器/解串器芯片組的設(shè)計與應(yīng)用

探索SN65LVDT14-EP與SN65LVDT41-EP:LVDS技術(shù)在存儲棒接口擴展中的應(yīng)用

SN65LVDS33-EP與SN65LVDT33-EP高速差分接收器:設(shè)計與應(yīng)用詳解

探索TI SN65LVDT14-EP和SN65LVDT41-EP:LVDS技術(shù)在Memory Stick接口擴展中的應(yīng)用

10 - MHz至66 - MHz,10:1 LVDS串行器/解串器SN65LV1023A - EP與SN65LV1224B - EP的技術(shù)剖析

德州儀器高速差分線驅(qū)動器與接收器:SN65LVDS系列深度剖析

高速差分線驅(qū)動器SN65LVDS31 - EP的特性與應(yīng)用解析

深入剖析SN65LVDS822:LVDS接收器的卓越之選

SN65LVDS93B:低功耗、高分辨率的LVDS SerDes發(fā)送器的理想選擇

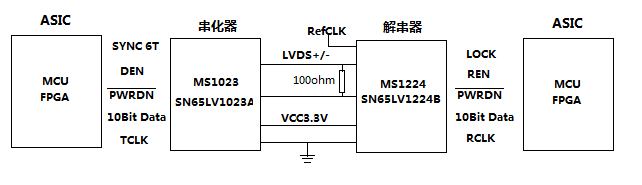

MS1023、SN65LV1023A串化器與MS1224、SN65LV1224B解串器應(yīng)用

SN65LV1023A-EP與SN65LV1224B-EP:10 - 66MHz LVDS串行器/解串器的深度剖析

SN65LV1023A-EP與SN65LV1224B-EP:10 - 66MHz LVDS串行器/解串器的深度剖析

評論