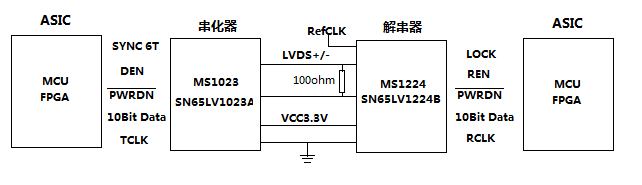

SN65LV1023A、SN65LV1224B為TI公司推出的基于BLVDS技術的串化與解串器,替代已經停產的DS90LV1023E、DS90LV1224E套片。

MS1023與MS1224是瑞盟公司基于BLVDS SerDes技術推出的并串/串并轉換器,MS1023能夠Pin to Pin替代DS90LV1023E、SN65LV1023A,MS1224 Pin to Pin替代DS90LV1224E、SN65LV1224B!但有關MS1023、MS1224應用文章稀缺,瑞盟未提供“用戶應用手冊”,今天就MS1023、MS1224應用做簡單分享,歡迎開發及應用工程師積極交流。

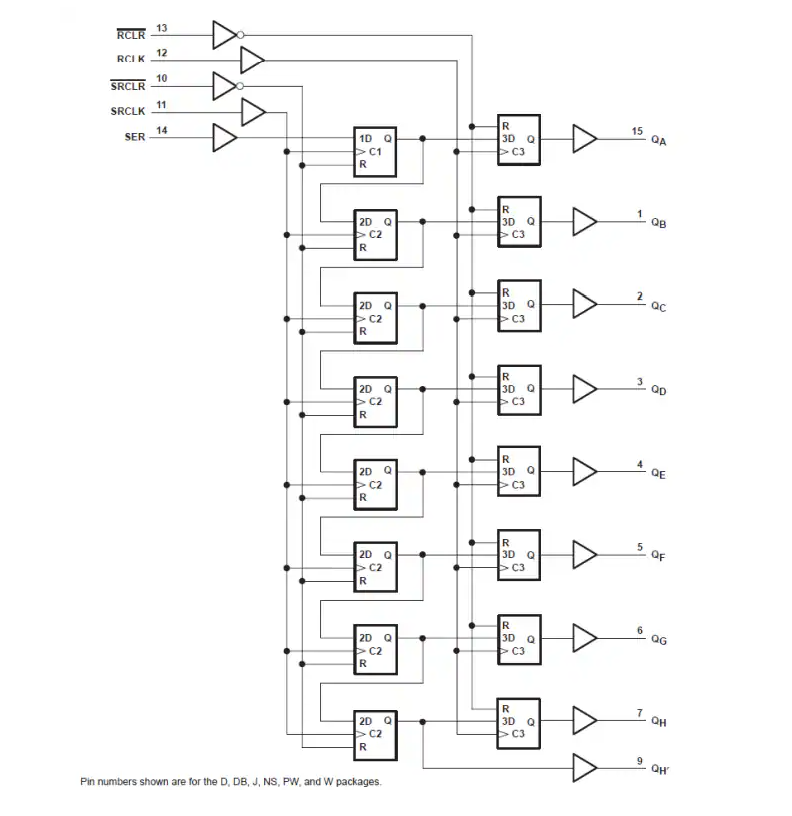

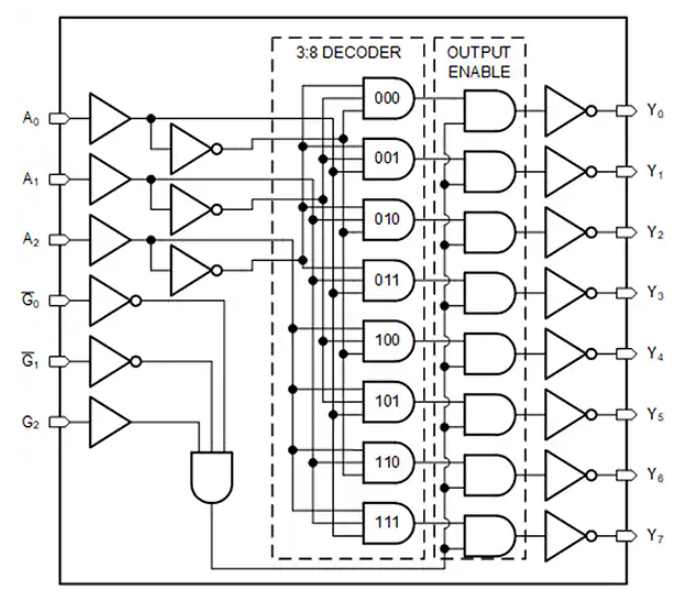

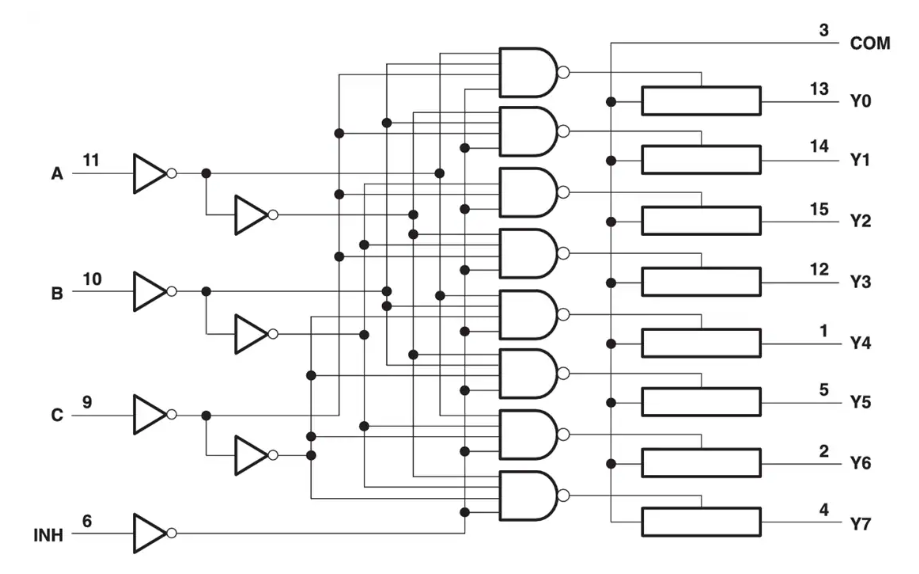

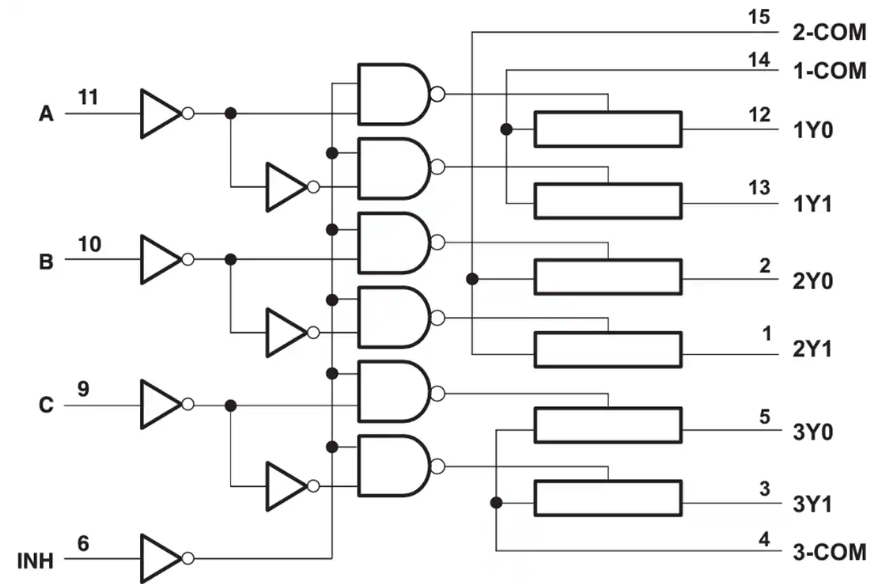

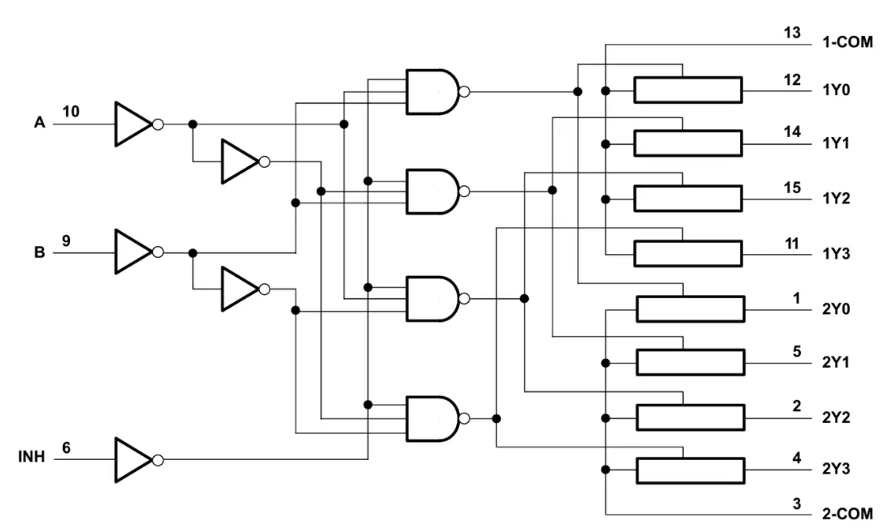

MS1023 串化器和 MS1224解串器是一對 10bit并串/串并轉換芯片,用于在 LVDS差分底板上傳輸和接收10MHz-80MHz的并行速率的串行數據。起始/停止位加載后,轉換為負載編碼輸出,串行數據速率120Mbps-960Mbps。上電時,這一對芯片可通過內部產生的 SYNC樣本信號同步模式進行初始化或者解串器與隨機數據同步。通過使用同步模式,解串器可在特定的、更短的時間參數內建立鎖定。

關于SYNC同步:

快速同步模式:SYNC樣本信號傳輸與否由串化器的SYNC1和SYNC2輸入決定。在SYNC1或SYNC2保持高電平至少6T(T=1個Refclk周期)后,SYNC模式在串行線上生成1026T。在這個1026周期的SYNC模式傳輸期間,不需要SYNC1或SYNC2保持高電平。

當連續收到有效的SYNC1或SYNC2脈沖(時間寬度超過6個時鐘周期),SYNC樣本信號將會發送由6個1和6個0組成特定的SYNC樣本信號。當MS1224解串器在LVDS輸入上檢測到邊沿傳輸, PLL鎖定來自串化器的SYNC樣本信號,此時LOCK由高轉為低電平,解串器輸出開始恢復輸入的LVDS數據。

隨機同步模式:MS1224可以工作在開環應用中,且支持熱插拔。在開環應用中,MS1224解串器可從數據流中獲取時鐘,而不需要串化器發送特定的同步模式信號。MS1224解串器在LVDS輸入上檢測到邊沿傳輸,將嘗試鎖定到內嵌的時鐘信息, 當PLL鎖定輸入的內嵌的時鐘,LOCK由高轉為低電平,解串器輸出開始恢復輸入的LVDS數據。

MS1224在開環或熱插拔情況下,數據流在本質上是隨機的,由于鎖定時間根據數據流特征而變化,所以準確時間是不可能預知的。當MS1224啟動隨機鎖定,受RMT重復性多級傳輸影響,解串器會檢測到潛在的錯誤時鐘,而延長隨機鎖定時間。在隨機同步模式下,PLL鎖定前,LOCK輸出為高電平,ROUT(0:9)、RCLK為高阻態。

總結:

⑴、不管是快速同步模式或是隨機同步模式,用戶系統最好監控MS1224 LOCK狀態,以防MS1224失鎖。當檢測到“失鎖”,如果在特定的時間內無法復位鎖定,系統可重新發送SYNC同步樣本信號。因此,最好將解串器 LOCK輸出直接連接到SYNC1、SYNC2。

⑵、將SYNC1、SYNC2短接后連接到MCU/FPGA 輸出的SYNC同步觸發電路,輸出的SYNC同步高電平觸發保持6T。

2、TCLK與LVDS數據流速率:

串化器以TCLK的12倍頻傳輸串行數據及內嵌時鐘位,每一幀串行數據流為10bit數據,并嵌入1bit起始位+1bit停止位到每一幀數據的寄存器中,起始位恒定為高,停止位恒定為低,在串行數據流中,起始/停止位為嵌入的時鐘信息。

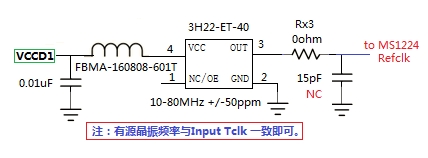

例如 TCLK為40MHz,串行速率為 40×12=480Mbps,由于僅有10bit輸入數據,有效數據速率實際為10倍的TCLK頻率,所以有效數據速率40×10=400Mbps。提供給MS1023之TCLK的數據源要求在10MHz至80MHz之間。而提供給MS1224之RefCLK也應與MS1023一致,例如 MS1023 TCLK為40MHz,則MS1224 RefCLK為40MHz,RefCLK建議用外掛有源晶振,減少PCB板載連線。參考如下:

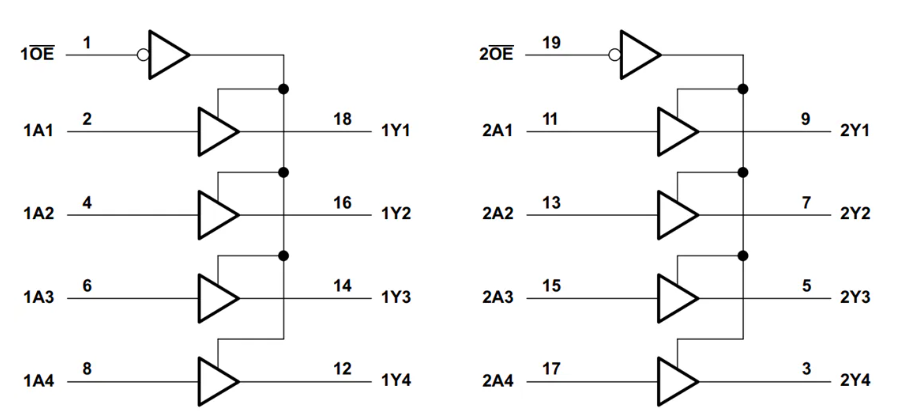

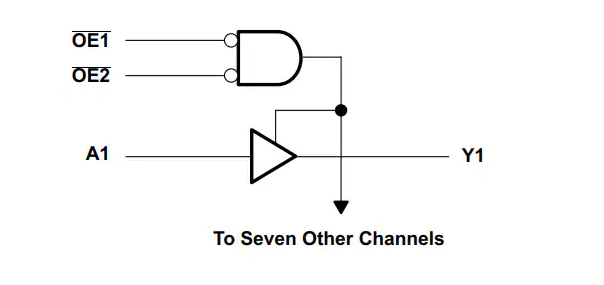

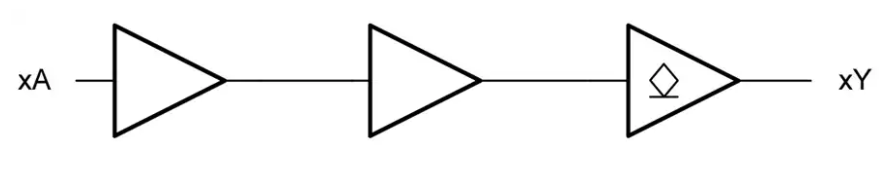

3、關于DEN、REN控制(高阻態模式):

當DEN被置低時,串化器進入高阻模式。這將使所有輸出腳(DO+和 DO-)進入高阻狀態。當驅動DEN為高 , 串化器恢復到先前的狀態 ,同時其他所有控制引腳保持靜態(SYNC1,SYNC2, PWRDN ,TCLK_R/F)。

當REN腳被置低時,解串器進入高阻模式,解串器的輸出腳(ROUT0-ROUT9)和 RCLK進入高阻狀態。 LOCK保持有效(Active),用來跟蹤PLL的狀態。因此,DEN、REN可與MCU/FPGA建立邏輯控制,待機時,DEN、REN設置為低電平。

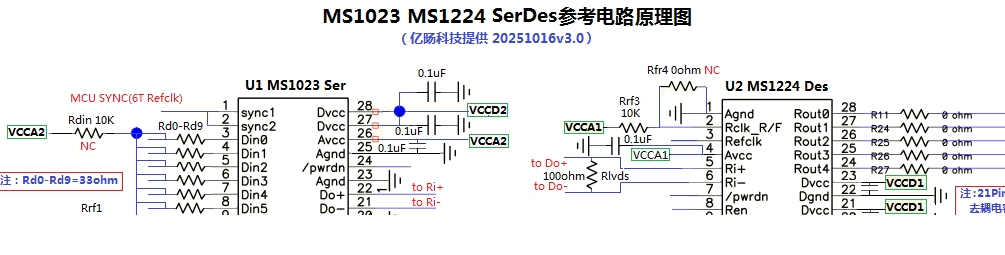

4、MS1023 MS1224應用參考原理圖

以下為展示的簡易原理圖,如果你是終端應用工程師,可以聯系我們,已獲得詳細原理圖及技術支持。

審核編輯 黃宇

-

SerDes

+關注

關注

8文章

232瀏覽量

36598 -

SN65LV1023A

+關注

關注

0文章

3瀏覽量

8379 -

SN65LV1224B

+關注

關注

0文章

2瀏覽量

6589

發布評論請先 登錄

SN65LVDS93B:低功耗、高分辨率的LVDS SerDes發送器的理想選擇

SN65LVDxx高速差分線路驅動器和接收器:特性、應用與設計要點

SN65LVDS33和SN65LVDS34高速差分接收器數據手冊

SN74LV244A Octal Buffer/Driver技術解析:高速3態輸出的多功能解決方案

SN74LV541A:2-5.5V八路3態緩沖器/驅動器技術解析

SN74LV594A:2-5.5V帶輸出寄存器的8位移位寄存器技術解析

SN74LV138A 3-8線解碼器/解復用器技術解析與應用指南

SN74LV6T07 Hex開漏緩沖器技術解析與應用指南

SN74LV6T06/SN74LV6T06-Q1六通道開漏逆變器數據手冊

Texas Instruments SN74LV4051A/SN74LV4051A-Q1模擬多路復用器和解復用器數據手冊

Texas Instruments SN74LV4053A/SN74LV4053A-Q1模擬多路復用器和解復用器數據手冊

Texas Instruments SN74LV4052A/SN74LV4052A-Q1雙模擬多路復用器和解復用器數據手冊

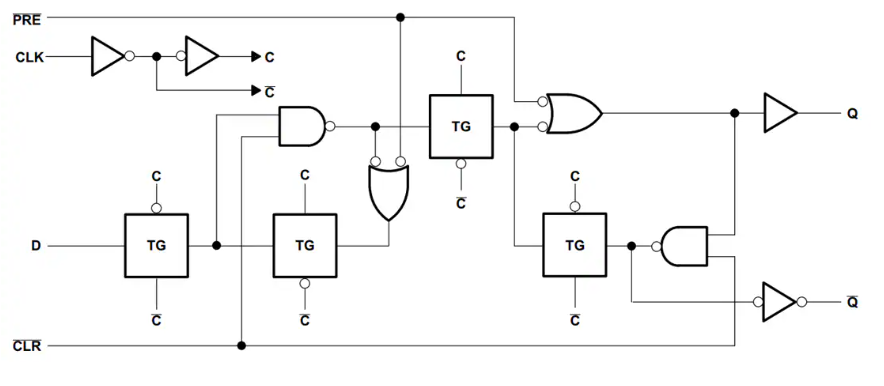

Texas Instruments SN74LV74A/SN74LV74A-Q1雙通道D型觸發器數據手冊

MS1023、SN65LV1023A串化器與MS1224、SN65LV1224B解串器應用

MS1023、SN65LV1023A串化器與MS1224、SN65LV1224B解串器應用

評論