10 - MHz至66 - MHz,10:1 LVDS串行器/解串器SN65LV1023A - EP與SN65LV1224B - EP的技術(shù)剖析

在電子設(shè)計(jì)領(lǐng)域,高速數(shù)據(jù)傳輸一直是一個(gè)關(guān)鍵的研究方向。SN65LV1023A - EP和SN65LV1224B - EP這對(duì)10位串行器/解串器芯片組,專為在10 MHz至66 MHz的時(shí)鐘速度下通過差分背板或非屏蔽雙絞線(UTP)傳輸數(shù)據(jù)而設(shè)計(jì),為高速數(shù)據(jù)傳輸提供了一種可靠的解決方案。下面我們將深入探討它們的特性、功能、電氣參數(shù)等方面。

文件下載:sn65lv1023a-ep.pdf

特性亮點(diǎn)

1. 溫度與制造支持

該芯片組具有擴(kuò)展的溫度性能,能在 - 55°C至125°C的環(huán)境下穩(wěn)定工作。同時(shí),它采用了受控基線,即單一裝配/測(cè)試地點(diǎn)和單一制造地點(diǎn),這有助于提高產(chǎn)品的一致性和可靠性。此外,它還提供了增強(qiáng)的制造資源減少(DMS)支持和產(chǎn)品變更通知,確保了產(chǎn)品在整個(gè)生命周期內(nèi)的穩(wěn)定供應(yīng)。

2. 低功耗與同步特性

在66 MHz時(shí),芯片組的功耗典型值小于450 mW,具有較低的功耗。它還具備同步模式,可實(shí)現(xiàn)更快的鎖定,并且有鎖定指示器,方便用戶監(jiān)控工作狀態(tài)。另外,PLL無需外部組件,簡(jiǎn)化了設(shè)計(jì)。

3. 數(shù)據(jù)帶寬與封裝優(yōu)勢(shì)

芯片組支持100 - Mbps至660 - Mbps的串行LVDS數(shù)據(jù),在10 - MHz至66 - MHz的系統(tǒng)時(shí)鐘下具有較高的有效數(shù)據(jù)帶寬。它提供28 - 引腳SSOP和節(jié)省空間的5 × 5 mm QFN封裝,并且引腳兼容,方便PCB布局。同時(shí),時(shí)鐘上的可編程邊緣觸發(fā)功能進(jìn)一步提高了設(shè)計(jì)的靈活性。

功能描述

1. 工作狀態(tài)

芯片組具有初始化模式、同步模式、數(shù)據(jù)傳輸模式、掉電模式和高阻抗模式五種工作狀態(tài)。

- 初始化模式:在數(shù)據(jù)傳輸開始之前,需要對(duì)串行器和解串器的PLL進(jìn)行初始化,使其與本地時(shí)鐘同步。當(dāng)VCC施加到器件時(shí),輸出進(jìn)入高阻抗?fàn)顟B(tài),直到VCC達(dá)到2.45V,PLL開始鎖定本地時(shí)鐘。

- 同步模式:解串器的PLL必須與串行器同步才能接收有效數(shù)據(jù)。同步可以通過快速同步或隨機(jī)鎖定同步兩種方式實(shí)現(xiàn)。快速同步通過串行器發(fā)送特定的SYNC模式,使解串器在確定的時(shí)間內(nèi)鎖定;隨機(jī)鎖定同步則允許解串器在沒有特殊SYNC模式的情況下鎖定數(shù)據(jù)流,適用于開環(huán)應(yīng)用和熱插拔場(chǎng)景。

- 數(shù)據(jù)傳輸模式:初始化和同步完成后,串行器接收并行數(shù)據(jù),并使用TCLK輸入鎖存數(shù)據(jù)。數(shù)據(jù)在內(nèi)部添加起始和停止位后,以12倍TCLK頻率的速率從串行數(shù)據(jù)輸出發(fā)送。

- 掉電模式:當(dāng)不需要數(shù)據(jù)傳輸時(shí),可以使用掉電模式來降低功耗。在掉電模式下,PLL停止工作,輸出進(jìn)入高阻抗?fàn)顟B(tài)。

- 高阻抗模式:當(dāng)DEN引腳為低電平時(shí),串行器進(jìn)入高阻抗模式;當(dāng)REN引腳為低電平時(shí),解串器進(jìn)入高阻抗模式。

2. 同步模式的細(xì)節(jié)

同步模式是芯片組的一個(gè)重要特性,下面我們?cè)敿?xì)介紹同步模式下的同步模式生成和同步過程。

- 同步模式生成:當(dāng)SYNC1或SYNC2保持高電平至少6T(T = 1個(gè)refclk周期)時(shí),串行線上會(huì)生成1026T的SYNC模式。在這1026個(gè)周期的SYNC模式傳輸期間,不需要一直保持SYNC1或SYNC2為高電平。根據(jù)SYNC1或SYNC2保持高電平的時(shí)間不同,會(huì)有不同的SYNC模式生成情況。

- 同步過程:解串器通過檢測(cè)LVDS輸入的邊緣轉(zhuǎn)換來嘗試鎖定嵌入式時(shí)鐘信息。當(dāng)解串器鎖定LVDS數(shù)據(jù)時(shí),LOCK輸出變?yōu)榈碗娖剑硎窘獯饕殉晒︽i定。

電氣參數(shù)

1. 絕對(duì)最大額定值

芯片組的絕對(duì)最大額定值規(guī)定了其在各種條件下的最大承受能力,包括電壓、電流、溫度等方面。例如,Vcc到GND的電壓范圍為 - 0.3V至4V,LVTTL輸入電壓范圍為 - 0.3V至(Vcc + 0.3 V),靜電放電HBM可達(dá)6kV等。超過這些額定值可能會(huì)導(dǎo)致器件永久性損壞。

2. 推薦工作條件

推薦工作條件給出了芯片組在正常工作時(shí)的最佳參數(shù)范圍。例如,DVCC和AVCC的電壓范圍為3V至3.6V,TCLK的頻率范圍為10 MHz至66 MHz等。在這些條件下,芯片組能夠發(fā)揮最佳性能。

3. 電氣特性

電氣特性詳細(xì)描述了芯片組的各種電氣參數(shù),包括LVCMOS/LVTTL直流規(guī)格、LVDS直流規(guī)格、串行器和解串器的開關(guān)特性等。例如,LVDS輸出差分電壓(DO +) - (DO -)的典型值為450 mV,串行器的PLL鎖定時(shí)間為1026xtTCP等。這些參數(shù)對(duì)于設(shè)計(jì)和驗(yàn)證電路至關(guān)重要。

應(yīng)用建議

1. 差分走線和端接

芯片組的性能受傳輸介質(zhì)特性的影響。在設(shè)計(jì)時(shí),應(yīng)使用受控阻抗介質(zhì),并在傳輸線的接收端進(jìn)行端接,以匹配介質(zhì)的特性阻抗。建議使用平衡電纜,如雙絞線或緊密排列的差分走線,以減少噪聲干擾。同時(shí),要保持電纜或走線的長(zhǎng)度匹配,以減少偏斜。

2. 拓?fù)浣Y(jié)構(gòu)

芯片組可以在多種拓?fù)浣Y(jié)構(gòu)下工作,常見的有單點(diǎn)端接點(diǎn)對(duì)點(diǎn)連接、多點(diǎn)配置和多串行器/解串器在同一差分總線上的配置。不同的拓?fù)浣Y(jié)構(gòu)需要不同的端接方式和負(fù)載匹配,以確保信號(hào)的穩(wěn)定傳輸。例如,單點(diǎn)端接點(diǎn)對(duì)點(diǎn)連接中,在解串器端使用單個(gè)端接電阻;多點(diǎn)配置中,在總線的遠(yuǎn)端使用50 - kΩ電阻進(jìn)行端接。

總結(jié)

SN65LV1023A - EP和SN65LV1224B - EP芯片組以其出色的特性和功能,為10 - MHz至66 - MHz的高速數(shù)據(jù)傳輸提供了可靠的解決方案。在實(shí)際應(yīng)用中,電子工程師需要根據(jù)具體的設(shè)計(jì)需求,合理選擇工作模式、優(yōu)化PCB布局、匹配端接電阻等,以充分發(fā)揮芯片組的性能。同時(shí),要嚴(yán)格遵守其絕對(duì)最大額定值和推薦工作條件,確保器件的可靠性和穩(wěn)定性。大家在使用這對(duì)芯片組進(jìn)行設(shè)計(jì)時(shí),有沒有遇到過什么特別的問題呢?歡迎在評(píng)論區(qū)分享交流。

-

高速數(shù)據(jù)傳輸

+關(guān)注

關(guān)注

0文章

257瀏覽量

7188

發(fā)布評(píng)論請(qǐng)先 登錄

SN74LV8T139 - EP 雙 2 至 4 位解碼器/解復(fù)用器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

深入剖析SN65LVDS95 LVDS 串行器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

深入剖析DS92LV16:16位總線LVDS串行器/解串器的卓越性能與應(yīng)用

深入剖析SCAN921023和SCAN921224:20 - 66 MHz 10位總線LVDS串行器與解串器

SN65LV1023A/SN65LV1224B:10 - 66MHz 高速 LVDS 串行器/解串器的深度剖析

探索SN65LVDS95 - EP LVDS SERDES發(fā)射器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

10 - MHz至66 - MHz,10:1 LVDS串行器/解串器芯片組的設(shè)計(jì)與應(yīng)用

探索SN65LVDT14-EP與SN65LVDT41-EP:LVDS技術(shù)在存儲(chǔ)棒接口擴(kuò)展中的應(yīng)用

SN65LVDS33-EP與SN65LVDT33-EP高速差分接收器:設(shè)計(jì)與應(yīng)用詳解

探索TI SN65LVDT14-EP和SN65LVDT41-EP:LVDS技術(shù)在Memory Stick接口擴(kuò)展中的應(yīng)用

SN65LV1023A-EP與SN65LV1224B-EP:10 - 66MHz LVDS串行器/解串器的深度剖析

德州儀器高速差分線驅(qū)動(dòng)器與接收器:SN65LVDS系列深度剖析

高速差分線驅(qū)動(dòng)器SN65LVDS31 - EP的特性與應(yīng)用解析

深入剖析SN65LVDS822:LVDS接收器的卓越之選

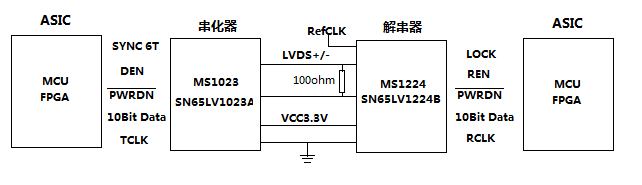

MS1023、SN65LV1023A串化器與MS1224、SN65LV1224B解串器應(yīng)用

10 - MHz至66 - MHz,10:1 LVDS串行器/解串器SN65LV1023A - EP與SN65LV1224B - EP的技術(shù)剖析

10 - MHz至66 - MHz,10:1 LVDS串行器/解串器SN65LV1023A - EP與SN65LV1224B - EP的技術(shù)剖析

評(píng)論