探索DS90URxxx-Q1:5MHz至43MHz DC平衡24位FPD-Link II串行器和解串器芯片組

在電子設計領域,數據傳輸的高效性和穩定性一直是工程師們追求的目標。今天,我們將深入探討德州儀器(TI)的DS90URxxx - Q1芯片組,它在圖形數據傳輸方面表現出色,為我們的設計帶來了新的可能性。

文件下載:ds90ur124.pdf

一、芯片組概述

DS90URxxx - Q1芯片組由DS90UR241串行器和DS90UR124解串器組成,能夠將24位并行總線轉換為帶有嵌入式時鐘信息的全透明數據/控制FPD - Link II LVDS串行流。這個芯片組專為驅動需要18位色深的顯示器而設計,支持RGB666 + HS、VS、DE + 三個額外通用數據通道。其工作頻率范圍為5MHz至43MHz,可在屏蔽雙絞線(STP)上傳輸數據長達10米。

二、特性亮點

2.1 高兼容性與數據壓縮

2.2 高性能傳輸

- 時鐘范圍:像素時鐘范圍為5MHz至43MHz,適用于多種應用場景。

- DC平衡與AC耦合:嵌入式時鐘具有DC平衡功能,支持AC耦合數據傳輸,確保數據傳輸的穩定性。

- 長距離驅動:能夠驅動長達10米的屏蔽雙絞線電纜,滿足不同的布線需求。

2.3 汽車級品質

2.4 其他特性

- 無參考時鐘需求:解串器無需參考時鐘,降低了系統復雜度。

- 熱插拔支持:支持熱插拔功能,方便系統的安裝和維護。

- EMI降低:串行器接受擴頻輸入,串行鏈路上進行數據隨機化和混洗,解串器提供可調PTO(漸進開啟)LVCMOS輸出,有效降低電磁干擾。

三、引腳配置與功能

3.1 串行器(DS90UR241)

串行器采用48引腳TQFP封裝,其主要引腳功能如下:

- LVCMOS并行接口引腳:包括24位數據輸入引腳DIN[23:0]和時鐘輸入引腳TCLK,用于輸入并行數據和時鐘信號。

- 控制和配置引腳:如DEN用于控制LVDS驅動器輸出的使能,PRE用于選擇預加重級別,RAOFF用于控制隨機化功能等。

- LVDS串行接口引腳:DoUT + 和DoUT - 為LVDS輸出引腳,用于輸出串行數據。

- 電源/接地引腳:提供模擬和數字電壓供應,確保芯片的正常工作。

3.2 解串器(DS90UR124)

解串器采用64引腳TQFP封裝,主要引腳功能如下:

- LVCMOS并行接口引腳:包括并行數據輸出引腳Rout[23:0]和時鐘輸出引腳RCLK,用于輸出解串后的并行數據和時鐘信號。

- 控制和配置引腳:如LOCK用于指示接收器PLL的鎖定狀態,PTOSEL用于選擇漸進開啟操作模式等。

- BIST模式引腳:用于內置自測試(BIST)功能,方便進行測試驗證。

- 電源/接地引腳:為芯片提供穩定的電源供應。

四、規格參數

4.1 絕對最大額定值

芯片的絕對最大額定值規定了其在不同條件下的極限參數,如電源電壓范圍為 - 0.3V至4V,結溫最高可達150℃等。超過這些額定值可能會導致芯片永久性損壞。

4.2 ESD額定值

芯片具有良好的靜電防護能力,不同封裝的引腳在HBM、CDM和ISO 10605等測試標準下都有相應的ESD額定值,確保在實際應用中能夠抵御靜電干擾。

4.3 推薦工作條件

推薦的工作條件包括電源電壓范圍為3.0V至3.6V,工作溫度范圍為 - 40℃至105℃,時鐘速率為5MHz至43MHz等。在這些條件下,芯片能夠穩定工作,發揮最佳性能。

4.4 熱信息

文檔提供了芯片的熱阻參數,如結到環境熱阻、結到外殼熱阻等,幫助工程師進行散熱設計,確保芯片在工作過程中溫度不會過高。

4.5 電氣特性

詳細列出了LVCMOS和LVDS的直流和交流特性參數,如輸入輸出電壓、電流、延遲時間等,為電路設計提供了精確的參考。

五、詳細工作原理

5.1 初始化和鎖定機制

在數據傳輸之前,串行器和解串器需要進行初始化,即同步兩者的PLL。串行器先鎖定輸入時鐘源,解串器再同步到串行器。解串器能夠在不使用單獨參考時鐘源的情況下鎖定數據流,實現真正的“即插即鎖”功能。

5.2 數據傳輸

串行器通過TCLK輸入將數據時鐘到芯片中,數據通過DOUT±輸出。在串行數據流中,除了24位數據外,還包含CLK1、CLK0、DCA、DCB四個開銷位,用于實現嵌入式時鐘和數據驗證等功能。解串器接收到LVDS串行數據流后,將其轉換回24位并行數據和恢復時鐘。

5.3 重新同步

如果解串器失去鎖定,它會自動嘗試重新建立鎖定。通過監測嵌入式時鐘信息,解串器能夠識別時鐘邊緣并重新鎖定數據流,確保數據的連續性和完整性。

5.4 掉電模式

串行器和解串器都支持掉電模式,通過TPWDNB和RPWDNB引腳控制。在掉電模式下,PLL停止工作,輸出進入三態,可有效降低功耗。退出掉電模式后,需要重新初始化和鎖定才能繼續進行數據傳輸。

5.5 三態模式

串行器在DEN或TPWDNB引腳為低電平時進入三態,解串器在REN或RPWDNB引腳為低電平時進入三態。三態模式可用于控制輸出的開啟和關閉,方便系統的設計和調試。

5.6 預加重功能

串行器具有預加重功能,通過PRE引腳和外部電阻設置預加重級別。預加重能夠補償長距離或有損傳輸介質的影響,提高信號質量,增加傳輸距離。

5.7 AC耦合和端接

芯片支持AC耦合互連,通過在LVDS信號路徑中插入外部AC耦合電容實現。同時,需要在串行器輸出和解串器輸入處進行端接,常用100Ω電阻,以確保信號的反射控制和電流回路的完整性。文檔還提供了多種接收器端接選項,可根據不同的應用場景選擇合適的端接方式。

5.8 信號質量增強器

解串器的SLEW引腳可用于調節LVCMOS輸出的驅動強度,PTOSEL引腳可引入銀行偏斜,減少同時開關噪聲和系統接地反彈,提高信號質量。

5.9 @SPEED - BIST測試功能

芯片具備內置自測試(BIST)功能,通過BISTEN和BISTM引腳控制。BIST功能可在不使用專業昂貴測試設備的情況下,對整個高速串行鏈路進行測試驗證,方便供應商進行生產和現場診斷。

5.10 向后兼容模式

通過RAOFF引腳,芯片可與DS90C241和DS90C124設備實現向后兼容,方便系統的升級和改造。

六、應用與實現

6.1 應用信息

DS90URxxx - Q1芯片組適用于汽車中央信息顯示、汽車儀表盤顯示、汽車平視顯示和遠程攝像頭駕駛員輔助系統等應用。它能夠在120Mbps至1.03Gbps的吞吐量下,將24位并行LVCMOS數據通過單條串行LVDS鏈路進行傳輸。

6.2 典型應用連接

文檔給出了串行器和解串器的典型應用連接圖,包括LVDS輸出的端接、耦合電容的使用、電源旁路電容的放置等。在實際應用中,需要根據具體需求對引腳進行合理配置,如設置TRFB引腳選擇時鐘邊沿,設置VODSEL引腳選擇輸出差分電壓等。

6.3 電源供應建議

芯片設計工作在3.3V輸入核心電壓供應下,部分引腳為不同電路部分提供單獨的電源和接地,以隔離開關噪聲影響。可使用外部濾波器為敏感電路(如PLL)提供干凈的電源。

6.4 布局

6.4.1 布局指南

PCB布局和電源系統設計應確保為芯片提供低噪聲電源。采用薄介質(2至4密耳)的電源/接地夾層可提高電源系統性能,減少外部旁路電容的影響。外部旁路電容應包括RF陶瓷和鉭電解電容,且推薦使用表面貼裝電容。LVDS互連應使用100Ω耦合差分對,遵循S/2S/3S規則,減少過孔數量,保持走線平衡,盡量靠近TX輸出和RX輸入進行端接。

6.4.2 布局示例

文檔提供了串行器和解串器的布局示例圖,為工程師進行實際布局設計提供了參考。

七、總結

DS90URxxx - Q1芯片組以其豐富的特性、良好的電氣性能和廣泛的應用場景,為電子工程師在圖形數據傳輸領域提供了一個優秀的解決方案。在實際設計中,我們需要根據具體需求合理選擇芯片的工作模式和配置參數,同時注意引腳連接、電源供應、布局布線等方面的問題,以確保系統的穩定性和可靠性。你在使用類似芯片組時遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

數據傳輸

+關注

關注

9文章

2201瀏覽量

67579

發布評論請先 登錄

DS90C241和DS90C124:5 - MHz至35 - MHz DC平衡24位FPD - Link II串行器和解串器深度解析

詳解DS90C241與DS90C124:5 - 35MHz FPD - Link II串行器與解串器芯片組

汽車級FPD-Link II串行器和解串器芯片組DS90URxxx-Q1技術解析

深度解析DS90URxxx - Q1:5MHz至43MHz DC平衡24位FPD - Link II串行器和解串器芯片組

探索DS90C241和DS90C124:5 - 35MHz DC平衡24位FPD - Link II串行器與解串器

探索DS90C241和DS90C124:5 - MHz至35 - MHz DC平衡24位FPD - Link II串行器和解串器

探索DS90UB901Q/DS902Q:汽車應用的理想FPD - Link III芯片組

解析DS90UR908Q:FPD-Link II到FPD-Link的高效轉換器

探索DS90UB903Q/DS90UB904Q:FPD - Link III的卓越解決方案

探索DS90UR903Q/DS90UR904Q:FPD - Link II芯片組的卓越性能與應用

汽車電子利器:DS90UR910-Q1 10 到 75 MHz 24 位彩色 FPD-Link II 到 CSI-2 轉換器解析

汽車娛樂系統利器:DS90UH927Q-Q1 FPD-Link III 串行器深度解析

汽車電子利器:DS90UB927Q-Q1 FPD-Link III 串行器深度解析

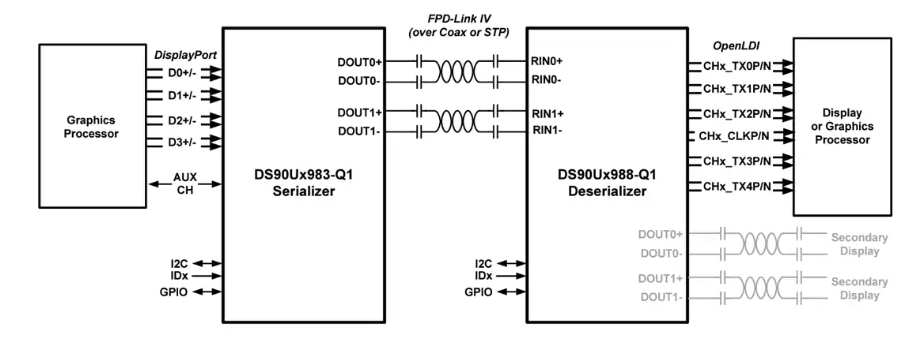

Texas Instruments DS90UB988-Q1 FPD-Link IV轉OpenLDI解串器數據手冊

探索DS90URxxx-Q1:5MHz至43MHz DC平衡24位FPD-Link II串行器和解串器芯片組

探索DS90URxxx-Q1:5MHz至43MHz DC平衡24位FPD-Link II串行器和解串器芯片組

評論