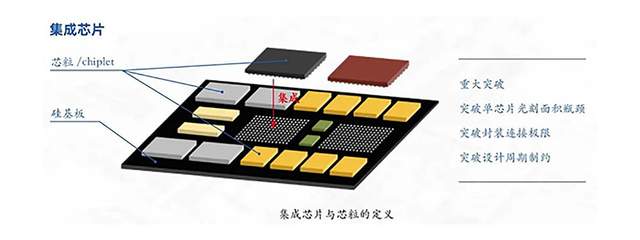

前言: 當業界為2納米之后的物理極限未雨綢繆,一條名為“Chiplet”(芯粒)的技術路徑正將半導體創新從晶圓廠引向封裝廠。它允許多個采用不同工藝、來自不同廠商的芯粒,像組建“聯盟”一樣通過先進封裝(如CoWoS)集成在一起,共同構成一個更強大的系統級芯片。然而,當這個功能強大、成員各異的“芯片聯盟”被密封在同一個封裝體內,一個前所未有的挑戰隨之浮現:我們該如何為這個高度異構、內部緊密協作的“微系統”,進行一次確保其長期穩定運行的“終極體檢”? 傳統的單體芯片測試方法,在這個聯盟面前已經徹底失效。

一、 趨勢洞察:從“單體檢測”到“系統級驗證”的范式革命

Chiplet技術被視為延續摩爾定律經濟效益的關鍵,其核心優勢在于通過異構集成提升性能、降低成本和加速上市。然而,這也從根本上改變了芯片測試的范式和對象。測試的目標不再是單個、均質的硅片,而是一個在封裝后才首次形成的完整電子系統。

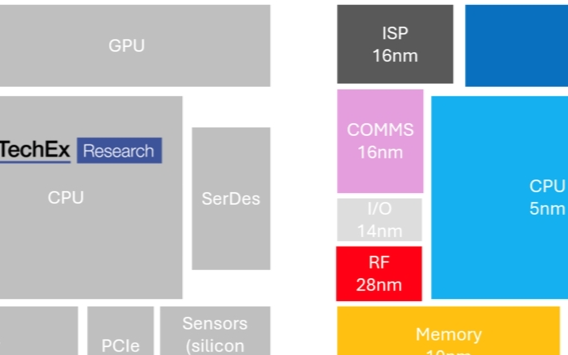

這個“系統”的復雜性體現在:它可能包含采用5納米工藝的計算芯粒、12納米工藝的I/O芯粒、以及來自第三方的存儲芯粒或模擬芯粒。它們通過硅中介層或基板上的高密度互連線(如UCIe標準)通信,共享電源和散熱路徑。因此,傳統的在晶圓測試(CP)和最終測試(FT)之間清晰的職責劃分被打破,測試重心必須后移,聚焦于封裝完成后的 “系統級測試(System Level Test, SLT)” 與 “互連及協同功能驗證” 。這不僅是測試地點的變化,更是測試哲學、技術和工具的全面升級。

二、 技術挑戰:“芯片聯盟”體檢的三大難關

為這樣一個異構“聯盟”提供可靠的“體檢”報告,需要攻克三大核心難關,它們共同定義了Chiplet時代測試的復雜性:

1.互連通道的“信號完整性”極限測試

芯粒間互連(如UCIe)的數據速率已步入數十Gbps的超高速領域。在封裝后,微米級的走線長度差異、中介層的材質缺陷、或熱應力引起的形變,都可能導致信號完整性(SI)的劣化,引發間歇性的高誤碼率。測試必須在實際工作頻率下,對每一條關鍵高速通道進行誤碼率(BER)掃描、眼圖分析和串擾評估,而這在封裝后有限的可訪問性下極為困難。

2.系統級的“功耗與熱”協同管理驗證

不同芯粒的功耗特性、工作狀態(激活/休眠)可能差異巨大,它們被緊密封裝后,會產生復雜的相互熱影響和電源噪聲耦合。測試需要模擬真實應用場景,驗證在最壞情況功耗負載下,電源配送網絡(PDN)能否穩定供電,局部熱點是否會導致某個芯粒降頻或失效,以及整個系統的熱管理方案是否有效。

3.異構系統的“協同配置”與燒錄

Chiplet系統在啟動前,需要為各個芯粒分別載入正確的固件、微碼、驅動程序和特定的協同配置參數(如互連訓練參數、功耗管理策略)。這個過程(燒錄)變得異常復雜:它本質上是為多個獨立的“大腦”同時、有序地安裝操作系統和協作協議。 必須確保多源頭、多協議的數據流能準確、同步地注入,并能在系統啟動時被正確讀取和識別。

三、 解決方案:構建面向“系統聯盟”的智能體檢中心

應對上述挑戰,需要構建一套全新的、能夠理解并驗證“芯片聯盟”整體健康的智能測試與配置體系:

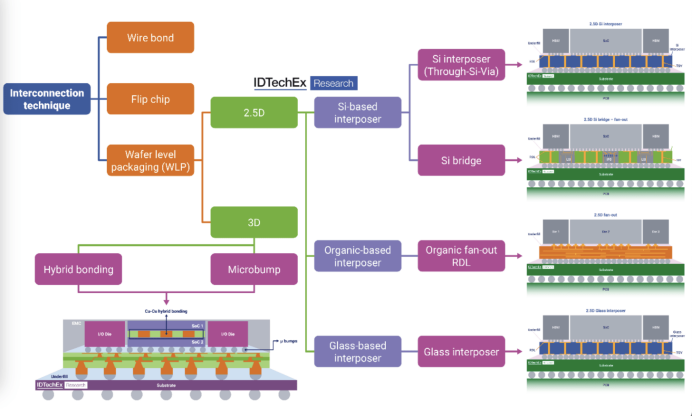

基于硅基板的“內窺鏡”式測試訪問:為了在封裝后仍能對內部互連進行高精度測試,需要借助硅轉接板(Interposer)上預留的專用測試通道或先進的可測試性設計(DFT),如邊界掃描(JTAG)鏈的增強版本,以實現對關鍵節點的可控與可觀。這如同為封裝體安裝了“內窺鏡”。

仿真驅動的系統級測試(SLT)與監控:在接近最終使用環境的板卡上,運行真實的操作系統和應用軟件,進行長時間、高負載的系統級壓力測試。同時,集成先進的功耗與熱監控傳感器,實時采集并關聯分析每個芯粒乃至關鍵模塊的功耗、溫度與性能數據,繪制出系統的“協同工作健康圖譜”。

支持多協議、多任務的協同燒錄引擎:燒錄設備需進化成為一個 “協同配置管理器” 。它需要具備同時處理多種底層通信協議(如PCIe, I2C, SPI, 專用Die-to-Die協議)的能力,并能根據預設的“配置劇本”,有序地向不同芯粒分發數據、驗證回讀,并最終生成一份涵蓋所有成員的、統一的燒錄與配置完成報告。

結語:

Chiplet將半導體的創新從單一的硅片,拓展到了整個封裝系統。這場“超越摩爾”的征程,成功與否不僅取決于設計和封裝的能力,更取決于我們能否在最后關頭,為這個精密的“芯片聯盟”提供一份令人信服的、關于其長期協同作戰能力的“健康證明”。

在您看來,推動Chiplet大規模落地的最大測試障礙是什么?是缺乏統一的可測試性標準,是系統級測試的過高成本,還是協同燒錄的工程復雜度? 歡迎在評論區分享您的洞察與挑戰。當芯片學會“團隊作戰”,我們的檢驗技術,也必須跟上這場進化。在這一前沿領域,與具備系統級驗證視野和深度協議整合能力的伙伴合作,正成為將Chiplet藍圖轉化為可靠產品的關鍵路徑。

審核編輯 黃宇

-

芯片測試

+關注

關注

6文章

161瀏覽量

21093 -

chiplet

+關注

關注

6文章

485瀏覽量

13528

發布評論請先 登錄

探秘半導體“體檢中心”:如何為一顆芯片做靜態參數測試?

Chiplet核心挑戰破解之道:瑞沃微先進封裝技術新思路

Chiplet封裝設計中的信號與電源完整性挑戰

Chiplet,改變了芯片

CMOS 2.0與Chiplet兩種創新技術的區別

臨港汽車軟件聯盟首場技術沙龍來襲!共探“AI如何為OS賦能”|活動預告

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

Chiplet 顛覆芯片創新,一文看懂計算平臺大廠 Arm 的布局藍圖

2.5D集成電路的Chiplet布局設計

解鎖Chiplet潛力:封裝技術是關鍵

超越摩爾:Chiplet時代如何為“芯片聯盟”進行終極體檢?

超越摩爾:Chiplet時代如何為“芯片聯盟”進行終極體檢?

評論