一、引言

隨著工業(yè)自動(dòng)化、機(jī)器人技術(shù)和高端裝備制造業(yè)的快速發(fā)展,伺服控制系統(tǒng)對(duì)性能要求日益提高。傳統(tǒng)基于單片處理器或純DSP的方案已難以滿足現(xiàn)代伺服系統(tǒng)對(duì)高速實(shí)時(shí)性、多軸同步和復(fù)雜算法的需求。DSP+FPGA異構(gòu)架構(gòu)憑借其獨(dú)特的優(yōu)勢(shì),已成為高性能伺服控制模塊的主流解決方案。

二、DSP與FPGA的技術(shù)特性對(duì)比

DSP(數(shù)字信號(hào)處理器)的優(yōu)勢(shì):

強(qiáng)大的算法處理能力:專為數(shù)學(xué)密集型運(yùn)算優(yōu)化,適合坐標(biāo)變換、PID控制、觀測(cè)器算法等

高精度浮點(diǎn)運(yùn)算:現(xiàn)代DSP支持單/雙精度浮點(diǎn)運(yùn)算,滿足高精度控制需求

成熟的開發(fā)環(huán)境:豐富的算法庫和實(shí)時(shí)操作系統(tǒng)支持

FPGA(現(xiàn)場(chǎng)可編程門陣列)的優(yōu)勢(shì):

硬件級(jí)并行處理:可同時(shí)執(zhí)行多個(gè)任務(wù),無軟件調(diào)度延遲

納秒級(jí)響應(yīng)速度:純硬件邏輯實(shí)現(xiàn),滿足最嚴(yán)格的實(shí)時(shí)性要求

高度可定制性:可根據(jù)需求定制硬件外設(shè)和接口

確定性的時(shí)序:消除軟件執(zhí)行時(shí)間的不確定性

JLH221360伺服控制芯片SIP

JLH221360伺服控制芯片SIP

三、DSP+FPGA架構(gòu)在伺服系統(tǒng)中的協(xié)同設(shè)計(jì)

1.DSP側(cè)核心任務(wù):

位置/速度規(guī)劃算法

閉環(huán)控制器(PID、自適應(yīng)控制、滑模控制等)

故障診斷與安全監(jiān)控

上層通信協(xié)議棧(EtherCAT、CANopen等)

2.FPGA側(cè)核心任務(wù):

高速電流環(huán)控制(PWM生成與調(diào)制)

編碼器信號(hào)解碼(增量式、絕對(duì)式、旋轉(zhuǎn)變壓器)

高速ADC數(shù)據(jù)采集與預(yù)處理

保護(hù)電路邏輯(過流、過壓、過熱)

多軸同步時(shí)序控制

3.DSP+FPGA系統(tǒng)級(jí)優(yōu)勢(shì)

實(shí)時(shí)性保證:關(guān)鍵環(huán)路硬件實(shí)現(xiàn),避免操作系統(tǒng)調(diào)度延遲

功能擴(kuò)展性:無需改變硬件即可通過FPGA重構(gòu)增加新功能

可靠性提升:硬件實(shí)現(xiàn)的保護(hù)電路響應(yīng)時(shí)間<1μs

設(shè)計(jì)靈活性:可根據(jù)不同電機(jī)類型(伺服、直線、力矩)定制控制策略

四、關(guān)鍵應(yīng)用設(shè)計(jì)示例

JLH221360控制芯片SIP主要面向伺服機(jī)構(gòu)控制電路小型化應(yīng)用需求,內(nèi)置多種通信接口,用于實(shí)現(xiàn)控制算法及與各個(gè)部件之間的通信,并對(duì)外部各個(gè)部件的控制。

JLH221360控制模塊的設(shè)計(jì)架構(gòu)“DSP+FPGA”

JLH221360控制模塊的設(shè)計(jì)架構(gòu)“DSP+FPGA”

由上圖可知,JLH221360控制芯片主要由DSP核心處理模塊和FPGA接口模塊組成。其中DSP核心處理模塊豐要包括DSP、配套電源、SCI接口、CAN接口等;FPGA接口模塊主要包括程序存儲(chǔ)器、接口轉(zhuǎn)換電路、DAC以及其他外圍電路。各部分主要功能如下:

DSP核心處理模塊主要功能:通過ADC接口對(duì)光電探測(cè)器輸出的信號(hào)進(jìn)行采集,送入DSP完成控制算法的解算;根據(jù)功能時(shí)序要求,通過EMIF、RS422等接口實(shí)時(shí)輸出時(shí)序控制指令,實(shí)現(xiàn)對(duì)外圍電路的控制;通過外部存儲(chǔ)器,實(shí)現(xiàn)數(shù)據(jù)存儲(chǔ)。

FPGA核心處理模塊主要功能:通過D/A轉(zhuǎn)換模塊,將數(shù)字信號(hào)轉(zhuǎn)換為模擬信號(hào)實(shí)現(xiàn)對(duì)激光器輸出光強(qiáng)的控制;通過通信接口及預(yù)留的10端口等實(shí)現(xiàn)與外部電路的通信及電路控制;通過外部程序存儲(chǔ)器,實(shí)現(xiàn)對(duì)控制程序的存儲(chǔ)功能。

五、總結(jié)

DSP+FPGA架構(gòu)在伺服控制模塊中的應(yīng)用,成功解決了高性能伺服系統(tǒng)對(duì)實(shí)時(shí)性、精度和復(fù)雜度的多重需求。通過合理的功能劃分,DSP專注于復(fù)雜算法和上層控制,F(xiàn)PGA處理高速硬件任務(wù),兩者協(xié)同實(shí)現(xiàn)了傳統(tǒng)架構(gòu)難以達(dá)到的性能指標(biāo)。隨著芯片技術(shù)的進(jìn)步和開發(fā)工具的完善,這一架構(gòu)將繼續(xù)推動(dòng)伺服控制技術(shù)向更高性能、更智能化的方向發(fā)展,為高端制造裝備提供核心技術(shù)支持。

這種異構(gòu)計(jì)算架構(gòu)不僅代表了當(dāng)前伺服控制技術(shù)的發(fā)展方向,也為未來智能運(yùn)動(dòng)控制系統(tǒng)的創(chuàng)新提供了可擴(kuò)展的平臺(tái)基礎(chǔ)。

審核編輯 黃宇

-

dsp

+關(guān)注

關(guān)注

561文章

8259瀏覽量

367293 -

FPGA

+關(guān)注

關(guān)注

1662文章

22450瀏覽量

637665 -

伺服控制

+關(guān)注

關(guān)注

5文章

161瀏覽量

24890

發(fā)布評(píng)論請(qǐng)先 登錄

深入剖析ADSP-21990:高性能混合信號(hào)DSP控制器的卓越之選

ADSP - 21992:高性能混合信號(hào) DSP 控制器的深度剖析

XC7Z020-2CLG484I 雙核異構(gòu)架構(gòu) 全能型 SoC

電能質(zhì)量在線監(jiān)測(cè)裝置的核心芯片架構(gòu)對(duì)裝置性能有哪些影響?

AMD UltraScale架構(gòu):高性能FPGA與SoC的技術(shù)剖析

伺服電機(jī)的控制方式簡(jiǎn)述

智能變槳:基于DSP與CPLD協(xié)同處理的高動(dòng)態(tài)飛行器主槳電動(dòng)變槳距伺服控制系統(tǒng)

伺服電機(jī)控制系統(tǒng)的高寬帶電流環(huán)參數(shù)設(shè)計(jì)

FPGA+DSP/ARM架構(gòu)開發(fā)與應(yīng)用

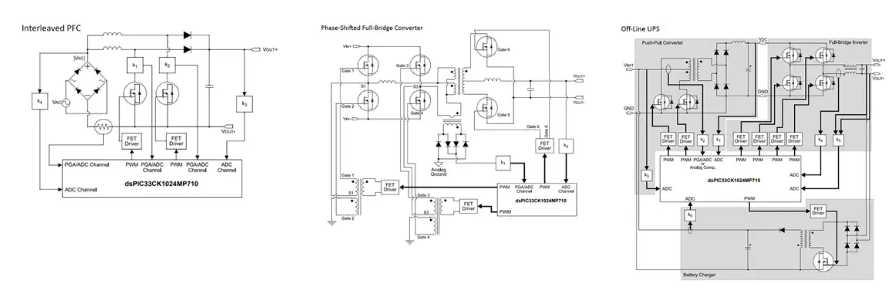

高性能數(shù)字信號(hào)控制器 dsPIC33CK1024MP710 及其在電機(jī)控制與電源系統(tǒng)中的應(yīng)用

MT6825磁編芯片:為伺服電機(jī)控制系統(tǒng)注入全角度測(cè)量新活力

【PZ-ZU15EG-KFB】——ZYNQ UltraScale + 異構(gòu)架構(gòu)下的智能邊緣計(jì)算標(biāo)桿

基于DSP與FPGA異構(gòu)架構(gòu)的高性能伺服控制系統(tǒng)設(shè)計(jì)

基于DSP與FPGA異構(gòu)架構(gòu)的高性能伺服控制系統(tǒng)設(shè)計(jì)

評(píng)論