ADSP - 21992:高性能混合信號 DSP 控制器的深度剖析

在電子工程領域,高性能的 DSP 控制器一直是推動各種應用發展的核心力量。今天,我們就來深入探討一款功能強大的混合信號 DSP 控制器——ADSP - 21992,看看它在工業控制、信號處理等領域能為我們帶來怎樣的驚喜。

文件下載:ADSP-21992.pdf

一、ADSP - 21992 概述

ADSP - 21992 是一款基于 ADSP - 2199x DSP 核心的混合信號 DSP 控制器,適用于各種高性能工業電機控制和信號處理應用。它將高性能 DSP 與嵌入式控制外設的混合信號集成相結合,目標應用涵蓋工業電機驅動、不間斷電源、光網絡控制、數據采集系統、測試與測量系統以及便攜式儀器等。

二、核心架構與性能

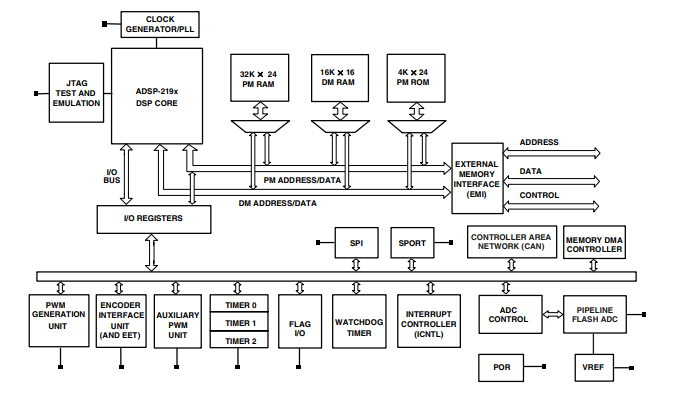

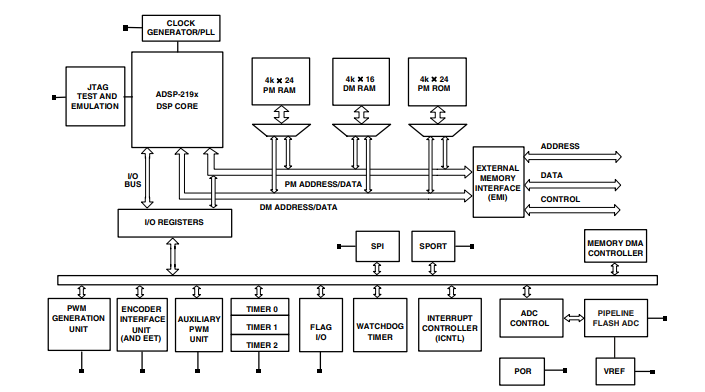

(一)DSP 核心架構

- 指令周期與性能:該控制器擁有出色的指令周期時間,內部指令周期時間可達 6.25 ns,能實現高達 160 MIPS 的持續性能。不同的時鐘頻率對應不同的指令周期時間,如 150 MIPS 持續性能時為 6.67 ns,100 MIPS 持續性能時為 10.0 ns。

- 代碼兼容性:與 ADSP - 218x 家族代碼兼容,采用易于使用的代數語法,方便工程師進行開發。

- 指令執行與內存空間:單周期指令執行,擁有高達 1M 字的可尋址內存空間,地址寬度為 24 位。其雙用途程序內存可同時用于指令和數據存儲,全透明指令緩存允許每個指令周期進行雙操作數提取。

- 計算單元與并行執行:具備獨立的 ALU、乘法器/累加器和桶形移位器計算單元,帶有雙 40 位累加器。支持單周期上下文切換,能夠并行執行計算和內存指令,流水線架構可在高達 160 MIPS 的速度下高效執行代碼。

(二)時鐘與指令集

- 時鐘生成:時鐘生成模塊包含時鐘控制邏輯,用戶可選擇和更改主時鐘頻率。該模塊生成兩個輸出時鐘,即 DSP 核心時鐘 CCLK 和外設時鐘 HCLK。CCLK 最高可達 160 MHz,HCLK 可等于 CCLK 或 CCLK/2,最高可達 80 MHz。

- 指令集特點:指令集提供靈活的數據移動和多功能指令,每個單字指令可在單個處理器周期內執行。匯編語言采用代數語法,便于編碼和閱讀,同時有一套完整的開發工具支持程序開發。

三、內存架構

(一)內部內存

ADSP - 21992 提供 48K 字的片上 SRAM 內存,分為三個塊:兩個 16K × 24 位塊(塊 0 和塊 1)和一個 16K × 16 位塊(塊 2),此外還有一個 4K × 24 位的程序內存引導 ROM。其統一的程序和數據內存空間由 16M 個位置組成,可通過兩個 24 位地址總線(PMA 和 DMA 總線)訪問。

(二)外部內存

該控制器支持多種外部內存空間,包括外部內存空間(MS3 - 0 引腳)、I/O 內存空間(IOMS 引腳)和引導內存空間(BMS 引腳)。每個外部內存空間都有單獨的控制寄存器,可配置獨特的訪問參數。

四、外設架構

(一)通信接口

- SPI 端口:基于 SPI 標準,提供通用可配置的串行端口接口功能,支持主或從操作,數據速率可達 HCLK/4,具備 DMA 能力和專用中斷。

- SPORT 端口:集成完整的同步串行端口,支持雙向通信、雙緩沖、多種時鐘模式、可變字長、硬件壓縮擴展、直接內存訪問等功能,還具備多通道能力和 UART 軟件仿真功能。

- CAN 模塊:符合 CAN V2.0B 標準,支持標準(11 位)和擴展(29 位)標識符,數據速率可達 1 Mbps 及以上,擁有 16 個可配置郵箱和數據過濾功能。

(二)模擬與數字轉換

- ADC 系統:包含一個快速、高精度、多輸入的模數轉換系統,具有 8 個專用模擬輸入和雙通道同時采樣能力。最高采樣率可達 20 MSPS,輸入電壓范圍為 2.0 V 峰 - 峰,支持內部或外部電壓參考。

- 電壓參考:片上集成帶隙參考,可提供精確的 1.0 V 輸出,也可配置為使用外部參考。

(三)PWM 與編碼器接口

- PWM 生成單元:3 相 16 位中心 PWM 生成單元,可編程脈沖寬度,分辨率可達 12.5 ns,支持單/雙更新模式、可編程死區時間和開關頻率等。

- 輔助 PWM 生成單元:2 通道 16 位輔助 PWM 輸出單元,可編程頻率和占空比,支持獨立或偏移操作模式。

- 編碼器接口單元:強大的編碼器接口塊,支持高達 53 MHz 的正交速率,具備可編程濾波、32 位編碼器計數器等功能。

(四)其他外設

還包含 16 個通用標志 I/O 引腳、3 個可編程 32 位間隔定時器、看門狗定時器、中斷控制器和集成的上電復位(POR)電路等。

五、低功耗操作

ADSP - 21992 具有四種低功耗選項,包括空閑模式、掉電核心模式、掉電核心/外設模式和掉電所有模式。通過執行 IDLE 指令并配置 PLLCTL 寄存器中的相關位,可選擇不同的低功耗模式,以顯著降低設備在待機條件下的功耗。

六、開發與設計要點

(一)開發工具

該控制器得到了一套完整的 CROSSCORE? 軟件和硬件開發工具的支持,包括 Analog Devices 仿真器和 VisualDSP++? 開發環境。這些工具提供了從編程到調試的全方位支持,有助于提高開發效率。

(二)設計兼容板

在設計與仿真器兼容的 DSP 板時,需要注意目標板應包含連接 DSP JTAG 端口到仿真器的接口。具體的設計問題可參考 Analog Devices 網站上的 EE - 68: JTAG Emulation Technical Reference。

七、總結

ADSP - 21992 以其強大的核心架構、豐富的外設功能和靈活的低功耗操作模式,為工業電機控制和信號處理等領域提供了一個高性能、高集成度的解決方案。作為電子工程師,我們在使用這款控制器時,要充分了解其特性和參數,合理利用其功能,以實現更高效、更穩定的系統設計。大家在實際應用中遇到過哪些關于 ADSP - 21992 的問題呢?歡迎在評論區交流分享。

-

工業控制

+關注

關注

38文章

1671瀏覽量

91757

發布評論請先 登錄

ADSP - BF531/ADSP - BF532/ADSP - BF533:高性能嵌入式處理器的深度剖析

高性能音頻處理利器:ADSP - 21477/ADSP - 21478/ADSP - 21479處理器深度解析

ADSP-21560/21561/21564/21568:高性能SHARC+單核心DSP的深度剖析

深入剖析ADSP - 2189M:高性能數字信號處理的理想選擇

深度剖析LTC3788:高性能2相雙同步升壓控制器

LTC3784:高性能多相同步升壓控制器的深度剖析

MSP430x43x/44x系列混合信號微控制器深度剖析

LTC7801:高性能同步降壓DC/DC控制器的深度剖析

深度剖析 LTC7803 - 3.3:高性能同步降壓控制器的卓越之選

SLG47525/28:高性能可編程混合信號矩陣的深度剖析

ADSP-21992高性能混合型信號DSP,160MHz,32K字程序存儲器RAM,16K字數據存儲器RAM技術手冊

ADSP - 21992:高性能混合信號 DSP 控制器的深度剖析

ADSP - 21992:高性能混合信號 DSP 控制器的深度剖析

評論