由上海 EDA/IP 創新中心、張江高科與上海市集成電路行業協會聯合主辦,上海市經濟和信息化委員會指導的《人工智能在 EDA 領域的應用與探討》成功舉辦。會上,芯華章科技副總裁劉軍系統的分享了“AI+EDA”如何重塑驗證效率以及客戶應用成果。

驗證自動化應該是每個驗證工程師的終極夢想,這不僅意味著效率的提升,更代表著可以將工程師從重復繁重的手工任務中解放出來,將創造力聚焦于更具挑戰性的設計優化難題。

但現實有著重重挑戰:

編寫定向測試用例耗時漫長,激勵分布易偏置導致覆蓋率難以提升

SVA語法復雜令人生畏,手工編寫易錯且效率低下

面對海量回歸失敗,定位根因如同大海撈針

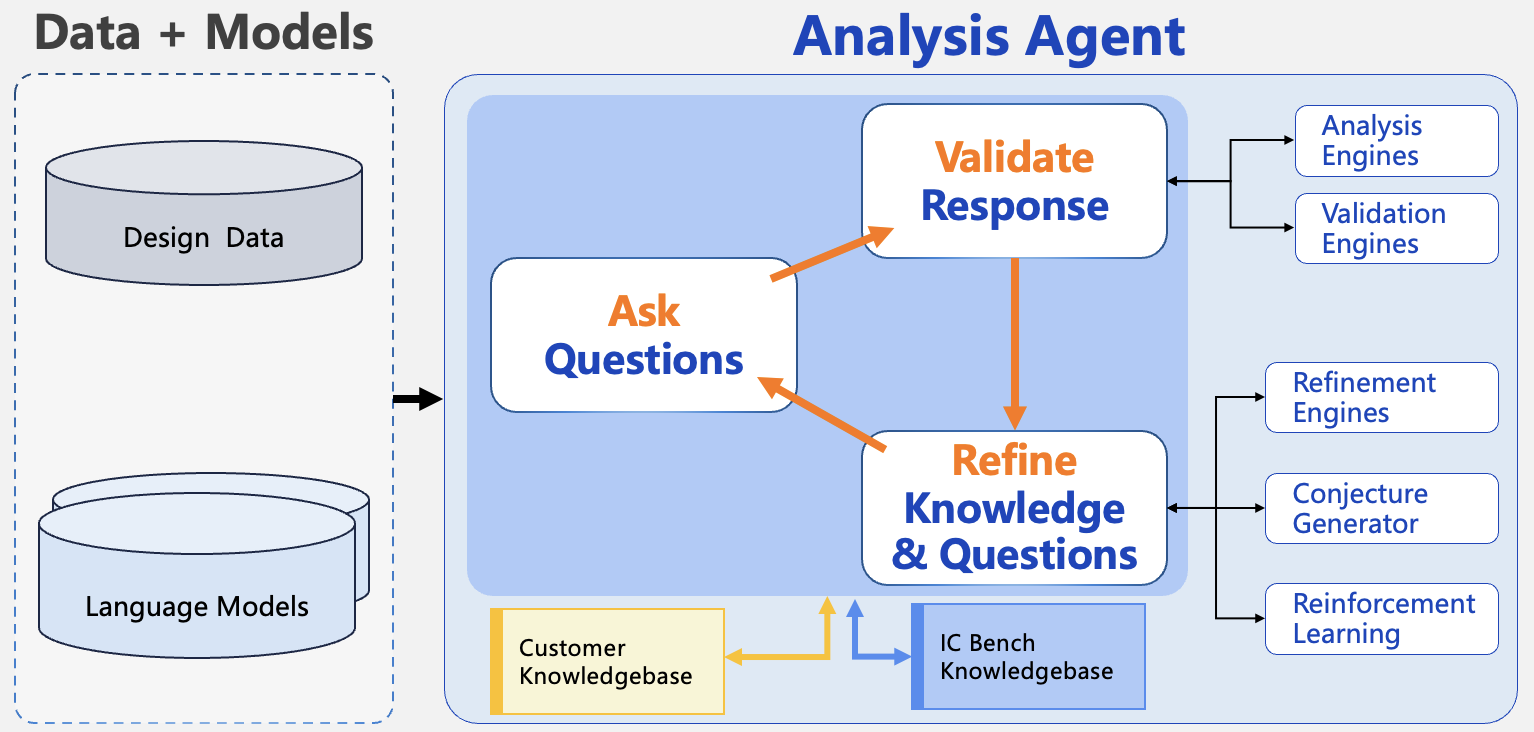

針對這些驗證中的“硬骨頭”問題,芯華章以 AI 技術為核心驅動力,構建系統性解決方案,直擊驗證中的瓶頸問題。

加速驗證收斂:讓測試生成更智能高效

針對仿真驗證中測試用例生成低效、激勵偏置導致覆蓋率難提升的痛點,芯華章引入機器學習技術,用已生成用例引導隨機約束求解器動態優化激勵分布。

這種 AI 引導模式將工程師驗證經驗轉化為可迭代算法模型,大幅提升測試生成的針對性與高效性,加速功能覆蓋率收斂,讓工程師擺脫重復試錯的激勵/約束編寫工作,聚焦更高層次的驗證策略制定。

Auto Debug:快速定位回歸失敗根源

面對回歸測試中數千個仿真失敗用例的排查難題,AI 自動故障聚類(Failure Binning)將海量失敗歸納為少數核心根因。

通過與代碼版本管理工具深度聯動,系統可自動關聯失敗用例與特定代碼變更,精準定位問題代碼行或模塊,將調試周期從數天縮短至小時級,顯著提升驗證迭代效率與研發信心。

AI賦能形式化驗證

除了優化仿真驗證的核心流程,針對仿真難以覆蓋的復雜邊界場景與完備性驗證需求,芯華章在形式化驗證領域實現了更大幅度的技術革新。

硬件模型檢測技術作為形式化驗證的核心分支,是確保設計關鍵核心控制邏輯完備驗證的重要手段,但面對復雜的設計和眾多的屬性與求解引擎,如何最優調度資源成為巨大挑戰。

芯華章通過 AI 技術實現多項關鍵突破,全面激活形式化驗證的高效性,增強新用戶導入形式化驗證方法學進行驗證提效的信心。

最佳引擎選擇

通過對設計、屬性提取數千個特征參數,進行離線模型訓練與在線實時預測,為每個待驗證屬性動態匹配最優底層求解引擎,顯著縮短求解時間;

屬性求解排序與分組

通過模型預測屬性求解難度,優先攻克簡單問題,最大化有限時間內的驗證產出;同時將相似屬性分組求解,共享求解過程中的 “引理” 知識,進一步提升整體效率;

驗證結果預測與求解導向

模型可預測某個屬性成功或失敗的概率,據此智能選擇求解引擎策略,避免盲目進行無效嘗試,浪費計算資源;

資源需求預估

根據用戶提供的 CPU、內存等服務器配置,預測驗證任務能否在給定資源下完成,從而提供科學的資源規劃建議,避免算力浪費。

這些智能化手段,使得形式化驗證模型檢測技術煥發出新的速度和靈活性。

從 “人工苦旅” 走向 “智能生成”

SVA 編寫是硬件模型檢測中不可回避的核心難題 —— 作為形式化屬性驗證(FPV)的關鍵載體,SVA 對確保設計正確性至關重要,但復雜時序邏輯的手工編寫耗時耗力,且易因邊界條件遺漏引發驗證漏洞。

針對這一痛點,芯華章聯合中興微電子,研發基于大語言模型(LLM)的SVA生成并引入工業級創新評估系統SVAEval。用戶只需輸入自然語言描述的設計意圖,系統便能調用大語言模型智能體,自動生成符合語法的SVA。

隨后,該系統會進行三層自動化校驗:語法正確性、功能正確性以及質量評估。我們創新地采用了形式化驗證與仿真比對相結合的方式,確保生成的SVA與黃金參考等價。該框架通過迭代式提示優化和指標評估,顯著提升了由大型語言模型生成的 SVA 的質量。

SVA智能小助手已成功在中興微電子落地并投入日常使用。實驗數據顯示,pass@5較基線提升59%,復雜斷言開發效率提升40%以上,有效減輕了工程師編寫SVA的負擔,提升了驗證代碼的產出效率與質量。

未來,芯華章將持續探索“AI+EDA”創新路徑,與客戶共同研發適配其技術路線的驗證方案,為客戶提供更加高效、可靠的驗證解決方案,實現從需求響應到價值共創的跨越。

-

eda

+關注

關注

72文章

3079瀏覽量

181678 -

AI

+關注

關注

90文章

38414瀏覽量

297708 -

芯華章

+關注

關注

0文章

194瀏覽量

11929

原文標題:AI+EDA如何重塑驗證效率

文章出處:【微信號:X-EPIC,微信公眾號:芯華章科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

AI重塑EDA,3D-IC成關鍵戰場:Cadence的洞察與應變

伴芯科技重磅發布DVcrew與PDcrew兩大創新產品,以AI智能體重構EDA

伴芯科技重磅亮相!AI智能體重構EDA,邁向芯片自主設計閉環

西門子EDA AI System驅動芯片設計新紀元

智驅設計 芯構智能(AI+EDA For AI) 2025芯和半導體用戶大會隆重舉行

智驅設計 芯構智能(AI+EDA For AI) 2025芯和半導體用戶大會隆重舉行

國產EDA又火了,那EDA+AI呢?國產EDA與AI融合發展現狀探析

EDA+AI For AI,芯和半導體邀請您參加2025用戶大會

EDA是什么,有哪些方面

芯華章攜手EDA國創中心推出數字芯片驗證大模型ChatDV

Cadence Conformal AI Studio助力前端驗證設計

IC驗證云平臺優勢明顯,這家本土EDA公司如何御風先行?

AI+EDA如何重塑驗證效率

AI+EDA如何重塑驗證效率

評論