簡介

國務(wù)院最新發(fā)布《關(guān)于深入實施“人工智能 +” 行動的意見》,明確 AI 將推動千行百業(yè)智能化升級,半導(dǎo)體行業(yè)需加速算力、存儲、網(wǎng)絡(luò)、電源等核心要素進階 ——Chiplet 先進封裝成算力增長關(guān)鍵,AI 數(shù)據(jù)中心設(shè)計為復(fù)雜系統(tǒng)級工程,EDA 工具需從單芯片設(shè)計轉(zhuǎn)向封裝級、系統(tǒng)級協(xié)同優(yōu)化,推動設(shè)計范式從 DTCO 升級至 STCO。

國際EDA 三大家通過收購布局系統(tǒng)分析 EDA 與多物理場仿真能力;國產(chǎn) EDA 中,芯和半導(dǎo)體在 Chiplet 封裝設(shè)計、節(jié)點級 PCB 仿真、集群級 STCO 集成系統(tǒng)領(lǐng)域積累深厚,具備 “從芯片到系統(tǒng)全棧 EDA” 先發(fā)優(yōu)勢。

在AI 賦能重構(gòu) EDA 領(lǐng)域,國際 EDA 企業(yè)加緊將 AI 融入設(shè)計流程;芯和半導(dǎo)體等國產(chǎn)企業(yè)也將國產(chǎn) AI 大模型融入開發(fā),推出 XAI 多智能體平臺,推動設(shè)計范式從 “規(guī)則驅(qū)動” 向 “數(shù)據(jù)驅(qū)動” 升級。

2025 芯和半導(dǎo)體用戶大會將于 10 月 31 日在上海舉辦,以 “智驅(qū)設(shè)計,芯構(gòu)智能 (AI+EDA for AI)” 為主題,聚焦 AI 大模型與 EDA 深度融合,將發(fā)布 Xpeedic EDA2025 軟件集,匯聚多領(lǐng)域用戶與合作伙伴分享技術(shù)突破,助力中國集成電路產(chǎn)業(yè)發(fā)展。

正文

國務(wù)院最新發(fā)布的《關(guān)于深入實施“人工智能 +” 行動的意見》明確指出,AI 作為第四次工業(yè)革命核心驅(qū)動力,將推動千行百業(yè)實現(xiàn)自動化智能化升級,到 2027 年智能終端和智能體普及率超 70%。

半導(dǎo)體行業(yè)首當(dāng)其沖,算力、存儲、網(wǎng)絡(luò)、電源等核心要素必須加速進階。一方面,AI 大模型訓(xùn)練與推理需求爆發(fā),面對摩爾定律放緩、單芯片工藝微縮性能提升有限的現(xiàn)狀,Chiplet 先進封裝成為延續(xù)算力增長的關(guān)鍵,EDA 工具需從單芯片設(shè)計擴展至封裝級協(xié)同優(yōu)化,實現(xiàn)跨維度系統(tǒng)設(shè)計。另一方面,AI 數(shù)據(jù)中心設(shè)計已成為覆蓋異構(gòu)算力、高速互連、供電冷卻的復(fù)雜系統(tǒng)級工程,EDA 急需通過技術(shù)重構(gòu)與生態(tài)整合,推動設(shè)計范式從 DTCO 升級至貫穿全鏈路的 STCO,實現(xiàn)從芯片到系統(tǒng)的能力躍遷。

EDA For AI:系統(tǒng)級攻堅成產(chǎn)業(yè)破局關(guān)鍵

過去兩年,AI 硬件的爆炸式發(fā)展推動系統(tǒng)攻堅成為大勢所趨。芯片系統(tǒng)化層面,三維芯片 Chiplet 先進封裝與異構(gòu)集成成為延續(xù)算力增長的核心路徑,已被英偉達、AMD、博通等 AI 芯片巨頭廣泛采用;系統(tǒng)規(guī)模化層面,以英偉達 NVL72、華為昇騰 384 機柜級超節(jié)點系統(tǒng)為代表的智算系統(tǒng),正通過硅光等更高速互連技術(shù)不斷突破 Scale-Up 和 Scale-Out 的性能邊界。

這一融合趨勢成為后摩爾時代突破先進工藝瓶頸、提升算力的重要方向,也帶來了全新挑戰(zhàn)。Chiplet 集成系統(tǒng)面臨高密互連、高速串?dāng)_、電 - 熱 - 力耦合及反復(fù)優(yōu)化迭代等難題;AI 超節(jié)點硬件系統(tǒng)的萬卡級互連拓撲優(yōu)化、高壓直供電源網(wǎng)絡(luò)設(shè)計、液冷系統(tǒng)與芯片熱耦合仿真等復(fù)雜度,遠超傳統(tǒng)單芯片設(shè)計能力范疇。

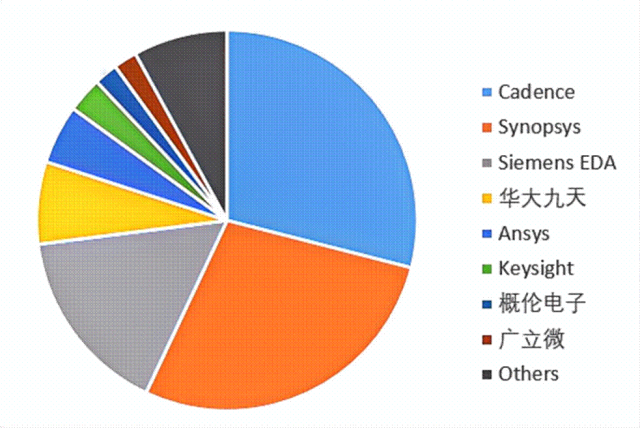

面對挑戰(zhàn),EDA 三大家在傳統(tǒng)芯片 EDA 業(yè)務(wù)基礎(chǔ)上,積極布局多物理場仿真分析能力與系統(tǒng)分析 EDA,推動產(chǎn)業(yè)貫通融合。新思科技收購 Ansys、Cadence 收購 BETA CAE Systems 及 Invecas、Siemens EDA 收購 Altair,均是加速向系統(tǒng)設(shè)計轉(zhuǎn)型的重要舉措,旨在構(gòu)建 “芯片到系統(tǒng)的完整設(shè)計鏈路”,應(yīng)對 AI 硬件設(shè)施設(shè)計挑戰(zhàn)。

國產(chǎn)EDA 企業(yè)中,芯和半導(dǎo)體憑借在 Chiplet、封裝、系統(tǒng)領(lǐng)域的長期深耕,以及多物理場仿真分析的雄厚積累,在拉通 “從芯片到系統(tǒng)全棧 EDA” 方面具備先發(fā)優(yōu)勢。其 AI 芯片級 Chiplet 先進封裝設(shè)計平臺剛斬獲中國工業(yè)博覽會上的 CIIF 大獎;針對 AI 節(jié)點級 Scale-Up 需求,封裝 PCB 設(shè)計仿真全流程十年間已服務(wù)國內(nèi)超百家高速系統(tǒng)設(shè)計用戶;在 AI 集群級 Scale-Out 設(shè)計領(lǐng)域,芯和 STCO 集成系統(tǒng)仿真平臺融入散熱、電源分配網(wǎng)絡(luò)等多物理分析場景,保障算力從芯片到集群持續(xù)穩(wěn)定輸出。

AI+EDA:技術(shù)重構(gòu)開啟產(chǎn)業(yè)新范式

AI 不僅推動半導(dǎo)體產(chǎn)業(yè)深刻變革,更賦能并重構(gòu) EDA 領(lǐng)域。傳統(tǒng)以規(guī)則驅(qū)動和工藝約束為核心的設(shè)計方法,已無法滿足多芯片協(xié)同、系統(tǒng)級優(yōu)化和多物理場耦合帶來的挑戰(zhàn)。AI 技術(shù)的引入,為 EDA 開辟了全新發(fā)展路徑 —— 從電路設(shè)計到封裝布局,從信號通道優(yōu)化到系統(tǒng)級電 - 熱 - 應(yīng)力協(xié)同仿真,AI 通過強大的學(xué)習(xí)與推理能力,大幅提升設(shè)計效率、縮短驗證周期。

國際EDA 企業(yè)已加緊推進 AI 與 EDA 設(shè)計流程的融合。Cadence 與英偉達深度合作,將 Blackwell 架構(gòu)集成到 EDA 工程與科學(xué)解決方案中,顯著提升芯片設(shè)計和仿真效率;新思科技推出 DSO.ai,通過強化學(xué)習(xí)自動探索設(shè)計空間,優(yōu)化 PPA(功耗、性能、面積),在 Intel 18A 和臺積電 N2/A16 工藝中實現(xiàn) 10%~15% 的能效提升。AI 技術(shù)迭代速度飛快,國內(nèi) EDA 企業(yè)若不積極布局,將很快形成代際劣勢。

值得欣慰的是,芯和半導(dǎo)體等國產(chǎn)EDA 企業(yè)已率先行動,將 DeepSeek 等國產(chǎn) AI 大模型融入開發(fā)流程,踐行仿真驅(qū)動設(shè)計理念。其自主研發(fā)的 XAI 多智能體平臺已貫穿芯片到系統(tǒng)的全棧 EDA,從建模、設(shè)計、仿真、優(yōu)化等多方面賦能,推動 EDA 從傳統(tǒng) “規(guī)則驅(qū)動設(shè)計” 演進為 “數(shù)據(jù)驅(qū)動設(shè)計”,大幅提升設(shè)計效率。

2025 芯和半導(dǎo)體用戶大會:共探 AI+EDA forAI融合創(chuàng)新

耳聽為虛,眼見為實。2025 芯和半導(dǎo)體用戶大會即將揭開國產(chǎn) EDA 與 AI 融合的更多面紗。

本次大會將于10 月 31 日在上海舉辦,以 “智驅(qū)設(shè)計,芯構(gòu)智能 (AI+EDA for AI)” 為主題,聚焦 AI 大模型與 EDA 深度融合,賦能人工智能時代 “從芯片到系統(tǒng)” 的 STCO 協(xié)同設(shè)計與生態(tài)共建。大會設(shè)置主旨演講和技術(shù)分論壇兩大環(huán)節(jié),涵蓋算力(AI HPC)、互連(5G 射頻與網(wǎng)絡(luò)互連)兩條主線,并將正式發(fā)布融合 AI 智慧的 Xpeedic EDA2025 軟件集。

屆時,來自AI 人工智能和數(shù)據(jù)中心、5G 射頻、網(wǎng)絡(luò)互連、汽車電子等領(lǐng)域的芯和用戶,以及科研院所、生態(tài)圈合作伙伴將齊聚一堂,覆蓋 Fabless、IP、OSAT 到 Foundry 全產(chǎn)業(yè)鏈,共同分享 Chiplet 先進封裝、存儲、射頻、電源、數(shù)據(jù)中心、智能終端等關(guān)鍵領(lǐng)域的技術(shù)突破與成功實踐。

AI 大時代剛剛拉開帷幕,需要每一位工程師參與其中,共同探討 “AI+EDA” 融合創(chuàng)新路徑,助力中國集成電路產(chǎn)業(yè)攻克關(guān)鍵技術(shù)、構(gòu)建完善生態(tài),為推動高水平科技自立自強注入 AI 新動能!

-

eda

+關(guān)注

關(guān)注

72文章

3119瀏覽量

183330 -

AI

+關(guān)注

關(guān)注

91文章

40403瀏覽量

301973 -

chiplet

+關(guān)注

關(guān)注

6文章

496瀏覽量

13627 -

芯和半導(dǎo)體

+關(guān)注

關(guān)注

0文章

125瀏覽量

32244 -

先進封裝

+關(guān)注

關(guān)注

2文章

549瀏覽量

1045

發(fā)布評論請先 登錄

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】跟著本書來看國內(nèi)波詭云譎的EDA發(fā)展之路

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】跟著本書來看EDA的奧秘和EDA發(fā)展

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】--中國EDA的發(fā)展

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】+ 芯片“卡脖子”引發(fā)對EDA的重視

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】+ 全書概覽

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】--EDA了解與發(fā)展概況

【「芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望」閱讀體驗】--全書概覽

70%營收砸向研發(fā)!這家EDA企業(yè)破局高密度存儲EDA、數(shù)字EDA

英諾達ELPC榮登國產(chǎn)EDA“口碑榜”

【書籍評測活動NO.69】解碼中國”芯“基石,洞見EDA突圍路《芯片設(shè)計基石——EDA產(chǎn)業(yè)全景與未來展望》

伴芯科技重磅亮相!AI智能體重構(gòu)EDA,邁向芯片自主設(shè)計閉環(huán)

EDA+AI For AI,芯和半導(dǎo)體邀請您參加2025用戶大會

EDA是什么,有哪些方面

九霄智能國產(chǎn)EDA工具的突圍之路

芯華章以AI+EDA重塑芯片驗證效率

國產(chǎn)EDA又火了,那EDA+AI呢?國產(chǎn)EDA與AI融合發(fā)展現(xiàn)狀探析

國產(chǎn)EDA又火了,那EDA+AI呢?國產(chǎn)EDA與AI融合發(fā)展現(xiàn)狀探析

評論