CDCE949和CDCEL949是基于模塊化PLL的低成本、高性能、可編程時鐘合成器、乘法器和分頻器。這些器件從單個輸入頻率生成多達(dá)九個輸出時鐘。每個輸出均可在系統(tǒng)內(nèi)編程,適用于高達(dá) 230MHz 的任何時鐘頻率,使用多達(dá)四個獨(dú)立的可配置 PLL。

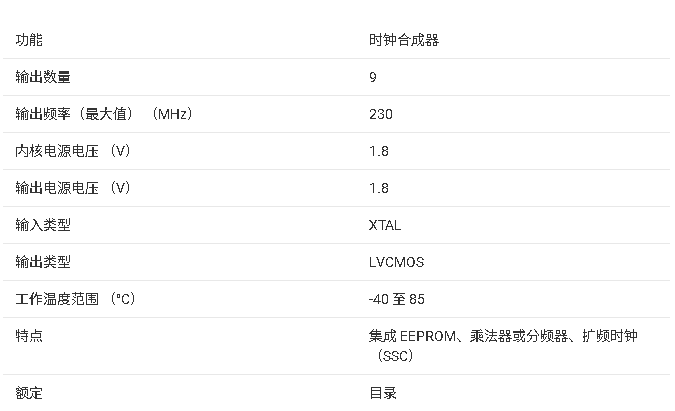

CDCEx949具有獨(dú)立的輸出電源引腳(VDDOUT):CDCEL949為1.8V,CDCE949為2.5V至3.3V。

*附件:cdce949.pdf

輸入接受外部晶體或LVCMOS時鐘信號。如果使用外部晶體,片內(nèi)負(fù)載電容器足以滿足大多數(shù)應(yīng)用。負(fù)載電容器的值可在 0pF 至 20pF 之間進(jìn)行編程。此外,片上VCXO是可選的,允許輸出頻率與外部控制信號(即PWM信號)同步。

較深的M/N分頻比允許從參考輸入頻率(例如27MHz)生成0ppm的音頻或視頻、網(wǎng)絡(luò)(WLAN、藍(lán)牙、以太網(wǎng)、GPS)或接口(USB、IEEE1394、記憶棒)時鐘。

所有 PLL 都支持?jǐn)U頻時鐘 (SSC)。SSC 可以是中心擴(kuò)展或向下擴(kuò)展時鐘。這是減少電磁干擾 (EMI) 的常用技術(shù)。

根據(jù)PLL頻率和分頻器設(shè)置,自動調(diào)整內(nèi)部環(huán)路濾波器組件以實(shí)現(xiàn)高穩(wěn)定性,并優(yōu)化每個PLL的抖動傳遞特性。

該器件支持非易失性EEPROM編程,可根據(jù)應(yīng)用輕松定制器件。CDCEx949 預(yù)設(shè)為出廠默認(rèn)配置。該器件可以在 PCB 組裝之前重新編程為不同的應(yīng)用配置,或通過系統(tǒng)內(nèi)編程重新編程。所有器件設(shè)置都可通過SDA和SCL總線(2線串行接口)進(jìn)行編程。

特性

- 可編程時鐘發(fā)生器系列成員

- CDCEx913:1 個 PLL,3 個輸出

- CDCEx925:2 個 PLL,5 個輸出

- CDCEx937:3 個 PLL,7 個輸出

- CDCEx949:4 個 PLL,9 個輸出

- 系統(tǒng)內(nèi)可編程性和EEPROM

- 串行可編程易失性寄存器

- 用于存儲客戶設(shè)置的非易失性EEPROM

- 靈活的輸入時鐘概念

- 外部晶體:8MHz至32MHz

- 片內(nèi)VCXO拉動范圍:±150ppm

- 單端LVCMOS,頻率高達(dá)160MHz

- 自由選擇高達(dá) 230MHz 的輸出頻率

- 低噪聲PLL內(nèi)核

- 集成 PLL 回路濾波器組件

- 低周期抖動:60ps(典型值)

- 獨(dú)立的輸出電源引腳

- CDCE949:3.3V 和 2.5V

- CDCEL949:1.8V

- 靈活的時鐘驅(qū)動器

- 1.8V器件核心電源

- 寬溫度范圍:–40°C 至 85°C

- 采用 TSSOP 封裝

- 用于輕松進(jìn)行 PLL 設(shè)計(jì)和編程的開發(fā)和編程套件 (TI Pro-Clock?)

參數(shù)

方框圖

?1. 產(chǎn)品概述?

- ?型號?:CDCE949(3.3V/2.5V輸出)與CDCEL949(1.8V輸出),均為可編程低功耗LVCMOS時鐘發(fā)生器,支持?jǐn)U頻時鐘(SSC)以降低EMI。

- ?核心特性?:

- 4個獨(dú)立PLL,支持9路輸出,頻率最高230MHz。

- 集成SSC功能(中心/下擴(kuò)頻,調(diào)制范圍±0.25%至±2%)。

- 支持晶體(8MHz-32MHz)或LVCMOS輸入(最高160MHz)。

- 低周期抖動(典型值60ps),內(nèi)置PLL環(huán)路濾波器。

- 非易失性EEPROM存儲用戶配置,支持在線編程(SDA/SCL接口)。

?2. 關(guān)鍵功能模塊?

- ?PLL架構(gòu)?:

- 每個PLL可獨(dú)立配置分頻/倍頻參數(shù)(N/M值),支持0ppm音頻/視頻時鐘生成。

- 自動調(diào)整內(nèi)部濾波器以優(yōu)化抖動性能。

- ?控制接口?:

- 3個可編程控制引腳(S0/S1/S2),支持頻率切換、SSC模式選擇、輸出使能等功能。

- 默認(rèn)SDA/SCL接口可重配置為控制引腳。

- ?輸出配置?:

- 每路輸出可單獨(dú)設(shè)置分頻值(Pdiv,1-127)、電源電壓(VDDOUT)及狀態(tài)(使能/三態(tài)/低電平)。

?3. 應(yīng)用場景?

- ?典型應(yīng)用?:數(shù)字電視(D-TV)、機(jī)頂盒(STB)、DVD播放器/錄像機(jī)、打印機(jī)、網(wǎng)絡(luò)設(shè)備(WLAN/藍(lán)牙/以太網(wǎng))及接口(USB/IEEE1394)。

- ?EMI優(yōu)化?:通過SSC技術(shù)降低時鐘諧波輻射,適用于高密度PCB設(shè)計(jì)。

?4. 電氣特性?

- ?工作范圍?:1.8V核心供電,溫度-40°C至85°C。

- ?功耗?:

- 靜態(tài)電流典型值38mA(所有PLL開啟,27MHz輸入)。

- 輸出驅(qū)動電流依電壓不同(3.3V: ±12mA, 1.8V: ±8mA)。

- ?抖動性能?:周期抖動70-180ps(取決于配置與負(fù)載)。

?5. 封裝與開發(fā)支持?

- ?封裝?:24引腳TSSOP(7.8mm×6.4mm)。

- ?開發(fā)工具?:TI Pro-Clock?軟件簡化PLL配置與編程。

?6. 設(shè)計(jì)注意事項(xiàng)?

- ?布局建議?:晶體需靠近芯片,對稱布線;避免底層走線以減少寄生電容。

- ?電源管理?:建議VDD先于VDDOUT上電,未用輸出引腳可懸空。

-

可編程

+關(guān)注

關(guān)注

2文章

1325瀏覽量

41480 -

分頻器

+關(guān)注

關(guān)注

43文章

536瀏覽量

53349 -

pll

+關(guān)注

關(guān)注

6文章

981瀏覽量

138156 -

時鐘合成器

+關(guān)注

關(guān)注

0文章

113瀏覽量

8891

發(fā)布評論請先 登錄

按照ClockPro導(dǎo)出的參數(shù)后,配置到CDCE949寄存器后,對應(yīng)的輸出腳無時鐘輸出,為什么?

時鐘發(fā)生器CDCE949.pdf

基于CDCE949的可控頻率源設(shè)計(jì)

CDCE949 時鐘發(fā)生器

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

CDCE925,CDCEL925低功耗LVCMOS時鐘發(fā)生器數(shù)據(jù)表

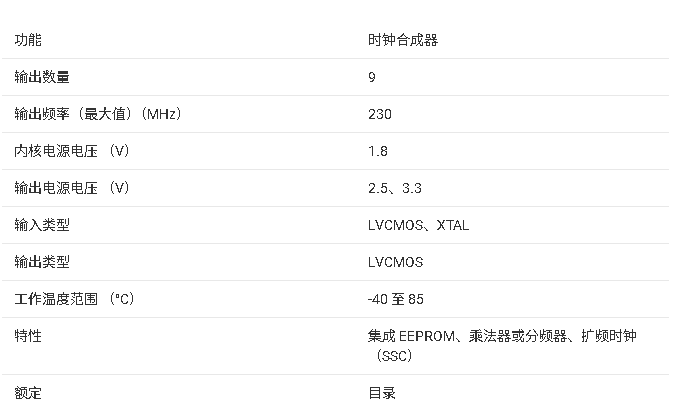

?CDCE949-Q1 可編程時鐘合成器技術(shù)文檔總結(jié)

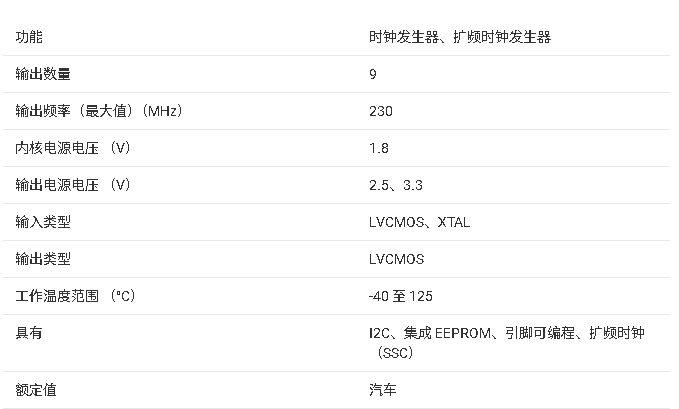

CDCEL949 具有1.8V LVCMOS輸出的可編程4-PLL VCXO時鐘合成器技術(shù)手冊

?CDCE949/CDCEL949 時鐘發(fā)生器芯片技術(shù)文檔總結(jié)

?CDCE949/CDCEL949 時鐘發(fā)生器芯片技術(shù)文檔總結(jié)

評論