深入剖析CDCE949與CDCEL949:高性能可編程時鐘發生器

在電子設備的設計中,時鐘信號的穩定性和靈活性至關重要。CDCE949和CDCEL949作為德州儀器(TI)推出的可編程時鐘發生器,為工程師們提供了強大而靈活的解決方案。本文將深入剖析這兩款器件的特性、應用及設計要點,希望能為電子工程師們在實際設計中提供有益的參考。

文件下載:cdce949.pdf

一、器件概述

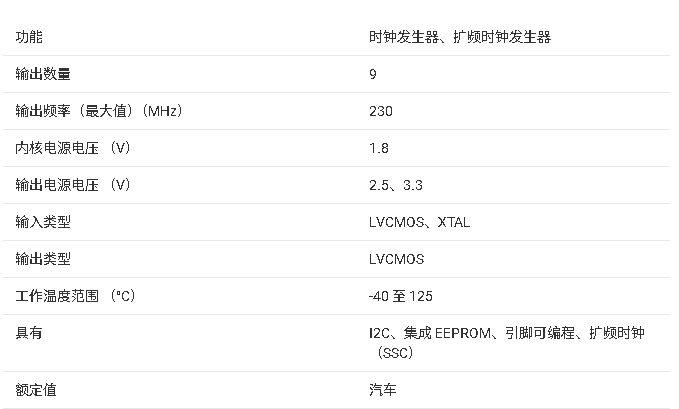

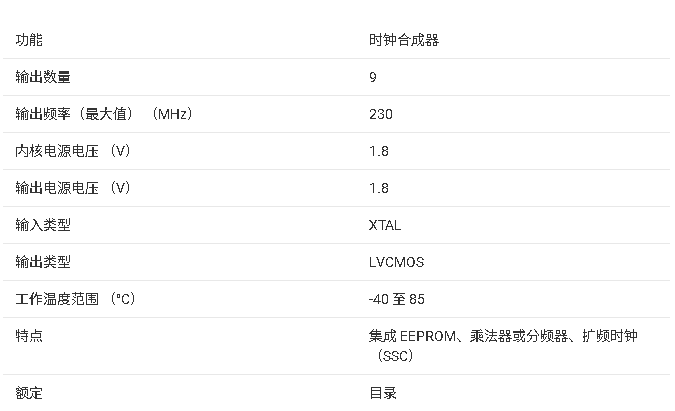

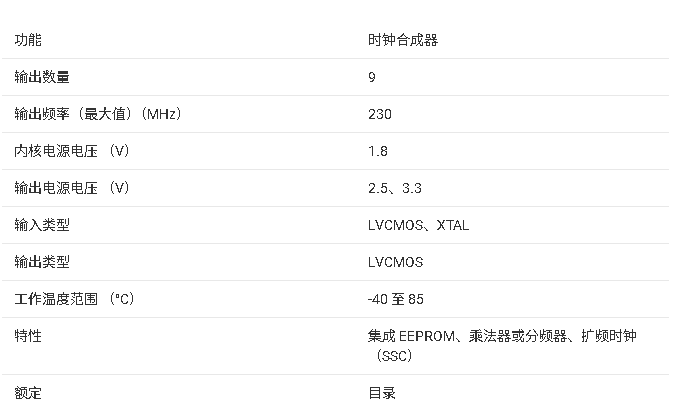

CDCE949和CDCEL949屬于可編程時鐘發生器家族,它們基于模塊化PLL架構,具備低成本、高性能的特點,是可編程的時鐘合成器、乘法器和除法器。這兩款器件能夠從單個輸入頻率生成多達九個輸出時鐘,每個輸出都能在系統內編程,實現最高230MHz的任意時鐘頻率,通過四個獨立可配置的PLL來實現。

(一)產品家族對比

可編程時鐘發生器家族中,不同型號有著不同的PLL數量和輸出數量:

- CDCEx913:1個PLL,3個輸出

- CDCEx925:2個PLL,5個輸出

- CDCEx937:3個PLL,7個輸出

- CDCEx949:4個PLL,9個輸出

(二)關鍵特性

- 輸入靈活性:輸入可接受外部晶體(8MHz - 32MHz)或單端LVCMOS時鐘信號(最高160MHz)。若使用外部晶體,片上負載電容(可編程范圍0pF - 20pF)在大多數應用中已足夠。此外,片上VCXO(壓控晶體振蕩器)可選,可將輸出頻率同步到外部控制信號(如PWM信號),片上VCXO的拉頻范圍為±150ppm。

- 低噪聲PLL核心:PLL環路濾波器組件集成,具有低周期抖動(典型值60ps),能提供穩定的時鐘信號。

- 靈活的輸出配置:輸出頻率可自由選擇,最高達230MHz。CDCE949的輸出電源引腳支持3.3V和2.5V,CDCEL949支持1.8V。

- 可編程控制:具備三個用戶可定義的控制輸入(S0/S1/S2),可用于控制多種操作,如SSC(擴頻時鐘)選擇、頻率切換、輸出使能或電源關閉等。

- SSC支持:所有PLL都支持擴頻時鐘(SSC),可采用中心擴展或向下擴展時鐘,有效降低電磁干擾(EMI)。

- EEPROM編程:支持非易失性EEPROM編程,方便根據應用定制設備。設備預設為工廠默認配置,可在PCB組裝前重新編程,也可通過系統內編程進行修改。

- 寬溫度范圍:能在 -40°C至85°C的寬溫度范圍內工作,適應不同的應用環境。

二、引腳配置與功能

(一)引腳布局

CDCE949和CDCEL949采用24引腳的TSSOP封裝,引腳布局清晰,各引腳功能明確。主要引腳包括:

- 電源引腳:VDD為1.8V設備電源,VDDOUT為輸出電源(CDCE949為3.3V或2.5V,CDCEL949為1.8V)。

- 輸入引腳:Xin/CLK為晶體振蕩器輸入或LVCMOS時鐘輸入(可通過SDA/SCL總線選擇);SCL/S2和SDA/S1在默認配置下為串行時鐘和數據輸入/輸出,也可作為用戶可編程控制輸入;S0為用戶可編程控制輸入;V Ctrl為VCXO控制電壓。

- 輸出引腳:Y1 - Y9為LVCMOS輸出。

(二)引腳功能詳細說明

| PIN | NO. | TYPE | DESCRIPTION |

|---|---|---|---|

| GND | 5, 9, 14, 20 | G | 接地 |

| SCL/S2 | 22 | I | SCL:串行時鐘輸入(默認配置),LVCMOS;內部上拉500kΩ;或S2:用戶可編程控制輸入,LVCMOS輸入,內部上拉500kΩ |

| SDA/S1 | 23 | I/O | SDA:雙向串行數據輸入/輸出(默認配置),LVCMOS;內部上拉500kΩ;或S1:用戶可編程控制輸入,LVCMOS輸入,內部上拉500kΩ |

| S0 | 2 | I | 用戶可編程控制輸入S0,LVCMOS輸入,內部上拉500kΩ |

| V Ctrl | 4 | I | VCXO控制電壓(不使用時留空或上拉) |

| V DD | 3, 13 | P | 1.8V設備電源 |

| V DDOUT | 6, 10, 17 | P | CDCEL949:所有輸出的1.8V電源;CDCE949:所有輸出的3.3V或2.5V電源 |

| Xin/CLK | 1 | I | 晶體振蕩器輸入或LVCMOS時鐘輸入(可通過SDA/SCL總線選擇) |

| Xout | 24 | O | 晶體振蕩器輸出(不使用時留空或上拉) |

| Y1 - Y9 | 7, 8, 11 - 12, 15 - 21 | O | LVCMOS輸出 |

三、電氣特性與性能指標

(一)絕對最大額定值

在使用過程中,需注意器件的絕對最大額定值,以避免永久性損壞。例如,VDD電源電壓范圍為 -0.5V至2.5V,輸入電壓VI范圍為 -0.5V至VDD + 0.5V,輸出電壓VO范圍為 -0.5V至VDDOUT + 0.5V等。

(二)ESD(靜電放電)額定值

該器件的人體模型(HBM)ESD額定值為±2000V,帶電設備模型(CDM)ESD額定值為±1500V,在操作時需采取適當的防靜電措施,防止ESD對器件造成損壞。

(三)推薦工作條件

器件的推薦工作條件包括電源電壓、輸入電壓、輸出電流、負載電容等。例如,設備電源電壓VDD推薦為1.7V - 1.9V,輸出Yx電源電壓CDCE949為2.3V - 3.6V,CDCEL949為1.7V - 1.9V;輸入電壓方面,LVCMOS低電平輸入電壓VIL為0.3 × VDD,高電平輸入電壓VIH為0.7 × VDD等。

(四)典型特性

從典型特性曲線可以看出,器件的電源電流與PLL頻率、輸出頻率等因素有關。例如,隨著PLL開啟數量的增加和輸出頻率的提高,電源電流會相應增大。

四、功能模塊與工作模式

(一)功能模塊

器件的功能模塊包括輸入時鐘、PLL、VCXO、EEPROM、控制輸入等。輸入時鐘可選擇外部晶體或LVCMOS時鐘信號,經過PLL進行頻率合成和調整,VCXO可實現頻率的微調。EEPROM用于存儲用戶配置,控制輸入(S0/S1/S2)可靈活控制設備的工作狀態。

(二)工作模式

- SDA/SCL硬件接口:CDCEx949作為2線串行SDA/SCL總線的目標設備,兼容SMBus或I2C總線規范,支持標準模式(最高100kbps)和快速模式(最高400kbps)的傳輸,并支持7位尋址。

- 數據協議:支持字節寫入和讀取、塊寫入和讀取操作。字節寫入/讀取操作中,系統控制器可單獨訪問尋址字節;塊寫入/讀取操作中,字節按順序從最低字節到最高字節訪問,可在任何完整字節傳輸后停止。

五、應用與設計要點

(一)應用領域

CDCE949和CDCEL949可廣泛應用于多種領域,如數字電視(D - TVs)、機頂盒(STBs)、IP - STBs、DVD播放器和記錄器、打印機等。在這些應用中,器件能夠為視頻、音頻、USB、IEEE1394、RFID、藍牙、WLAN、以太網和GPS等提供高精度時鐘。

(二)典型應用示例

以千兆以太網交換機應用為例,可使用CDCEx949替代晶體和晶體振蕩器,減少外部元件數量,提高系統的集成度和穩定性。

(三)設計要點

- SSC設計:支持擴頻時鐘(SSC),可通過控制調制量、調制頻率、調制形狀等參數來降低電磁干擾。

- PLL頻率規劃:根據輸入頻率和輸出頻率要求,使用公式 (f{OUT }=frac{f{IN}}{ Pdiv } × frac{N}{M}) 計算輸出頻率,使用公式 (f{VCO}=f{IN} × frac{N}{M}) 計算目標VCO頻率,并根據相關條件確定P、Q、R和 (N') 的值。

- 晶體振蕩器啟動:當作為晶體緩沖器使用時,晶體振蕩器的啟動時間相比內部PLL鎖定時間更長,需注意這一點對系統啟動的影響。

- 頻率調整:可通過VCXO控制輸入 (V_{Ctrl}) 調整頻率,若使用PWM調制信號作為控制信號,需添加外部濾波器。

- 未使用引腳處理:若不需要VCXO拉頻功能,可將 (V_{Ctrl}) 引腳浮空;將其他未使用的輸入引腳接地,未使用的輸出引腳浮空。若某個輸出塊不使用,建議禁用該輸出塊,但仍需為第二個輸出塊提供電源。

- 模式切換:在從XO模式切換到VCXO模式時,需按照特定步驟操作,以確保輸出頻率居中。

- 電源供應:使用外部參考時鐘時,需先驅動XIN/CLK再使 (V{DD}) 上升,避免輸出不穩定。若 (V{DDOUT }) 先于 (V{DD}) 施加,建議將 (V{DD}) 拉至地,直到 (V_{DDOUT }) 上升。

- 布局設計:作為晶體緩沖器使用時,要注意晶體單元的布局,將晶體盡量靠近器件放置,確保晶體端子到XIN和XOUT的布線長度相同。避免在晶體及其布線區域下方布置接地平面和電源平面,避免在該區域布線其他信號線,以減少噪聲耦合。可根據需要添加離散電容來滿足晶體負載電容要求,并將其盡量靠近器件且對稱放置。同時,合理放置電源旁路電容,縮短其與器件電源引腳的連接,確保接地端與接地平面低阻抗連接。

六、總結

CDCE949和CDCEL949以其豐富的功能、靈活的配置和高性能的表現,為電子工程師在時鐘設計方面提供了優秀的解決方案。在實際應用中,工程師們需根據具體需求合理選擇和配置器件,注意設計要點,以確保系統的穩定性和可靠性。希望本文能幫助大家更好地理解和應用這兩款器件,在電子設計中取得更好的成果。你在使用這兩款器件的過程中遇到過哪些問題呢?歡迎在評論區分享交流。

-

CDCE949

+關注

關注

0文章

4瀏覽量

6808

發布評論請先 登錄

時鐘發生器CDCE949.pdf

基于CDCE949的可控頻率源設計

CDCE949 時鐘發生器

CDCE(L)949:支持SSC以降低EMI的靈活低功耗LVCMOS時鐘發生器數據表

深入剖析CDCE949與CDCEL949:高性能可編程時鐘發生器

深入剖析CDCE949與CDCEL949:高性能可編程時鐘發生器

評論