CDCE62005是一款高性能時(shí)鐘發(fā)生器和分配器,具有低輸出 抖動(dòng)、通過SPI接口實(shí)現(xiàn)高度可配置以及可編程啟動(dòng)模式 由片上EEPROM確定。專為時(shí)鐘數(shù)據(jù)轉(zhuǎn)換器和高速定制 數(shù)字信號(hào),該CDCE62005的抖動(dòng)性能遠(yuǎn)低于 1 ps RMS(10 kHz 至 20 MHz 集成帶寬)。

*附件:cdce62005.pdf

該CDCE62005集成了一個(gè)帶有部分集成環(huán)路濾波器的合成器模塊,一個(gè) 時(shí)鐘分配模塊,包括可編程輸出格式,以及具有 創(chuàng)新的智能多路復(fù)用器。時(shí)鐘分配塊包括五個(gè)可單獨(dú)編程的 可配置為提供不同輸出格式組合的輸出(LVPECL、LVDS、 LVCMOS)。每個(gè)輸出還可以編程為唯一的輸出頻率(高達(dá) 1.5 GHz)和偏斜 通過可編程延遲模塊建立關(guān)系(請(qǐng)注意,頻率范圍取決于工作模式 并選擇輸出格式)。如果所有輸出都配置為單端模式(例如, LVCMOS),該CDCE62005支持多達(dá)十個(gè)輸出。每個(gè)輸出可以選擇四個(gè)時(shí)鐘源之一 調(diào)節(jié)和分配,包括三個(gè)時(shí)鐘輸入中的任何一個(gè)或頻率的輸出 合成器。輸入模塊包括兩個(gè)支持頻率的通用差分輸入 在 40 kHz 至 500 MHz 范圍內(nèi),以及可配置為連接到 通過片上振蕩器模塊進(jìn)行外部晶體。

智能輸入多路復(fù)用器有手動(dòng)和自動(dòng)兩種作模式。在手冊(cè)中 模式下,用戶通過SPI接口選擇合成器基準(zhǔn)電壓源。在自動(dòng)模式下, 輸入多路復(fù)用器將自動(dòng)在最高優(yōu)先級(jí)輸入時(shí)鐘之間進(jìn)行選擇 可用。

特性

- 卓越的性能:

- 低噪聲時(shí)鐘發(fā)生器:550 fs rms(典型值)(10 kHz至20 MHz積分帶寬),F(xiàn)

C= 100兆赫 - 低噪聲抖動(dòng)清除器:2.6 ps rms(典型值)(10 kHz至20 MHz積分帶寬),F(xiàn)

C= 100兆赫

- 低噪聲時(shí)鐘發(fā)生器:550 fs rms(典型值)(10 kHz至20 MHz積分帶寬),F(xiàn)

- 靈活的頻率規(guī)劃:

- 5 個(gè)完全可配置的輸出:LVPECL、LVDS、LVCMOS 和特殊的高擺幅輸出模式

- 獨(dú)特的雙VCO架構(gòu)支持寬調(diào)諧范圍:1.750 GHz至2.356 GHz

- 頻率范圍為4.25 MHz至1.175 GHz(合成器模式)

- 扇出模式下輸出頻率高達(dá) 1.5 GHz

- 所有輸出的獨(dú)立粗偏控制

- 高靈活性:

- 集成EEPROM在上電時(shí)確定器件配置

- 智能輸入多路復(fù)用器可在三個(gè)基準(zhǔn)輸入之一之間自動(dòng)切換

- 7mm × 7mm 48引腳VQFN封裝(RGZ)

- –40°C 至 +85°C 溫度范圍

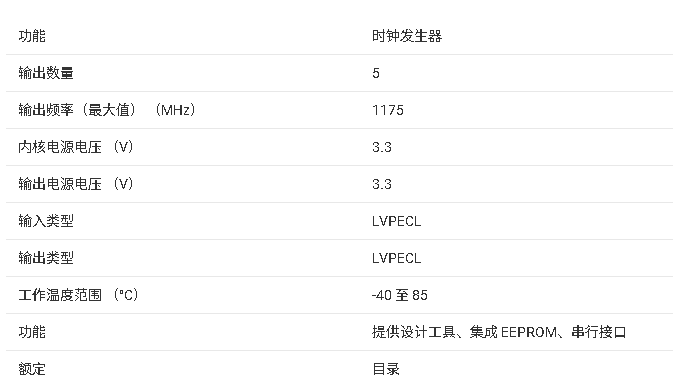

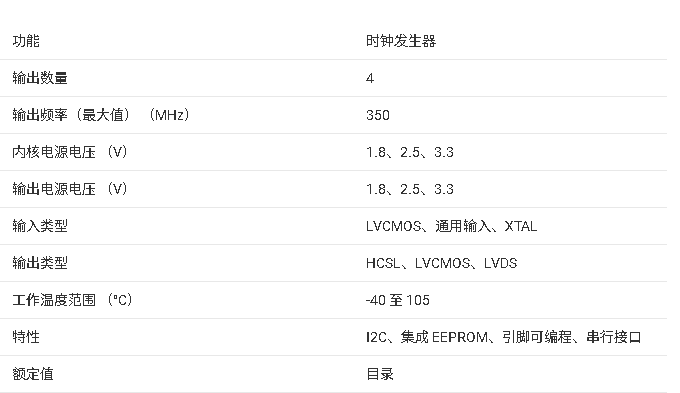

參數(shù)

方框圖

?1. 核心功能?

- ?高性能時(shí)鐘生成與抖動(dòng)清理?:集成雙VCO架構(gòu),支持合成器模式(4.25 MHz至1.175 GHz)和扇出模式(最高1.5 GHz),典型抖動(dòng)性能低至550 fs RMS(時(shí)鐘生成模式)和2.6 ps RMS(抖動(dòng)清理模式)。

- ?靈活輸出配置?:5個(gè)可編程輸出端口,支持LVPECL、LVDS、LVCMOS等多種電平格式,每個(gè)輸出可獨(dú)立設(shè)置頻率、延遲和格式。

- ?智能輸入多路復(fù)用器?:自動(dòng)或手動(dòng)切換3個(gè)參考時(shí)鐘輸入,支持40 kHz至500 MHz頻率范圍。

?2. 關(guān)鍵特性?

- ?雙VCO架構(gòu)?:寬調(diào)諧范圍1.750 GHz至2.356 GHz,適應(yīng)復(fù)雜頻率規(guī)劃需求。

- ?集成EEPROM?:上電時(shí)自動(dòng)加載配置,支持SPI接口實(shí)時(shí)編程。

- ?低功耗設(shè)計(jì)?:3.3V供電,48引腳VQFN封裝(7mm×7mm),工作溫度-40°C至+85°C。

?3. 應(yīng)用場(chǎng)景?

- 無線基礎(chǔ)設(shè)施、網(wǎng)絡(luò)交換機(jī)/路由器

- 醫(yī)療電子、航空航天及工業(yè)設(shè)備

- 高速數(shù)據(jù)轉(zhuǎn)換器(ADC/DAC)時(shí)鐘同步

?4. 技術(shù)細(xì)節(jié)?

- ?輸入接口?:支持差分輸入、外部晶體振蕩器(通過AUX_IN引腳)。

- ?輸出控制?:每個(gè)輸出可獨(dú)立選擇時(shí)鐘源(輸入或合成器),支持粗調(diào)延遲(coarse skew)。

- ?SPI控制?:通過寄存器映射配置頻率、輸出模式及系統(tǒng)狀態(tài)。

-

可編程

+關(guān)注

關(guān)注

2文章

1328瀏覽量

41520 -

數(shù)字信號(hào)

+關(guān)注

關(guān)注

2文章

1059瀏覽量

49525 -

分配器

+關(guān)注

關(guān)注

0文章

213瀏覽量

27392 -

時(shí)鐘發(fā)生器

+關(guān)注

關(guān)注

1文章

349瀏覽量

70114 -

SPI接口

+關(guān)注

關(guān)注

0文章

283瀏覽量

36777

發(fā)布評(píng)論請(qǐng)先 登錄

板子上沒有主控芯片給CDCE62005發(fā)送命令,如何設(shè)置它的時(shí)鐘輸出呢?

DAC3482用CDCE62005做時(shí)鐘發(fā)生器,產(chǎn)生的FIFO-OSTR又經(jīng)過了時(shí)鐘緩沖器CDCP1803,CDCP1803的作用是什么?

CDCE62005作為PLL需要外部輸入時(shí)鐘多少M(fèi)Hz?

CDCE62005第0通道沒有時(shí)鐘輸出

請(qǐng)問6678開發(fā)板TMDXEVM6678上CDCE62005的寄存器配置的數(shù)據(jù)是什么

CDCE62005 具有集成雙路 VCO 的 5/10 路輸出時(shí)鐘發(fā)生器/抖動(dòng)消除器

CDCE62005高性能時(shí)鐘發(fā)生器和分配器數(shù)據(jù)表

?CDCE6214 超低功耗時(shí)鐘發(fā)生器技術(shù)文檔總結(jié)

?CDCE62002 四輸出時(shí)鐘發(fā)生器/抖動(dòng)清除器技術(shù)文檔總結(jié)

?CDCE421A 時(shí)鐘發(fā)生器芯片技術(shù)文檔總結(jié)

?CDCE62005 時(shí)鐘發(fā)生器芯片技術(shù)文檔總結(jié)

?CDCE62005 時(shí)鐘發(fā)生器芯片技術(shù)文檔總結(jié)

評(píng)論