LMK04100系列精密時鐘調節器無需高性能VCXO模塊即可提供抖動清除、時鐘倍增和分配。

當連接到恢復的系統基準時鐘和VCXO時,該器件可生成5個LVCMOS、LVDS或LVPECL格式的低抖動時鐘。

*附件:lmk04110.pdf

特性

- 級聯 PLLatinum PLL 架構

- PLL1冗余基準輸入信號丟失

檢測自動和手動選擇

基準時鐘輸入 - PLL2相位檢測器速率高達100 MHz輸入

倍頻器集成VCO

- PLL1冗余基準輸入信號丟失

- 輸出

- LVPECL/2VPECL、LVDS 和

LVCMOS 格式 - 支持高達 1080 MHz 的時鐘速率

- 五個專用通道分頻器模塊

- 支持的常見輸出頻率:

30.72 MHz、61.44 MHz、62.5 MHz、

74.25 MHz、75 MHz、77.76 MHz、100 MHz、

106.25 MHz、125 MHz、122.88 MHz、

150 MHz、155.52 MHz、156.25 MHz、159.375 MHz、

187.5 MHz、200 MHz、

212.5 MHz、245.76 MHz、250 MHz、311.04 MHz、

312.5 MHz、368.64 MHz、

491.52 MHz、622.08 MHz、625 MHz、983.04 MHz

- LVPECL/2VPECL、LVDS 和

- MICROWIRE (SPI) 編程接口

- 工業溫度范圍:–40 至 85 °C

- 3.15 V 至 3.45 V 工作電壓

- 封裝:48 引腳 WQFN(7.0 × 7.0 × 0.8 mm)

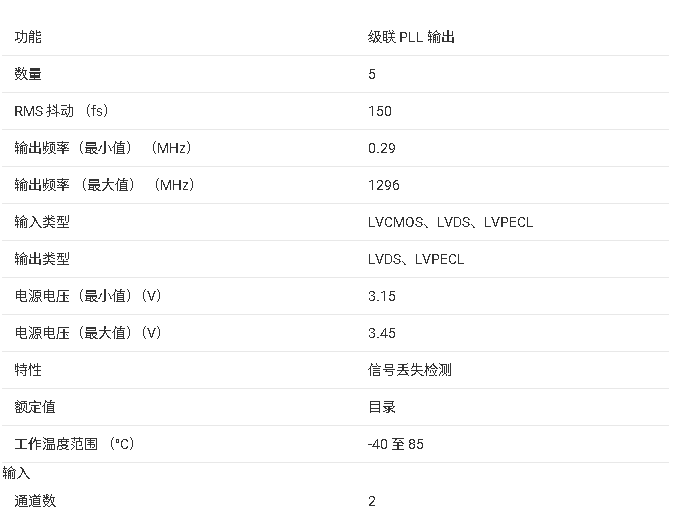

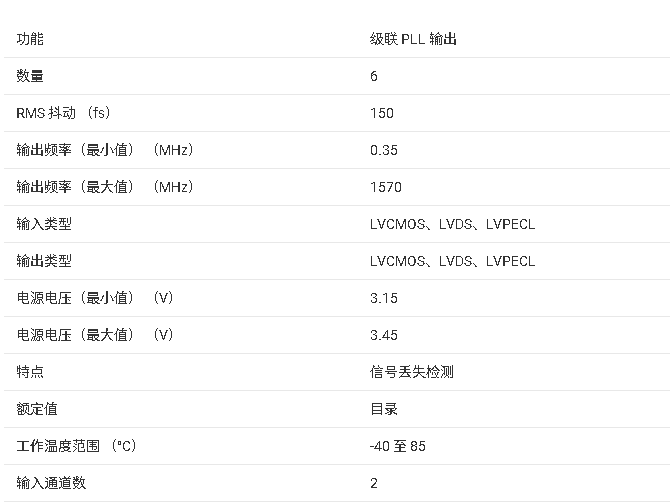

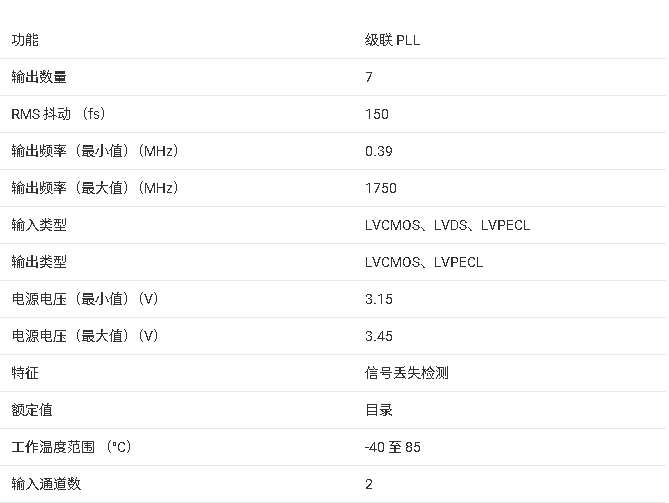

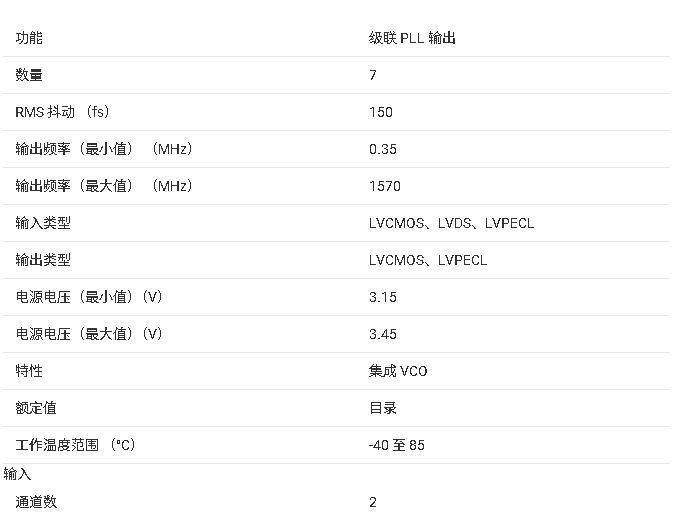

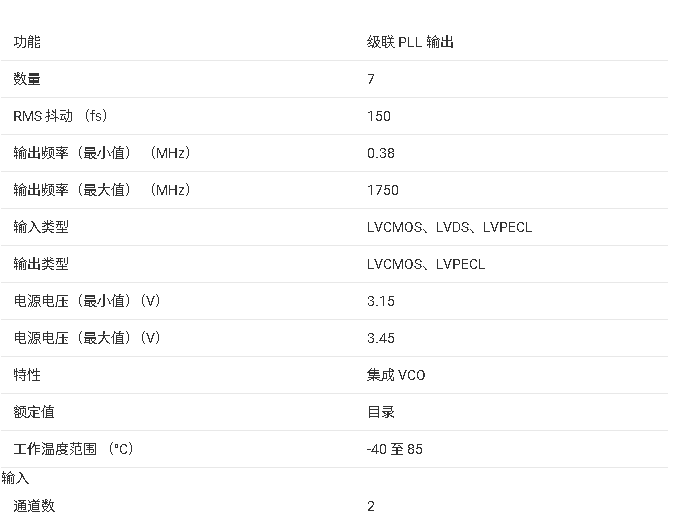

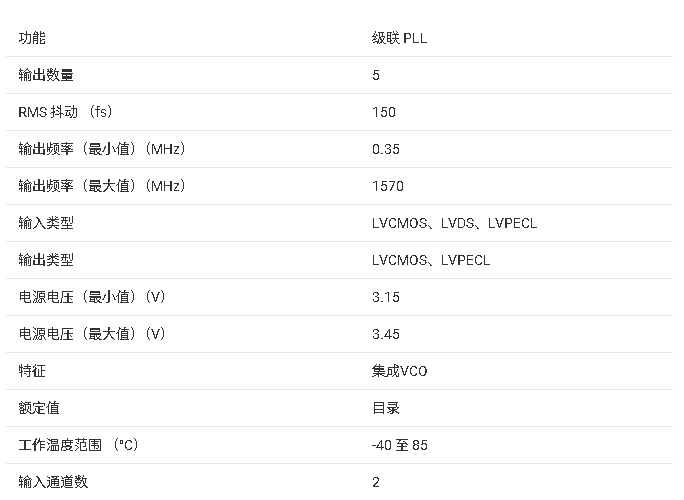

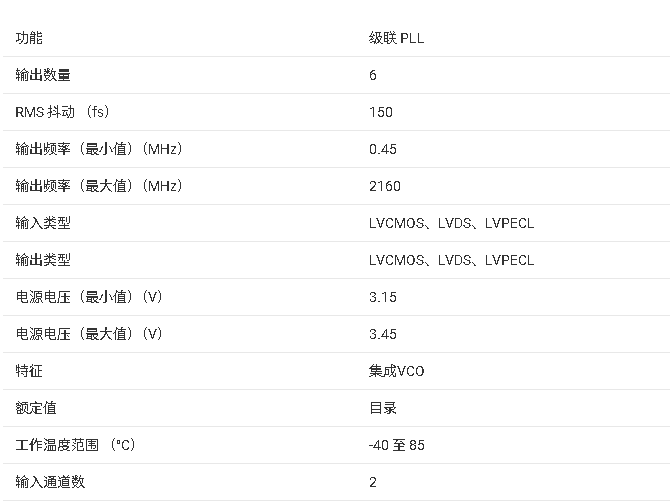

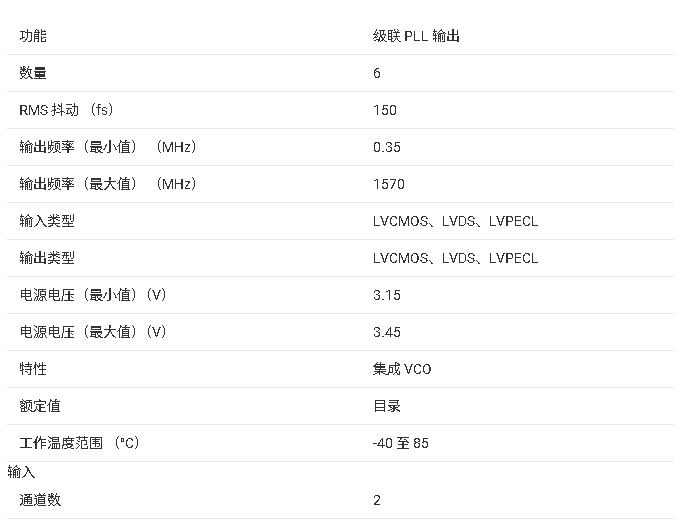

參數

方框圖

1. 產品概述?

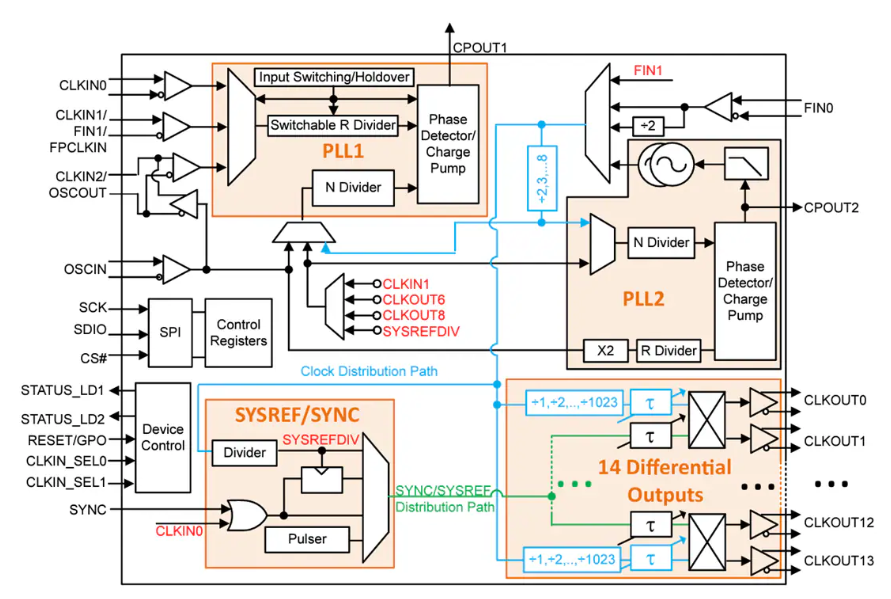

LMK04100家族是德州儀器(TI)推出的高精度時鐘調理芯片,集成雙級聯PLL架構,專為低抖動時鐘生成、乘法及分配設計。核心特點包括:

- ?雙PLL架構?:PLL1支持冗余參考輸入(CLKin0/1)和自動切換功能,PLL2集成VCO,相位檢測速率達100MHz。

- ?多格式輸出?:支持LVPECL/2VPECL、LVDS、LVCMOS格式,頻率覆蓋30.72MHz至983.04MHz。

- ?應用場景?:2G/3G/4G基站、高速ADC時鐘、光纖通信、廣播視頻等。

?2. 關鍵特性?

- ?PLL1?:

- 參考輸入支持LOS(信號丟失)檢測,自動/手動切換模式。

- 窄帶寬設計(10-200Hz),優化參考時鐘純凈度。

- ?PLL2?:

- 集成VCO(頻率范圍1185-2160MHz),支持寬帶寬(50-200kHz)。

- 可選內部環路濾波器(3/4階),減少外部元件需求。

- ?輸出通道?:5路獨立可編程分頻器(分頻比2-510),支持全局同步(SYNC*引腳)。

?3. 電氣參數?

- ?工作電壓?:3.15V至3.45V,工業溫度范圍(-40°C至85°C)。

- ?抖動性能?:

- 12kHz-20MHz積分RMS抖動:140-170fs(LVDS/LVPECL)。

- 1.875-20MHz積分RMS抖動:75-90fs。

- ?功耗?:典型值380-435mA(全輸出使能),支持低功耗模式。

?4. 功能模塊詳解?

- ?輸入接口?:

- ?控制接口?:

- MICROWIRE(SPI兼容)編程接口,32位寄存器配置。

- 鎖相檢測(LD引腳)可編程為PLL1/PLL2鎖定狀態輸出。

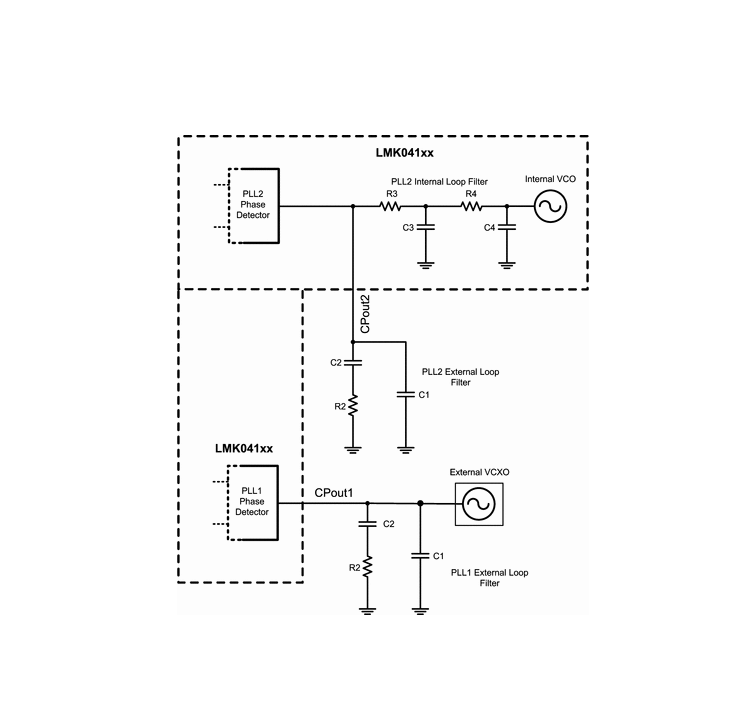

?5. 典型應用設計?

- ?環路濾波器?:

- PLL1需外部窄帶濾波器(推薦10-200Hz)。

- PLL2可選內部濾波器組件(R3/R4/C3/C4)。

- ?熱管理?:48引腳WQFN封裝(θJA=27.4°C/W),需確保結溫≤125°C。

?6. 寄存器配置?

?7. 設計注意事項?

?文檔范圍?

本文檔涵蓋器件功能、電氣規格、寄存器映射、應用電路及熱設計指南,適用于高頻低抖動時鐘系統設計。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

時鐘

+關注

關注

11文章

1955瀏覽量

134615 -

lvds

+關注

關注

2文章

1217瀏覽量

69202 -

調節器

+關注

關注

5文章

911瀏覽量

49184 -

VCXO

+關注

關注

0文章

55瀏覽量

10000 -

輸入信號

+關注

關注

0文章

558瀏覽量

13123

發布評論請先 登錄

相關推薦

熱點推薦

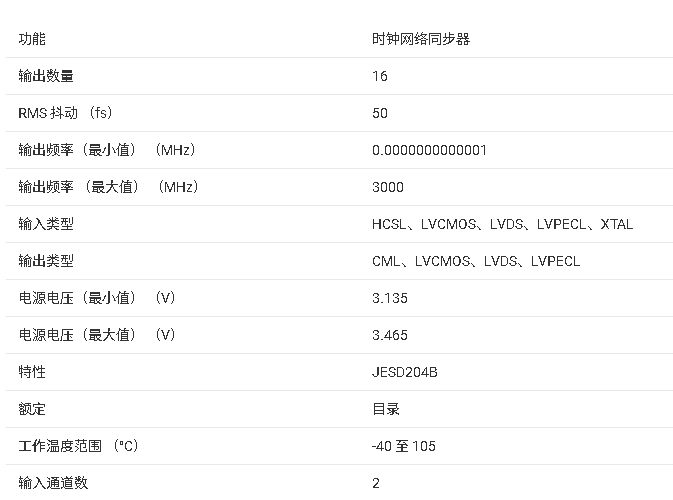

LMK04832-SP時鐘抖動清除器

SYSREF分頻器SYSREF時鐘的25ps步進模擬延遲設備時鐘和SYSREF的數字延遲和動態數字延遲PLL1的保持模式PLL1或PLL2的0延遲環境溫度范圍:–55°C至125°CLMK5C33216LMK04816LMK04808LMK04832-SPLMK04906LMK

發表于 03-24 16:13

LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表

電子發燒友網站提供《LMK04714-Q1符合JESD204B/C標準的汽車級、超低噪聲、雙環路時鐘抖動清除器數據表.pdf》資料免費下載

發表于 08-20 10:37

?0次下載

帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表

電子發燒友網站提供《帶雙環路PLL且符合JESD204B標準的LMK04832超低噪聲時鐘抖動清除器數據表.pdf》資料免費下載

發表于 08-21 09:20

?0次下載

LMK04906帶6路可編程輸出的,超低噪聲時鐘抖動清除器和乘法器數據表

電子發燒友網站提供《LMK04906帶6路可編程輸出的,超低噪聲時鐘抖動清除器和乘法器數據表.pdf》資料免費下載

發表于 08-21 09:21

?0次下載

具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器數據表

電子發燒友網站提供《具有雙環路PLL的LMK04228超低噪聲且符合JESD204B標準的時鐘抖動清除器數據表.pdf》資料免費下載

發表于 08-21 09:12

?0次下載

高性能時鐘抖動清除器LMK04714-Q1技術解析

Texas Instrument LMK04714-Q1雙環時鐘抖動清除器是一款高性能時鐘調節器,支持JEDEC JESD204B/C,適用于航天應用。PLL2的每個14時鐘輸出均可配

?LMK5C33216A 網絡同步器與抖動清除器總結

LMK5C33216A是一款高性能網絡同步器和抖動清除器,旨在滿足無線通信和基礎設施應用的嚴格要求。

該器件集成了三個 DPLL 和三個 APLL,通過可編程環路帶寬 (LBW)

LMK04131 抖動清除器技術文檔總結

LMK04100系列精密時鐘調節器無需高性能VCXO模塊即可提供抖動清除、時鐘倍增和分配。

當連接到恢復的系統基準時鐘和VCXO時,該器件可生成5個LVCMOS、LVDS或LVP

LMK04102 抖動清除器技術文檔總結

LMK04100系列精密時鐘調節器無需高性能VCXO模塊即可提供抖動清除、時鐘倍增和分配。

當連接到恢復的系統基準時鐘和VCXO時,該器件可生成5個LVCMOS、LVDS或LVP

LMK04110 抖動清除器技術手冊

LMK04110 抖動清除器技術手冊

評論