LMK5C33414A:高性能網(wǎng)絡(luò)同步器與抖動(dòng)清除器的深度剖析

在無(wú)線通信和基礎(chǔ)設(shè)施應(yīng)用領(lǐng)域,時(shí)鐘同步和抖動(dòng)控制至關(guān)重要。TI推出的LMK5C33414A網(wǎng)絡(luò)同步器和抖動(dòng)清除器,憑借其卓越的性能和豐富的功能,為這些應(yīng)用提供了強(qiáng)大的支持。本文將深入探討LMK5C33414A的特性、功能、應(yīng)用以及設(shè)計(jì)要點(diǎn)。

文件下載:lmk5c33414a.pdf

一、LMK5C33414A特性亮點(diǎn)

超低抖動(dòng)BAW VCO時(shí)鐘

LMK5C33414A采用超低抖動(dòng)BAW VCO技術(shù),在不同頻率下展現(xiàn)出出色的RMS抖動(dòng)性能。例如,在491.52MHz時(shí),典型RMS抖動(dòng)為40fs,最大為57fs;在245.76MHz時(shí),典型RMS抖動(dòng)為50fs,最大為62fs。這種超低抖動(dòng)特性為無(wú)線通信系統(tǒng)提供了穩(wěn)定、精確的時(shí)鐘信號(hào)。

多PLL架構(gòu)

該器件集成了三個(gè)高性能數(shù)字鎖相環(huán)(DPLL)和配對(duì)的模擬鎖相環(huán)(APLL)。DPLL的可編程環(huán)路帶寬范圍從1mHz到4kHz,DCO頻率調(diào)整步長(zhǎng)小于1ppt,能夠?qū)崿F(xiàn)高精度的頻率控制。同時(shí),四個(gè)差分或單端DPLL輸入支持1Hz(1PPS)到800MHz的輸入頻率,具備數(shù)字保持和無(wú)縫切換功能。

豐富的輸出配置

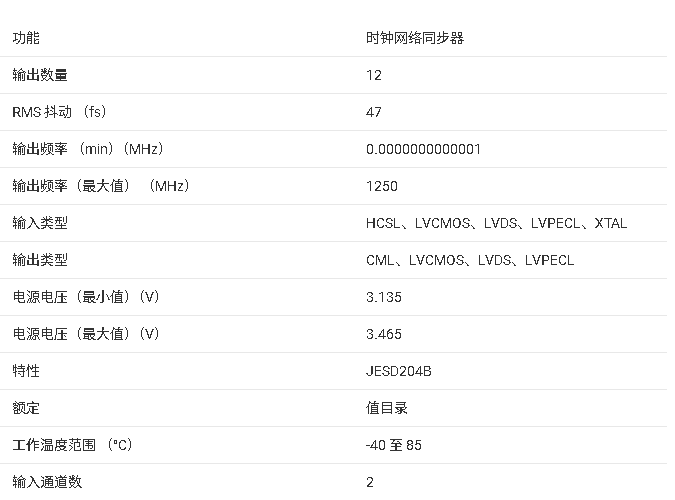

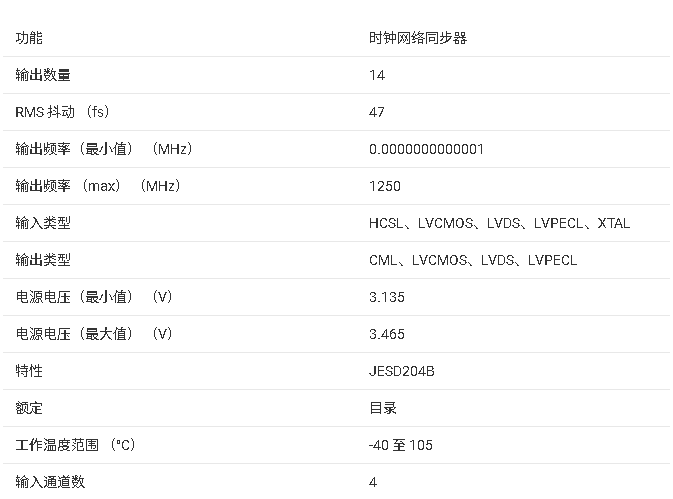

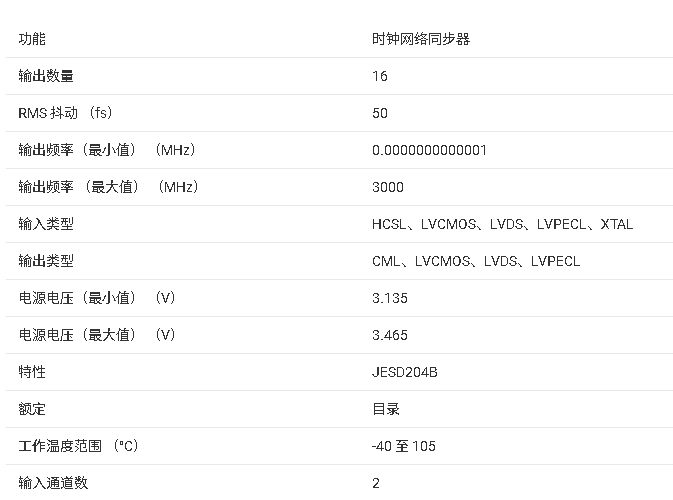

LMK5C33414A擁有14個(gè)差分輸出,支持可編程的HSDS、AC - LVPECL、LVDS和HSCL格式。當(dāng)配置為6個(gè)LVCMOS頻率輸出(OUT[1:0]_P/N、GPIO1和GPIO2)和12個(gè)差分輸出(OUT[13:2]_P/N)時(shí),總共可提供多達(dá)18個(gè)頻率輸出,輸出頻率范圍從1Hz(1PPS)到1250MHz,且輸出擺幅和共模電壓可編程。

兼容性良好

該器件兼容PCIe Gen 1到6,支持I2C、3線SPI或4線SPI通信接口,工作溫度范圍為 - 40°C到85°C,適用于各種復(fù)雜的應(yīng)用環(huán)境。

二、LMK5C33414A功能詳解

PLL架構(gòu)

1. DPLL與APLL協(xié)同工作

DPLL由時(shí)間數(shù)字轉(zhuǎn)換器(TDC)、數(shù)字環(huán)路濾波器(DLF)和可編程40位分?jǐn)?shù)反饋(FB)分頻器組成,APLL則包含參考(R)分頻器、相位頻率檢測(cè)器(PFD)、環(huán)路濾波器(LF)、分?jǐn)?shù)反饋(N)分頻器和VCO。每個(gè)DPLL都有參考選擇多路復(fù)用器,可選擇鎖定到另一個(gè)VCO域或參考輸入,實(shí)現(xiàn)多時(shí)鐘域的靈活頻率和相位控制。

2. 不同工作模式

- 獨(dú)立DPLL操作:每個(gè)DPLL可獨(dú)立選擇參考輸入,在啟動(dòng)時(shí),APLL先鎖定到XO輸入,當(dāng)檢測(cè)到有效DPLL參考輸入時(shí),DPLL開(kāi)始鎖定過(guò)程。

- 級(jí)聯(lián)DPLL操作:通過(guò)級(jí)聯(lián)DPLL,可提供干凈、低抖動(dòng)的輸出時(shí)鐘,與主同步DPLL同步。當(dāng)所有啟用的DPLL和APLL鎖定時(shí),所有啟用的輸出都與主同步DPLL選擇的參考同步。

- APLL與DPLL級(jí)聯(lián):VCBO作為級(jí)聯(lián)源為APLL1或APLL2提供高頻、超低抖動(dòng)參考時(shí)鐘,可改善近相位噪聲性能。

輸入輸出管理

1. 輸入監(jiān)測(cè)

DPLL參考輸入多路復(fù)用器支持自動(dòng)或手動(dòng)輸入選擇。參考輸入監(jiān)測(cè)塊對(duì)時(shí)鐘輸入進(jìn)行監(jiān)測(cè),當(dāng)檢測(cè)到參考丟失(LOR)時(shí),自動(dòng)進(jìn)行無(wú)縫切換或保持模式。同時(shí),支持鎖定到有缺失周期的間隙時(shí)鐘,提高了系統(tǒng)的適應(yīng)性。

2. 輸出配置

輸出時(shí)鐘通過(guò)輸出多路復(fù)用器從支持的APLL/VCO域獲取。輸出0(OUT0)和輸出1(OUT1)最為靈活,可選擇XO、參考輸入或任何APLL域作為源。輸出時(shí)鐘還支持SYSREF或1PPS輸出,輸出分頻器具有同步功能,可實(shí)現(xiàn)多個(gè)輸出的相位對(duì)齊。

其他功能

1. 零延遲模式(ZDM)

DPLL支持內(nèi)部ZDM同步選項(xiàng),可實(shí)現(xiàn)所選DPLL參考輸入與OUT0、OUT4或OUT10時(shí)鐘之間已知且確定的相位關(guān)系,主要用于實(shí)現(xiàn)輸入和所選輸出(如1PPS輸入到1PPS輸出)之間的確定性相位關(guān)系。

2. 時(shí)間計(jì)數(shù)器(TEC)

TEC允許用戶精確測(cè)量?jī)蓚€(gè)或多個(gè)事件之間的時(shí)間,測(cè)量精度優(yōu)于7.5ns,總測(cè)量時(shí)間超過(guò)59分鐘,具體取決于配置。

三、LMK5C33414A應(yīng)用場(chǎng)景

無(wú)線通信網(wǎng)絡(luò)

適用于4G和5G無(wú)線網(wǎng)絡(luò),如有源天線系統(tǒng)(AAS)、mMIMO宏遠(yuǎn)程無(wú)線電單元(RRU)、CPRI/eCPRI基帶、集中式和分布式單元(BBU、CU、DU)以及小基站等。可作為SyncE(G.8262)、SONET/SDH(Stratum 3/3E、G.813、GR - 1244、GR - 253)、IEEE - 1588 PTP從時(shí)鐘,為112G/224G PAM4 SerDes提供抖動(dòng)清除、漂移衰減和參考時(shí)鐘生成功能。

其他領(lǐng)域

還可應(yīng)用于光傳輸網(wǎng)絡(luò)(OTN G.709)、寬帶固定線路接入、工業(yè)、測(cè)試和測(cè)量等領(lǐng)域。

四、設(shè)計(jì)要點(diǎn)與建議

編程與配置

LMK5C33414A具有四個(gè)內(nèi)存空間:寄存器、ROM、EEPROM和SRAM。用戶可通過(guò)I2C或SPI對(duì)寄存器進(jìn)行編程,實(shí)現(xiàn)設(shè)備的配置。同時(shí),可利用TICS Pro編程軟件進(jìn)行設(shè)計(jì),生成頻率計(jì)劃和寄存器設(shè)置。

電源與布局

1. 電源供應(yīng)

在電源設(shè)計(jì)方面,要注意電源軌的順序、電源斜坡速率和混合電源域的問(wèn)題。建議使用LDO調(diào)節(jié)器為外部XO/TCXO/OCXO源供電,以減少電源噪聲對(duì)振蕩器時(shí)鐘的影響。輸出頻率相同或整數(shù)相關(guān)(諧波)的輸出可以共享一個(gè)濾波后的電源。

2. 布局設(shè)計(jì)

布局時(shí),要隔離輸入、XO/OCXO/TCXO和輸出時(shí)鐘,避免不同頻率的時(shí)鐘和其他動(dòng)態(tài)信號(hào)相互干擾。旁路電容器應(yīng)靠近VDD和VDDO引腳放置,以降低電源噪聲。同時(shí),要使用多個(gè)過(guò)孔將寬電源走線連接到相應(yīng)的電源島或平面,確保良好的電氣性能。

最佳實(shí)踐

- 對(duì)于未使用的模塊,通過(guò)寄存器將其關(guān)閉,以降低功耗。

- 對(duì)于活動(dòng)信號(hào),使用適當(dāng)?shù)脑椿蜇?fù)載端接,以匹配輸入和輸出時(shí)鐘走線的阻抗。

- 未使用的時(shí)鐘輸出可通過(guò)寄存器控制使其浮空并關(guān)閉電源,未使用的時(shí)鐘輸入可浮空處理。

- 在POR期間,可在每個(gè)GPIO引腳連接外部偏置電阻(10kΩ上拉到3.3V或10kΩ下拉),以選擇設(shè)備操作模式。

五、總結(jié)

LMK5C33414A作為一款高性能的網(wǎng)絡(luò)同步器和抖動(dòng)清除器,憑借其超低抖動(dòng)、多PLL架構(gòu)、豐富的輸入輸出配置和強(qiáng)大的功能,為無(wú)線通信和基礎(chǔ)設(shè)施應(yīng)用提供了可靠的解決方案。在設(shè)計(jì)過(guò)程中,工程師需要根據(jù)具體應(yīng)用需求,合理配置設(shè)備參數(shù),優(yōu)化電源和布局設(shè)計(jì),以充分發(fā)揮其性能優(yōu)勢(shì)。你在使用LMK5C33414A的過(guò)程中遇到過(guò)哪些問(wèn)題?又是如何解決的呢?歡迎在評(píng)論區(qū)分享你的經(jīng)驗(yàn)。

-

網(wǎng)絡(luò)同步器

+關(guān)注

關(guān)注

0文章

35瀏覽量

3020

發(fā)布評(píng)論請(qǐng)先 登錄

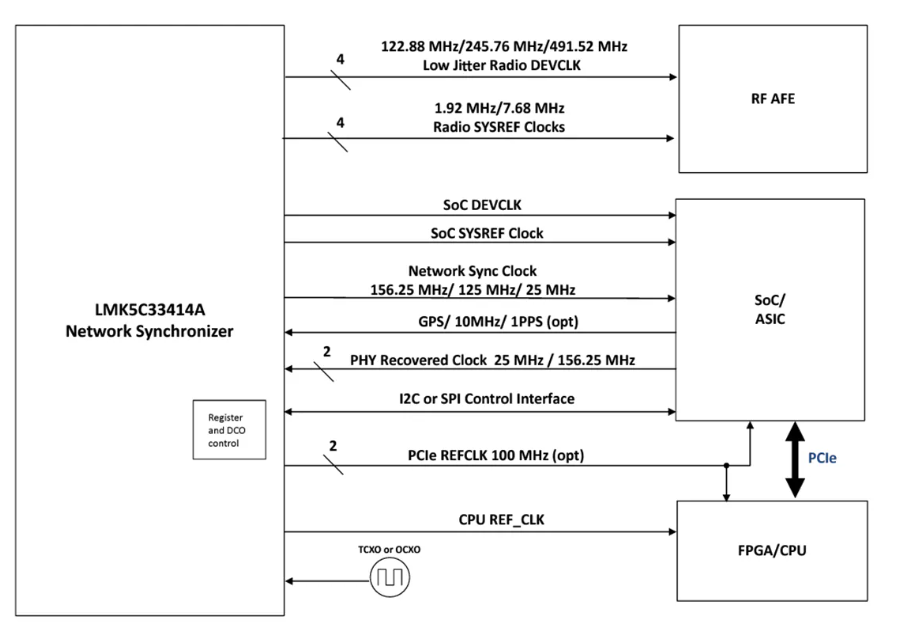

LMK5C33414A網(wǎng)絡(luò)同步器數(shù)據(jù)表

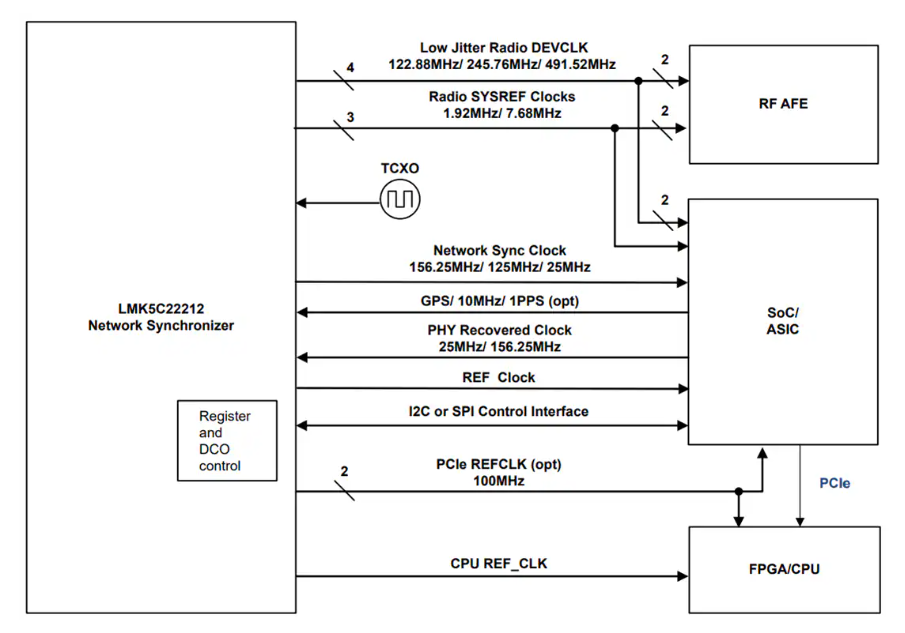

Texas Instruments LMK5C22212A網(wǎng)絡(luò)同步器數(shù)據(jù)手冊(cè)

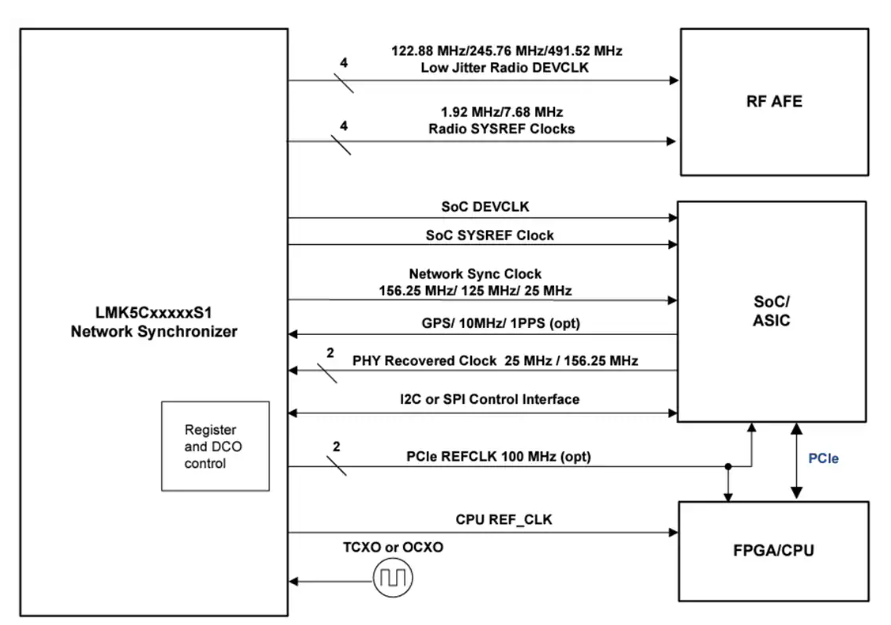

Texas Instruments LMK5C33414AS1網(wǎng)絡(luò)同步器數(shù)據(jù)手冊(cè)

高性能網(wǎng)絡(luò)同步器LMK5C33414A技術(shù)解析與應(yīng)用

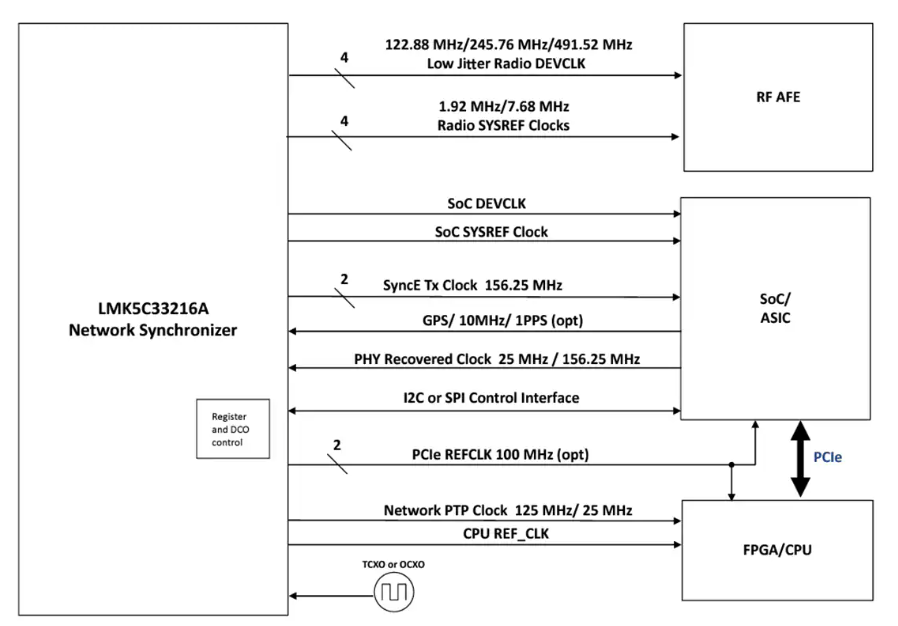

高性能網(wǎng)絡(luò)同步器LMK5C33216A技術(shù)解析與應(yīng)用

?LMK5C22212A網(wǎng)絡(luò)同步器技術(shù)文檔總結(jié)

?LMK5C33414AS1網(wǎng)絡(luò)同步器技術(shù)文檔總結(jié)

?LMK5C33414A網(wǎng)絡(luò)同步器技術(shù)文檔總結(jié)

?LMK5C33216A 網(wǎng)絡(luò)同步器與抖動(dòng)清除器總結(jié)

LMK5C33414A:高性能網(wǎng)絡(luò)同步器與抖動(dòng)清除器的深度剖析

LMK5C33414A:高性能網(wǎng)絡(luò)同步器與抖動(dòng)清除器的深度剖析

評(píng)論