?

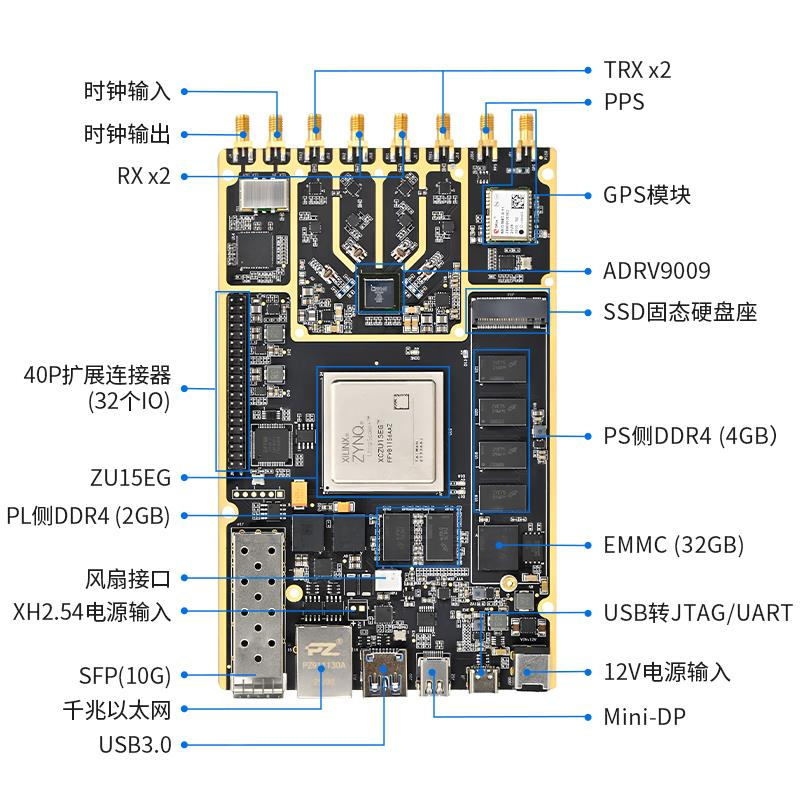

第一章:產(chǎn)品概述

1.1產(chǎn)品概述

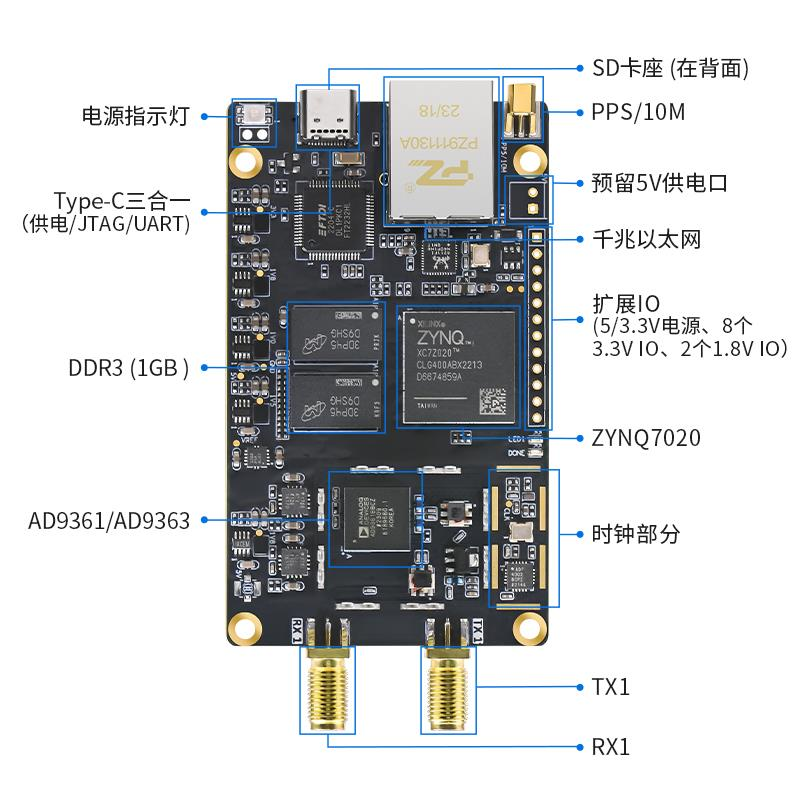

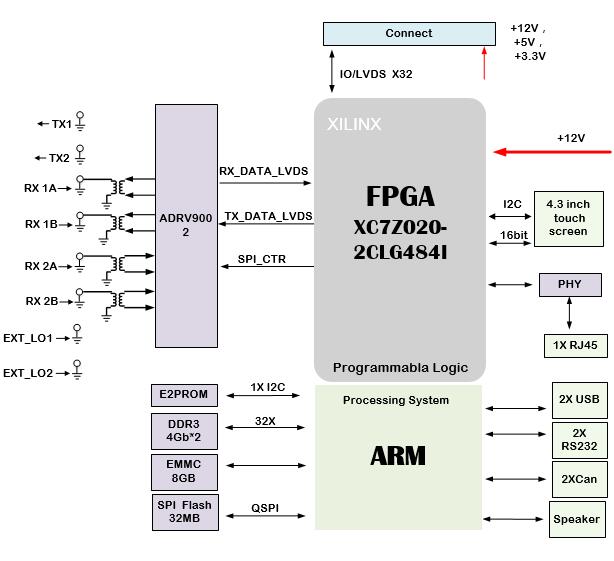

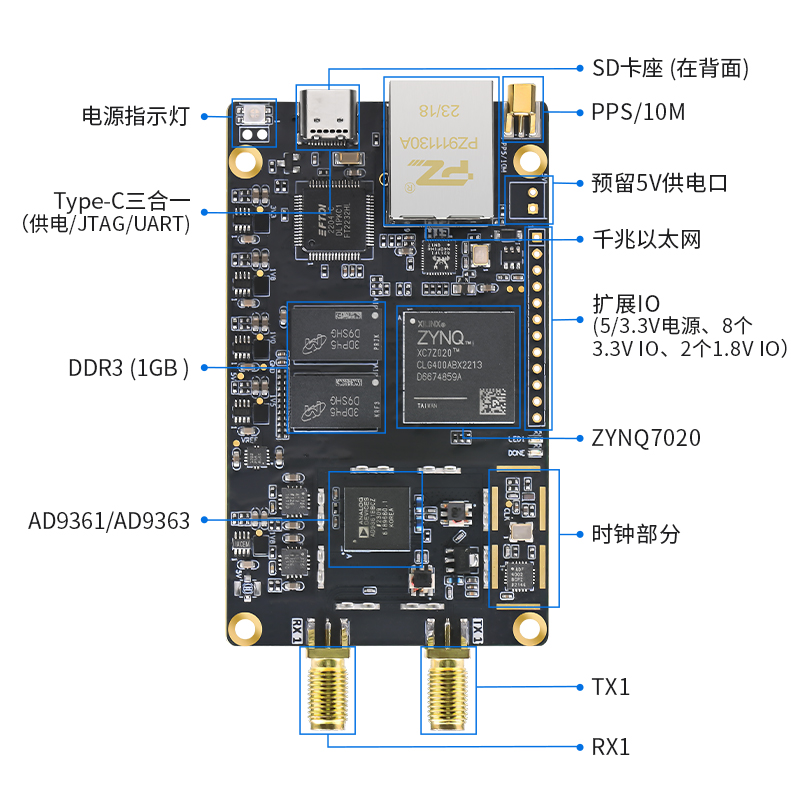

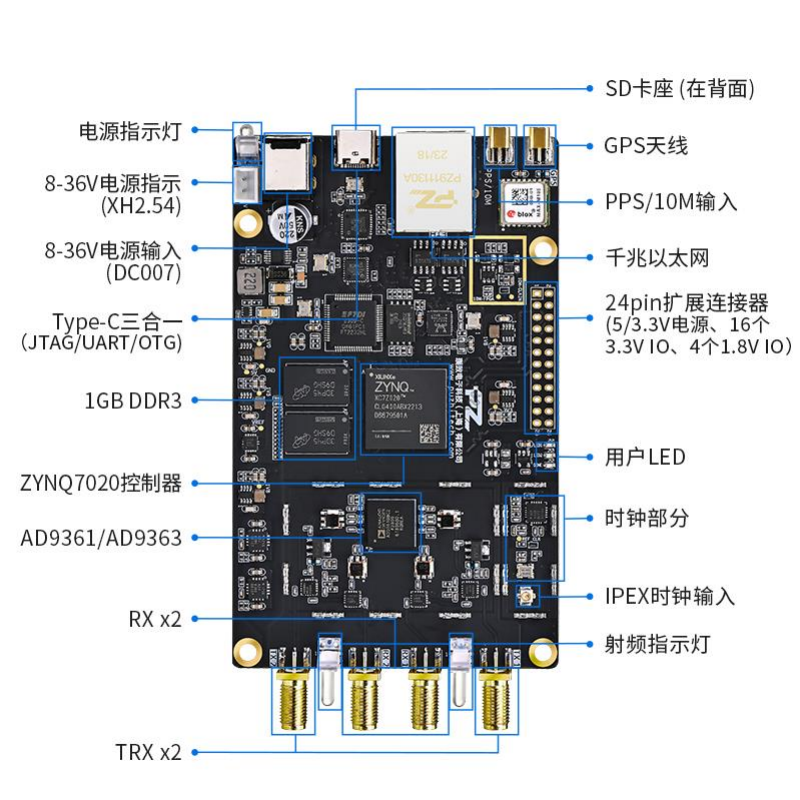

璞致軟件無線電 PZSDR 系列包括了眾多產(chǎn)品類別,本文介紹的是

P201Mini/P203Mini 兩款,兩款硬件完全兼容,軟件完全兼容,分別使用 了 XILINX 公司的 XC7Z020-2CLG400I 作為主控制器,搭載 ADI 公司的

AD9361/AD9363 射頻芯片構成了產(chǎn)品的主體架構。P201Mini 為 ZYNQ7020 搭 配 AD9361, P203Mini 為 ZYNQ7020 搭配 AD9363,兩款的主要差別在于射頻 芯片的帶寬不同,用戶可以根據(jù)實際需求來選擇對應產(chǎn)品。

P201Mini/P203Mini兩款集成了多種射頻和其他硬件接口,資源豐 富、方便易用,如下圖可以概覽產(chǎn)品內部資源結構。

P201Mini/P203Mini 的 PCB 尺寸是長寬=8550mm,PCB 厚度為 2.2mm,此外我們?yōu)楫a(chǎn)品配備了精美外殼,外殼尺寸為長寬高

=955523mm,整個外殼也起到了散熱的作用,確保了產(chǎn)品穩(wěn)定運行。

產(chǎn)品按照工業(yè)級標準設計,工作溫度-40—85℃,采用了0.5ppm 高精 度時鐘。

?編輯

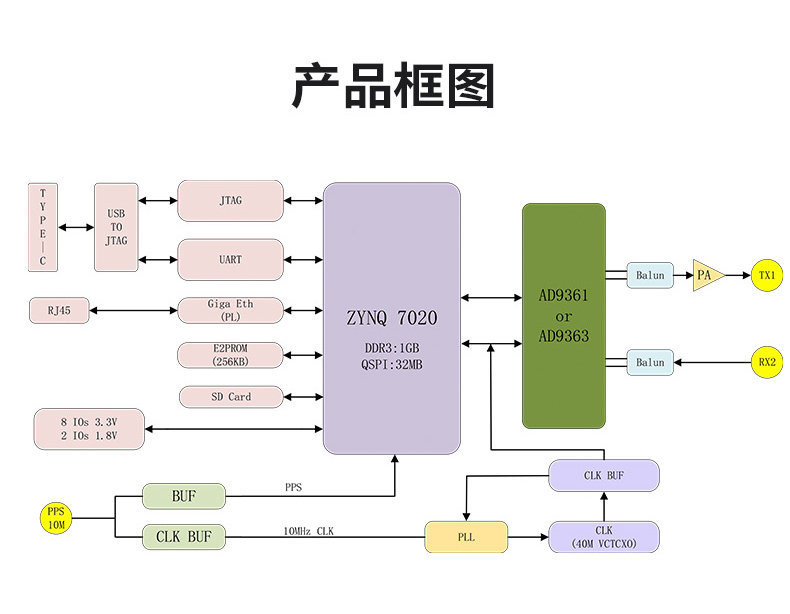

1.2********產(chǎn)品資源與框圖

如下框圖已列出產(chǎn)品板載資源,通過下表可以看到開發(fā)板所包含的所 有功能。

?編輯

1.3********產(chǎn)品尺寸與外殼

如下圖分別展示了產(chǎn)品 PCBA 尺寸與外殼尺寸。

?編輯

?編輯

[]()第二章:硬件使用說明

本章節(jié)開始我們將系統(tǒng)介紹產(chǎn)品的硬件,以便用戶快速上手使用。

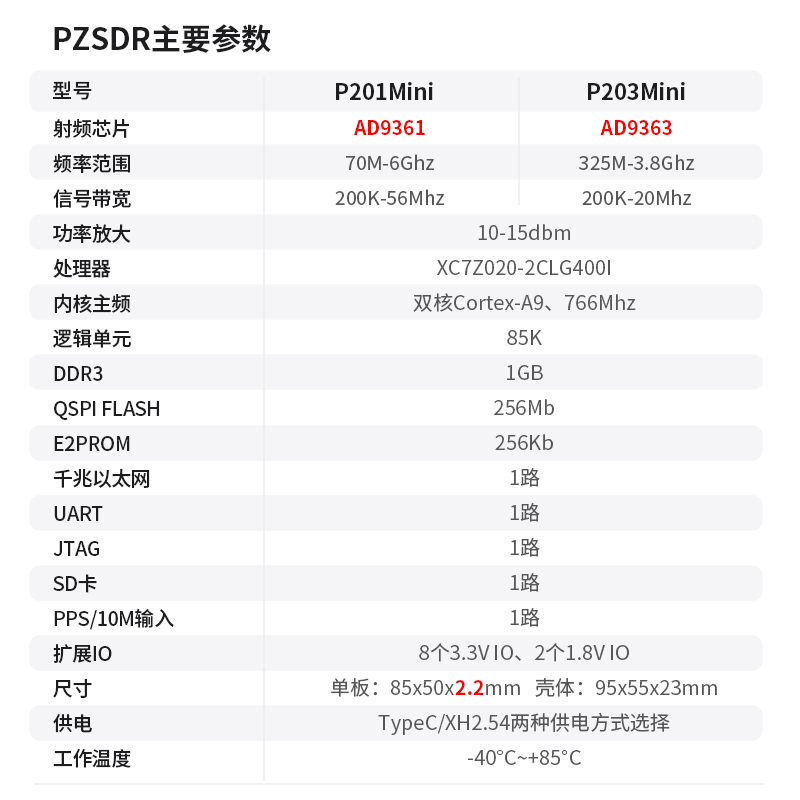

[]()2.1P201Mini與P203Mini對比

如下表列出了 P201Mini和 P203Mini 的參數(shù)指標,兩款產(chǎn)品的差異點在于射 頻芯片的選用不同,所以 P201Mini和 P203Mini 的差異表現(xiàn)在射頻端口的頻率范 圍不同、信號帶寬不同。用戶可以對比下表選擇對應產(chǎn)品使用。

?編輯

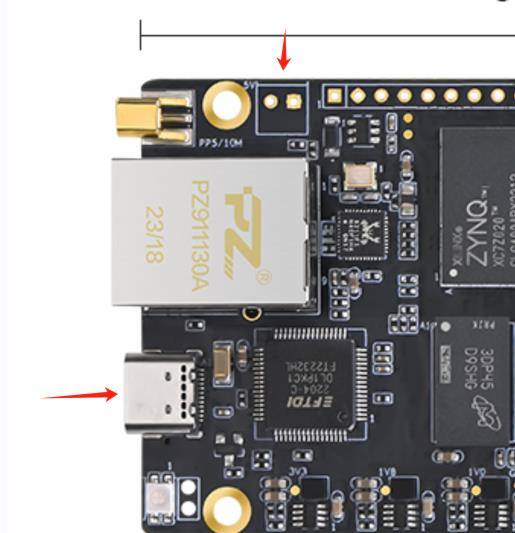

2.2********關于供電

產(chǎn)品提供了兩種供電方式:XH2.54 接口、TypeC 接口,兩種供電方式為客戶 在不同使用模式下供電。

XH2.54: 如果集成單板到自己的設備中,就可以通過 XH2.54 接口供電,供 電電壓范圍是 5V/1A,但是需要注意的是 5V 一定要處理好浪涌,可以在輸入口 加個電容,或者在外部加一級 DCDC 穩(wěn)壓。

TypeC:這里的 TypeC 接口提供了多重功能,既可以對板卡供電,直接接到 電腦 USB 接口上,即可為板卡提供 5V 電源。同時也是通信接口,提供了 JTAG、 UART 的通信功能,方便用戶下載和調試板卡。

?編輯

2.3********主控時鐘

單板為 PS 側提供了33.33Mhz 的時鐘輸入,輸入的管腳位置為 PS_CLK_500; 為 PL 端提供 40M 時鐘,輸入管腳位置為 IO_L14P_SRCC_35,管腳號為 J18。

2.4********主控復位

單板在靠近板邊位置提供了nGST 復位按鍵,為系統(tǒng)復位按鍵,低電平有效。 此引腳分別連接到 PS 側的 PS_POR_500 和 PL 側的 IO_12N_MRCC_34(管腳位置 U19)引腳上。

2.5********主控啟動模式

單板板支持三種啟動模式,分別是 JTAG、QSPI Flash、SD 卡。啟動模式的 切換可以提供板邊的撥動開關選擇,當開關撥動到 JTAG 側,即為 JTAG 啟動模 式,可以通過 JTAG 接口下載調試單板;當開關撥動到 QSPI/SD 側,啟動模式切 換為 QSPI Flash 和 SD 卡模式,在此模式下,我們做了特別的設計,當不接 SD 卡時,默認為 QSPI FLASH 啟動,當接了SD 卡時,啟動模式自動切換到SD 模式。

2.6DDR3介紹

PS 側設計了兩顆工業(yè)級 DDR3L 芯片,單顆容量 512MB,兩顆共計容量為 1GB, 型號為 MT41K256M16TW-107IT:P,DDR3L 管腳分配直接調用系統(tǒng)分配即可。也可 以參考我司提供的例程。

2.7QSPIFLASH********介紹

板載 256Mb 的 QSPI FLASH,可用于存儲啟動文件和用戶文件。 管腳定義如下表。

| QSPIFLASH引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| DATA0 | MIO2 | B8 |

| DATA1 | MIO3 | D6 |

| DATA2 | MIO4 | B7 |

| DATA3 | MIO5 | A6 |

| QSPI_CS | MIO1 | A7 |

| QSPI_CLK | MIO6 | A5 |

2.8E2PROM介紹

單板上預留了一顆 E2PROM,容量為 256Kb,管腳定義如下表。

| E2PROM********引腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| I2C_SCL | MIO10 | E9 |

| I2C_SDA | MIO11 | C6 |

2.9PL側千兆以太網(wǎng)

單板 PL 側設計了一顆千兆以太網(wǎng)芯片,以太網(wǎng)芯片與 ZYNQ 芯片之間通過 RGMII 接口互聯(lián),連接對應管腳見下表芯片地址 PHY_AD[2:0]=001。

| RMGII 信號 | 管腳名稱 | 管腳位置 |

|---|---|---|

| GPHY_GTX_CLK | IO_L3P_35 | E17 |

| GPHY_TXD0 | IO_L3N_35 | D18 |

| GPHY_TXD1 | IO_L4P_35 | D19 |

| GPHY_TXD2 | IO_L4N_35 | D20 |

| GPHY_TXD3 | IO_L5P_35 | E18 |

| GPHY_TX_EN | IO_L5N_35 | E19 |

| GPHY_RX_CLK | IO_L13P_MRCC_35 | H16 |

| GPHY_RXD0 | IO_L6P_35 | F16 |

| GPHY_RXD1 | IO_L6N_35 | F17 |

| GPHY_RXD2 | IO_L7P_35 | M19 |

| GPHY_RXD3 | IO_L7N_35 | M20 |

| GPHY_RX_DV | IO_L8P_35 | M17 |

| GPHY_MDC | IO_L2P_35 | B19 |

| GPHY_MDIO | IO_L2N_35 | A20 |

2.10SD卡

單板上設計了 SD 卡座,與PS 側 BANK501 相連,因為 BANK501 的電平為 1.8V,但 SD 的數(shù)據(jù)電平為 3.3V,所以使用 TXS02612RTWR 進行電平轉換。

如下是 SD 卡的管腳分配,更詳細電路可參考原理圖。

| SD********卡 | 管腳名稱 | 管腳位置 |

|---|---|---|

| SD_CLK | MIO40 | D14 |

| SD_CMD | MIO41 | C17 |

| SD_DATA0 | MIO42 | E12 |

| SD_DATA1 | MIO43 | A9 |

| SD_DATA2 | MIO44 | F13 |

| SD_DATA3 | MIO45 | B15 |

2.11USB轉JTAG和********UART

單板上設計了一路 USB 轉 JTAG/UART 接口,JTAG 連接到主控芯片的 JTAG 接口上, UART 連接到主控的 UART1 管腳上。

如下是 UART 管腳分配,更詳細電路可參考原理圖。

| UART | 管腳名稱 | 管腳位置 |

|---|---|---|

| UART1_TX | MIO12 | D9 |

| UART1_RX | MIO13 | E8 |

[]()2.12AD9361介紹

產(chǎn)品射頻部分使用了 ADI 公司的 AD9361,本小節(jié)我們將從射頻鏈路、數(shù)據(jù) 通道、時鐘部分詳細介紹。

[]()2.12.1********射頻前端電路

射頻前端電路涉及到巴倫、功放兩部分。巴倫的帶寬為 10M-6Ghz,覆蓋了 AD9361 的通信帶寬。

功放的帶寬是 50M-6Ghz,也是覆蓋了 AD9361 的通信帶寬,但功放在整個通 信帶寬的增益平坦度略有差異,如下表可以詳細看到功放在各頻點指標。

2.12.2AD9361控制和數(shù)據(jù)端口

AD9361 數(shù)字端口分為數(shù)據(jù)端口和控制端口兩部分,數(shù)據(jù)端口可以定義為 LVCMOS 也可以定義成 LVDS,LVCMOS 的通信速率不高,所以璞致提供的項目工程 里默認用 LVDS 接口來定義數(shù)據(jù)端口,如下表列出了管腳對應關系,也可以參考原 理圖。

| AD9361 接口 | 管腳名稱 | 管腳位置 |

|---|---|---|

| AD9631_TX_P0 | IO_8P_34 | W14 |

| AD9631_TX_N0 | IO_8N_34 | Y14 |

| AD9631_TX_P1 | IO_5P_34 | T14 |

| AD9631_TX_N1 | IO_5N_34 | T15 |

| AD9631_TX_P2 | IO_4P_34 | V12 |

| AD9631_TX_N2 | IO_4N_34 | W13 |

| AD9631_TX_P3 | IO_10P_34 | V15 |

| AD9631_TX_N3 | IO_10N_34 | W15 |

| AD9631_TX_P4 | IO_6P_34 | P14 |

| AD9631_TX_N4 | IO_6N_34 | R14 |

| AD9631_TX_P5 | IO_9P_34 | T16 |

|---|---|---|

| AD9631_TX_N5 | IO_9N_34 | U17 |

| AD9631_TX_FRAME_P | IO_7P_34 | Y16 |

| AD9631_TX_FRAME_N | IO_7N_34 | Y17 |

| AD9631_FB_CLK_P | IO_11P_SRCC_34 | U14 |

| AD9631_FB_CLK_N | IO_11N_SRCC_34 | U15 |

| AD9631_RX_P0 | IO_21P_34 | V17 |

| AD9631_RX_N0 | IO_21N_34 | V18 |

| AD9631_RX_P1 | IO_17P_34 | Y18 |

| AD9631_RX_N1 | IO_17N_34 | Y19 |

| AD9631_RX_P2 | IO_16P_34 | V20 |

| AD9631_RX_N2 | IO_16N_34 | W20 |

| AD9631_RX_P3 | IO_18P_34 | V16 |

| AD9631_RX_N3 | IO_18N_34 | W16 |

| AD9631_RX_P4 | IO_15P_34 | T20 |

| AD9631_RX_N4 | IO_15N_34 | U20 |

| AD9631_RX_P5 | IO_20P_34 | T17 |

| AD9631_RX_N5 | IO_20N_34 | R18 |

| AD9631_RX_FRAME_P | IO_19P_34 | R16 |

| AD9631_RX_FRAME_N | IO_19N_34 | R17 |

| AD9631_DATA_CLK_P | IO_13P_MRCC_34 | N18 |

| AD9631_DATA_CLK_N | IO_13N_MRCC_34 | P19 |

| AD9631_CLK_OUT | IO_14P_SRCC_34 | N20 |

| AD9631_SPI_CLK | IO_1P_34 | T11 |

| AD9631_SPI_nCS | IO_1N_34 | T10 |

| AD9631_SPI_DI | IO_2P_34 | T12 |

| AD9631_SPI_DO | IO_2N_34 | U12 |

| AD9631_nRST | IO_22N_34 | W19 |

| AD9631_ENABLE | IO_23P_34 | N17 |

| AD9631_EN_AGC | IO_23N_34 | P18 |

| AD9631_SYNC_IN | IO_24P_34 | P15 |

| AD9631_TXNRX | IO_24N_34 | P16 |

| AD9631_CTRL_OUT0 | IO_14N_SRCC_13 | Y8 |

| AD9631_CTRL_OUT1 | IO_14P_SRCC_13 | Y9 |

| AD9631_CTRL_OUT2 | IO_13P_MRCC_13 | Y7 |

| AD9631_CTRL_OUT3 | IO_15P_13 | V8 |

| AD9631_CTRL_OUT4 | IO_15N_13 | W8 |

| AD9631_CTRL_OUT5 | IO_16N_13 | W9 |

| AD9631_CTRL_OUT6 | IO_12N_MRCC_13 | U10 |

| AD9631_CTRL_OUT7 | IO_16P_13 | W10 |

| AD9631_CTRL_IN0 | IO_11P_SRCC_13 | U7 |

| AD9631_CTRL_IN1 | IO_12P_MRCC_13 | T9 |

| AD9631_CTRL_IN2 | IO_13N_MRCC_13 | Y6 |

| AD9631_CTRL_IN3 | IO_11N_SRCC_13 | V7 |

2.12.3AD9361時鐘電路

AD9361 的輸入時鐘采用的了 40M VCTCXO,精度高達 0.5ppm。此外板卡上預 留了 ADF4002BRUZ 芯片,如果對時鐘精度有更高要求,可以通過射頻頭輸入到 ADF4002BRUZ 來調整。對于時鐘的詳細使用可以參考璞致提供的原理圖來編程。

2.13PPS和時鐘輸入

板卡上設計了一路 PPS 輸入和 10M 時鐘輸入電路,此電路從同一個 mmcx 接口輸入, RC 電路配合 FPGA 的 IO 控制來選擇 PPS 和時鐘電路的通斷,此外 10M 時鐘信號還連接到 了 ADF4002 上,做時鐘校正。PPS 和時鐘分別連到 FPGA 的如下管腳:

| 信號名 | 管腳名稱 | 管腳位置 |

|---|---|---|

| PPS-IN | IO_12P_MRCC_35 | K17 |

| 10M_FPGA | IO_12P_MRCC_34 | U18 |

| EN_10M_FPGA | IO_18N_13 | Y11 |

| EN_10M_CLKIN | IO_18P_13 | W11 |

2.14IO擴展口

底板上設計了一個 12P 2.54mm 間距的排針,用于擴展信號的連接,如下 表標出了信號所在的芯片位置,詳細連接關系參考原理圖部分。

| IO 接口 | 管腳名稱 | 管腳位置 | 電平標準 |

|---|---|---|---|

| 1 | 5V | Power | |

| 2 | GND | GND | |

| 3 | IO_15P_35 | F19 | 3.3V |

| 4 | IO_15N_35 | F20 | |

| 5 | IO_20P_35 | G19 | |

| 6 | IO_20N_35 | G20 | |

| 7 | IO_23P_35 | M14 | |

| 8 | IO_23N_35 | M15 | |

| 9 | IO_17P_35 | J20 | |

| 10 | IO_17N_35 | H20 | |

| 11 | IO_20P_13 | Y12 | 1.8V |

| 12 | IO_20N_13 | Y13 |

2.15用戶LED

板卡上預留了一路 LED 做用戶自定義使用,LED 高電平亮,LED 低電平滅。 如下表列出了 LED 的管腳對應關系,更詳細說明可以參考提供的原理圖。

| LED 管腳 | 管腳名稱 | 管腳位置 |

|---|---|---|

| LED1 | IO_0_35 | G14 |

?

審核編輯 黃宇

-

FPGA

+關注

關注

1661文章

22442瀏覽量

637500 -

SDR

+關注

關注

7文章

242瀏覽量

52001 -

軟件無線電

+關注

關注

10文章

201瀏覽量

29916 -

開發(fā)板

+關注

關注

26文章

6325瀏覽量

119089

發(fā)布評論請先 登錄

代碼開源啦!用ESP32-P4 MINI開發(fā)板搭建雙攝像頭,帶你玩出新花樣!

【ESP32-P4系列】WT9932P4-MINI開發(fā)板上手指南

【ESP32-P4系列】WT9932P4-MINI開發(fā)板規(guī)格書

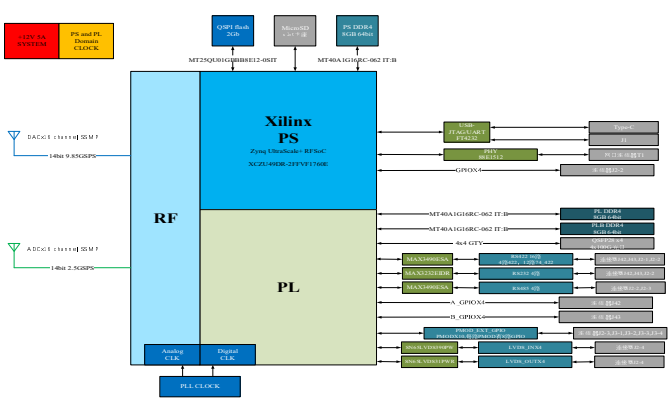

設計資料原理圖:622-基于ADRV9002 +ZYNQ7020 的軟件無線電 SDR(升級AD9361)

數(shù)字陣列板卡設計原理圖:889-基于RFSOC XCZU49DR的 16T16R的軟件無線電硬件

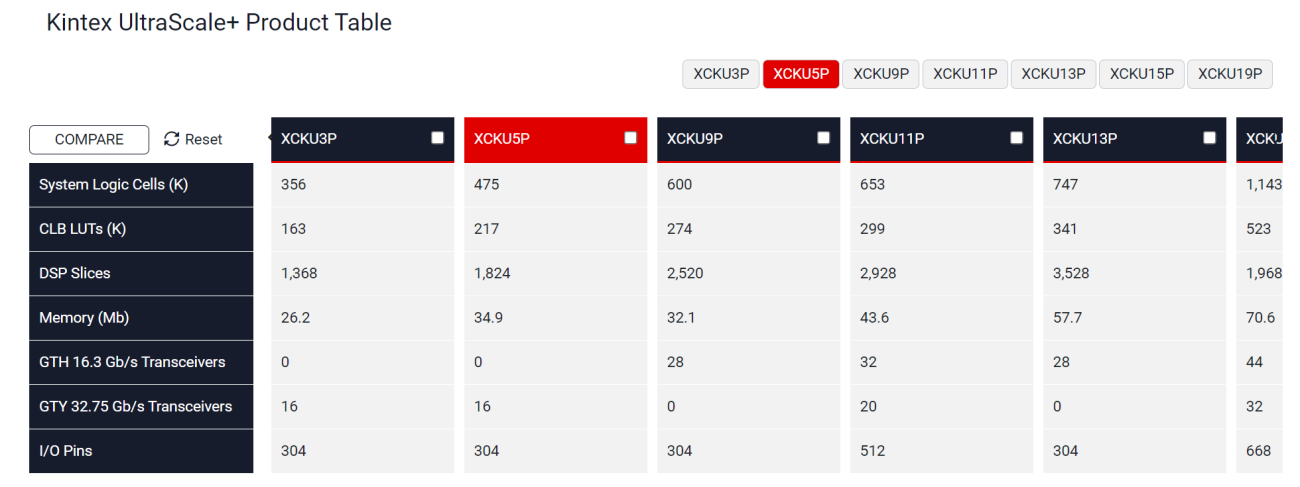

fpga開發(fā)板 璞致 Kintex UltraScale Plus PZ-KU3P 與 PZ-KU5P核心板與開發(fā)板用戶手冊

軟件無線電-AD9361 璞致 PZSDR 軟件無線電系列板卡之PZ-FL9361(FMCOMMS3)使用說明

璞致 PZSDR 系列板卡之 P159 軟件無線電硬件說明-ZU15EG+ADRV9009 16bit ADC & 14bit DAC

PZSDR/璞致 P201Pro(AD9361) 軟件無線電:工業(yè)級 SDR 解決方案,賦能多域技術創(chuàng)新

璞致電子 UltraScale+ RFSoC 架構下的軟件無線電旗艦開發(fā)平臺

璞致電子 【PZSDR P201MINI】P201Mini 軟件無線電開發(fā)板:緊湊型射頻系統(tǒng)的性能標桿

【PZSDR AD9361】——璞致PZ-FL9361 軟件無線電模塊:工業(yè)級射頻解決方案的技術標桿

ESP32-P4-MINI開發(fā)板開箱和上手指南來了!速速碼住!

璞致電子軟件無線電(PZSDR)系列——從嵌入式到高端射頻的全場景解決方案

璞致PZSDR 軟件無線電開發(fā)板系列板卡之P201Mini P203Mini 硬件說明—AD9361 AD9363

璞致PZSDR 軟件無線電開發(fā)板系列板卡之P201Mini P203Mini 硬件說明—AD9361 AD9363

評論