1、虛擬原型:芯片設(shè)計(jì)領(lǐng)域的革新利器

芯片設(shè)計(jì)公司長(zhǎng)期面臨雙重挑戰(zhàn):既要研發(fā)高性能芯片方案,又得縮短周期搶先推新。當(dāng)下,系統(tǒng)與軟件的復(fù)雜度與日俱增,傳統(tǒng)軟件開發(fā)方法在當(dāng)下復(fù)雜形勢(shì)中弊端漸顯,如介入時(shí)間靠后增加了開發(fā)周期,難滿足行業(yè)發(fā)展,革新勢(shì)在必行。“Shift Left”——左移開發(fā)理念雖并非新興概念,但其在當(dāng)下愈發(fā)凸顯出重要價(jià)值。其核心在于盡早進(jìn)入軟件開發(fā)環(huán)節(jié),利用虛擬平臺(tái)等與硬件設(shè)計(jì)并發(fā)進(jìn)行早期軟件開發(fā),也可利用軟件將驗(yàn)證和測(cè)試工作提前至設(shè)計(jì)初期。畢竟,設(shè)計(jì)初期發(fā)現(xiàn)并解決問題,成本和時(shí)間投入遠(yuǎn)低于項(xiàng)目后期。借助左移開發(fā),芯片設(shè)計(jì)公司能更主動(dòng)地把控質(zhì)量,降低潛在風(fēng)險(xiǎn)及問題定位成本,提升整體開發(fā)效率,從而縮短芯片開發(fā)周期。在左移開發(fā)理念的推動(dòng)下,虛擬原型技術(shù)嶄露頭角,為芯片設(shè)計(jì)和其配套軟件的開發(fā)帶來(lái)了全新的思路和方法。

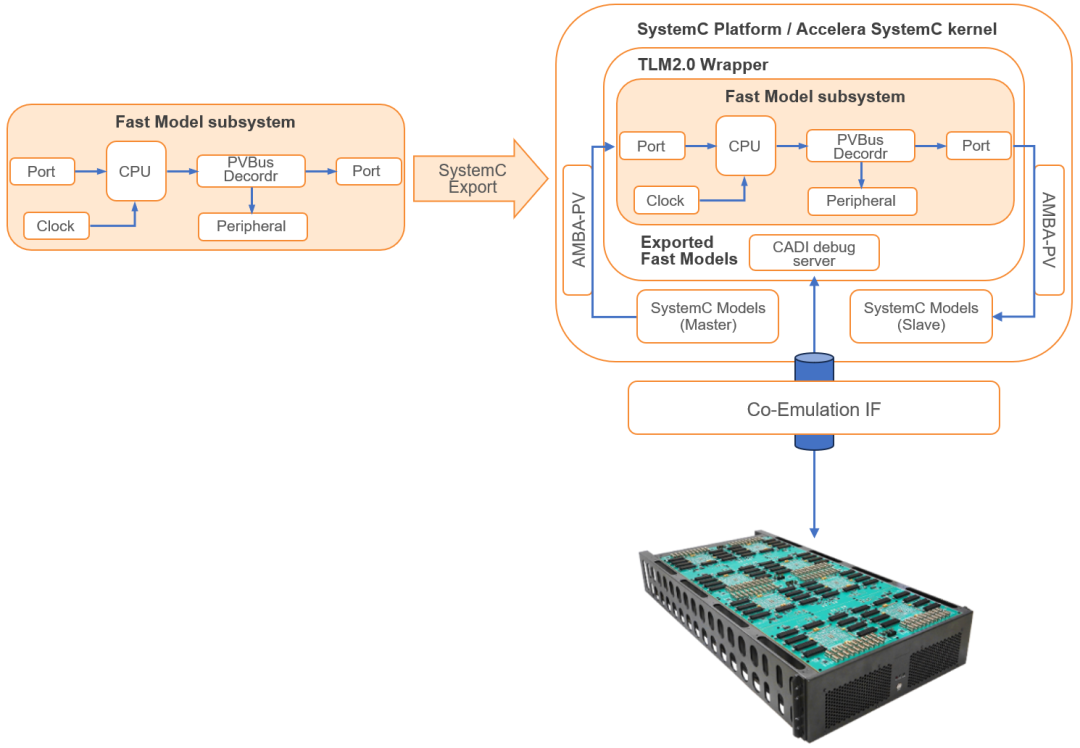

虛擬原型中的虛擬平臺(tái)提供全系統(tǒng)仿真能力,能夠在硬件還不具備的情況下提前進(jìn)行軟件開發(fā)。且基于虛擬原型開發(fā)的軟件可在項(xiàng)目開發(fā)的后續(xù)階段直接運(yùn)行在對(duì)應(yīng)的芯片上,這將大大提高項(xiàng)目的開發(fā)效率。且虛擬原型與傳統(tǒng)物理原型相比,虛擬平臺(tái)在可擴(kuò)展性、易用性、調(diào)試手段等方面有先天優(yōu)勢(shì)。如物理原型,需要高昂的FPGA、子卡等硬件成本,而且在構(gòu)建驗(yàn)證環(huán)境時(shí)耗時(shí)費(fèi)力。而虛擬平臺(tái)則可以輕松地根據(jù)設(shè)計(jì)需求進(jìn)行靈活調(diào)整和擴(kuò)展,為開發(fā)人員提供了更大的自由度和便利性。但物理原型上運(yùn)行的是真實(shí)的芯片IP設(shè)計(jì),在驗(yàn)證精準(zhǔn)度、IP復(fù)用等方面有虛擬原型不可比擬的優(yōu)勢(shì)。虛擬原型考慮到仿真速度等原因,一般在事務(wù)級(jí)進(jìn)行建模從而忽略了設(shè)計(jì)的細(xì)節(jié)。物理原型仿真的是真實(shí)芯片設(shè)計(jì),能夠精確仿真芯片的運(yùn)行細(xì)節(jié)。同時(shí),對(duì)于已有IP也可以直接集成到物理原型中,不需要再投入人力對(duì)其重新進(jìn)行建模。混合仿真解決方案將結(jié)合虛擬原型仿真速度、左移開發(fā)與物理原型在精確度上的優(yōu)勢(shì)帶來(lái)更高效的驗(yàn)證方案。

2、混合仿真:融合物理原型與虛擬原型的前沿技術(shù)

混合仿真不僅能夠助力實(shí)現(xiàn)更早的架構(gòu)優(yōu)化與軟件開發(fā),還能在關(guān)鍵IP(知識(shí)產(chǎn)權(quán)核)的寄存器傳輸級(jí)(RTL)驗(yàn)證過程中,通過軟件驅(qū)動(dòng)RTL驗(yàn)證實(shí)現(xiàn)更高的驗(yàn)證效率。混合仿真解決方案讓系統(tǒng)的一部分在硬件原型或硬件仿真器中運(yùn)行,另一部分在虛擬原型中運(yùn)行,結(jié)合二者的優(yōu)勢(shì),建構(gòu)混合驗(yàn)證系統(tǒng)。混合仿真具有三個(gè)主要應(yīng)用場(chǎng)景,分別是架構(gòu)探索、支持早期軟件開發(fā)以及開展硬件驗(yàn)證。

- 架構(gòu)探索

在架構(gòu)探索階段,需要調(diào)整如總線拓?fù)洹?nèi)存帶寬、cache結(jié)構(gòu)等系統(tǒng)參數(shù),并結(jié)合仿真結(jié)果找到最優(yōu)的芯片架構(gòu)。在這個(gè)過程中,仿真的速度和仿真的精確度都至為重要,前者決定了架構(gòu)探索效率,后者決定了仿真結(jié)果是否可信。在使用混合仿真進(jìn)行架構(gòu)探索時(shí),可將需要高精確度但運(yùn)行速度稍慢的部分使用RTL實(shí)現(xiàn),而不關(guān)注的部分使用低精度但仿真速度較快的部分使用事務(wù)級(jí)模型實(shí)現(xiàn),從而兼顧二者優(yōu)勢(shì)。如,在對(duì)SoC中某個(gè)外設(shè)的訪存帶寬進(jìn)行優(yōu)化時(shí),可通過事務(wù)級(jí)的指令仿真器實(shí)現(xiàn)CPU指令的執(zhí)行,通過在指令仿真器中運(yùn)行二進(jìn)制觸發(fā)不同應(yīng)用場(chǎng)景下外設(shè)對(duì)內(nèi)存的訪問并進(jìn)行統(tǒng)計(jì),從而找到瓶頸點(diǎn)和優(yōu)化方向。

- 早期軟件開發(fā)

絕大多數(shù)情況下,硬件需要配套相應(yīng)的軟件才能正常工作,而在傳統(tǒng)開發(fā)模式下,軟件團(tuán)隊(duì)一般需要等待硬件開發(fā)驗(yàn)證完成才能投入軟件的適配開發(fā)和測(cè)試;且在大型的芯片開發(fā)過程中,各硬件模塊的開發(fā)進(jìn)度一般是不同的,導(dǎo)致軟件團(tuán)隊(duì)需等待最慢的一個(gè)硬件模塊完成驗(yàn)證才能進(jìn)行開發(fā),這將拉長(zhǎng)整體項(xiàng)目的周期,降低研發(fā)效率。因此,通過虛擬平臺(tái)使能早期軟件開發(fā)可以成為提升項(xiàng)目整體開發(fā)效率的關(guān)鍵舉措。同時(shí),隨著硬件模塊開發(fā)的推進(jìn),混合仿真可將已開發(fā)完成的硬件模塊集成到虛擬平臺(tái)中,使軟件團(tuán)隊(duì)能盡早得使用實(shí)際設(shè)計(jì)的硬件進(jìn)行開發(fā)、驗(yàn)證。隨著開發(fā)進(jìn)度的進(jìn)行逐步完成虛擬平臺(tái)中各模塊的替代,并最終完全遷移到物理原型中。

- 開展硬件驗(yàn)證

硬件驗(yàn)證是確保芯片設(shè)計(jì)正確性和可靠性的關(guān)鍵環(huán)節(jié)。混合仿真允許在實(shí)際的軟件負(fù)載下運(yùn)行硬件系統(tǒng),這為硬件驗(yàn)證提供了更加真實(shí)和全面的測(cè)試環(huán)境。通過在實(shí)際軟件負(fù)載下進(jìn)行驗(yàn)證,開發(fā)人員能夠更早、更準(zhǔn)確地發(fā)現(xiàn)硬件設(shè)計(jì)中存在的問題,如性能瓶頸、兼容性問題等,并及時(shí)進(jìn)行修復(fù)和優(yōu)化,從而提高芯片的質(zhì)量和可靠性。

3、可擴(kuò)展的虛擬平臺(tái):混合仿真的堅(jiān)實(shí)基石

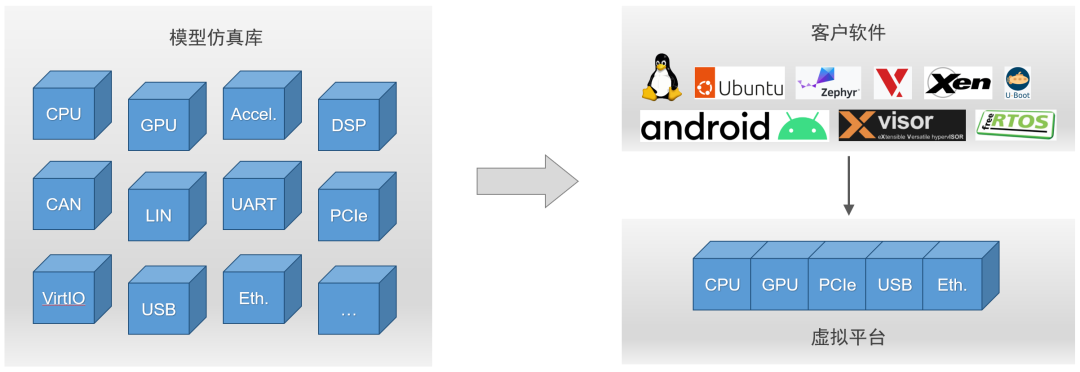

可擴(kuò)展的虛擬平臺(tái)是混合仿真得以實(shí)現(xiàn)的重要基礎(chǔ)。通過提供各種組件,開發(fā)人員可根據(jù)設(shè)計(jì)需求,將這些組件像搭積木一樣拼接成虛擬原型(VP)。在這個(gè)VP之上,可運(yùn)行多種操作系統(tǒng)或應(yīng)用程序,如Ubuntu、Android、U - boot、RTOS等,為芯片配套的軟件開發(fā)和驗(yàn)證提供豐富測(cè)試場(chǎng)景。

以思爾芯的Genesis芯神匠Virtual Platform(以下簡(jiǎn)稱 VP)為例,它是一個(gè)典型的虛擬原型平臺(tái)。該平臺(tái)具備高度可擴(kuò)展性和靈活性,能滿足不同芯片設(shè)計(jì)項(xiàng)目需求。開發(fā)人員可利用Genesis VP提供的豐富組件和工具,以及思爾芯的芯神瞳原型驗(yàn)證平臺(tái),快速搭建符合項(xiàng)目要求的虛擬原型,加速芯片設(shè)計(jì)和開發(fā)進(jìn)程。

4、混合仿真的應(yīng)用場(chǎng)景

- 場(chǎng)景1:系統(tǒng)早期Bring-up

在芯片尚不可用之前,混合仿真解決方案能提供良好的IP 接入,借助虛擬平臺(tái)為軟件開發(fā)創(chuàng)造有利條件。開發(fā)的軟件同時(shí)也作為RTL硬件的驗(yàn)證激勵(lì)。開發(fā)人員可在虛擬平臺(tái)的CPU上運(yùn)行開發(fā)的軟件,作為硬件驗(yàn)證編寫的測(cè)試模型,通過將暫未完成開發(fā)的RTL模塊遷移到虛擬平臺(tái),可以盡早地構(gòu)建完整的驗(yàn)證系統(tǒng)并bring-up,從而使能早期軟件開發(fā),提升驗(yàn)證效率。

- 場(chǎng)景2: 降低TAT并提高可調(diào)試性

虛擬平臺(tái)有助于提高測(cè)試覆蓋率、生產(chǎn)力和質(zhì)量。它具備集成豐富的調(diào)試能力,能夠讓開發(fā)人員直觀地觀察從代碼到硬件內(nèi)部寄存器的運(yùn)行情況,從而提升測(cè)試和問題解決效率。開發(fā)人員可以根據(jù)應(yīng)用場(chǎng)景在軟件中創(chuàng)建Corner測(cè)試,并在思爾芯的芯神瞳原型驗(yàn)證平臺(tái)上執(zhí)行,提高生產(chǎn)力。同時(shí),在虛擬原型中構(gòu)建的用例可作為在原型驗(yàn)證平臺(tái)上運(yùn)行的高性能回歸測(cè)試,進(jìn)一步確保芯片的質(zhì)量和性能。

- 場(chǎng)景3: FPGA加速提升整體系統(tǒng)性能

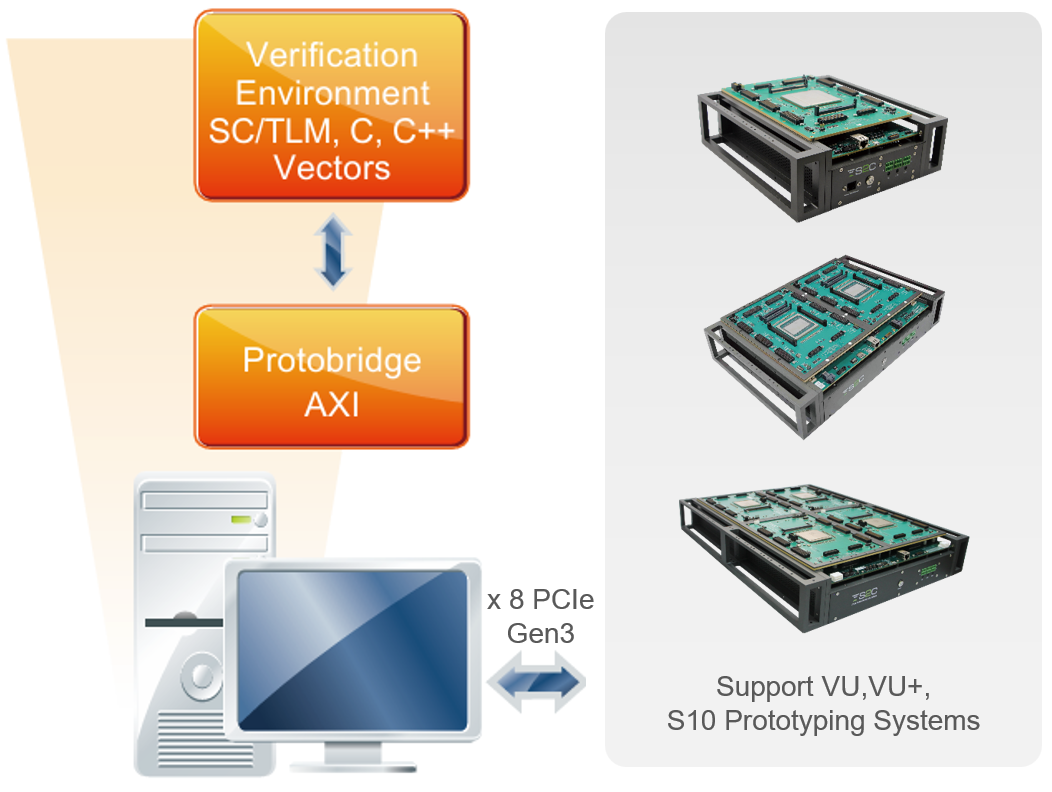

利用虛擬平臺(tái)和思爾芯的芯神瞳FPGA的混合仿真技術(shù)能有效加速仿真時(shí)間。對(duì)于軟件速度表現(xiàn)不佳的組件,可移植到FPGA實(shí)施,剩余部分組件則運(yùn)行在軟件上。如:客戶先撰寫SystemC or C/C++模型,運(yùn)行整體系統(tǒng)仿真,判斷哪些模型是性能瓶頸并可通過FPGA執(zhí)行提升運(yùn)行效率,然后通過HLS等方法將這些模型轉(zhuǎn)化到RTL并部署到FPGA再運(yùn)行仿真,以實(shí)現(xiàn)系統(tǒng)仿真性能的提升。

- 場(chǎng)景4: 提高可復(fù)用性

混合仿真系統(tǒng)能充分利用已經(jīng)存在并完全驗(yàn)證的RTL。在芯片設(shè)計(jì)中,常常會(huì)用到三方IP,或者行為模型SystemC or C/C++尚未準(zhǔn)備好的情況;或這些模型雖然可用,但可能具有特定限制,且與 RTL 并不完全等效。此時(shí),重復(fù)使用RTL在之前的客戶項(xiàng)目中就具有很大優(yōu)勢(shì),不必將其轉(zhuǎn)換為 SystemC模型,而且RTL模型可能已在FPGA中部署,進(jìn)一步提高開發(fā)效率和資源利用率。

5、成功案例 - SW + FPGA開發(fā)板

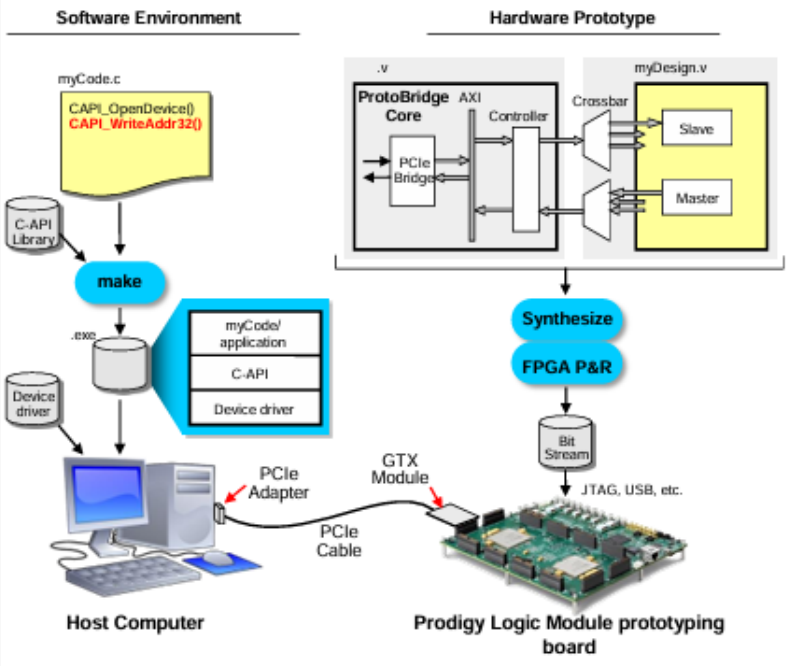

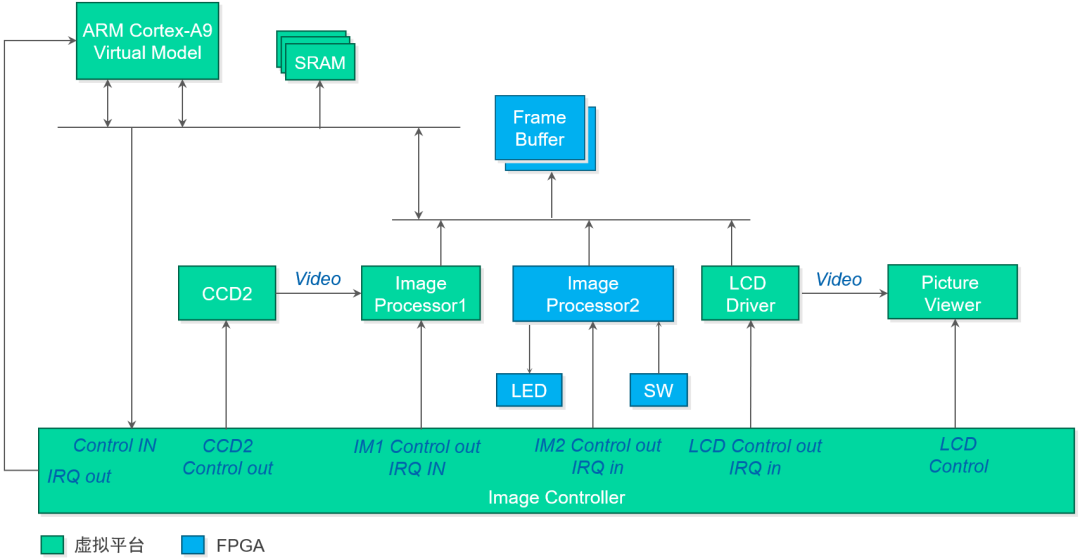

在前面詳細(xì)闡述虛擬平臺(tái)豐富應(yīng)用場(chǎng)景的基礎(chǔ)上,下面通過一個(gè)SW + FPGA開發(fā)板的成功案例,進(jìn)一步展現(xiàn)虛擬平臺(tái)在實(shí)際項(xiàng)目中的強(qiáng)大效能與獨(dú)特價(jià)值。此案例聚焦于圖像處理設(shè)計(jì)領(lǐng)域。該系統(tǒng)中,CPU扮演核心控制角色,精準(zhǔn)調(diào)度硬件資源;內(nèi)存負(fù)責(zé)存儲(chǔ)圖片,為圖像處理提供數(shù)據(jù)基礎(chǔ);而圖像處理器則需頻繁訪問內(nèi)存以獲取并處理圖像數(shù)據(jù)。如此復(fù)雜且緊密協(xié)作的系統(tǒng)架構(gòu),對(duì)驗(yàn)證工作提出極高要求,也凸顯出可擴(kuò)展虛擬平臺(tái)應(yīng)用的必要性。

在圖像處理系統(tǒng)的驗(yàn)證工作中,采用將系統(tǒng)一分為二的創(chuàng)新策略。具體而言,把Image Processor 2部署在FPGA中運(yùn)行,考慮到其需要接收?qǐng)D像數(shù)據(jù),在FPGA內(nèi)部專門設(shè)置Frame Buffer(幀緩沖器),用于臨時(shí)存儲(chǔ)圖像數(shù)據(jù),確保數(shù)據(jù)能夠穩(wěn)定、有序地傳輸給Image Processor 2進(jìn)行處理。系統(tǒng)的其余部分,涵蓋CPU以及各類配套的組件模型,則放置在虛擬原型(VP)中。系統(tǒng)運(yùn)行時(shí),VP會(huì)加載外設(shè)的驅(qū)動(dòng)程序,精準(zhǔn)捕獲原始圖像,并將其傳遞至FPGA開展處理工作。值得一提的是,VP中還集成圖像顯示等功能模塊,開發(fā)人員可直接觀察處理后的圖像情況,極大提升調(diào)試效率。此外,VP中還能集成通過軟件實(shí)現(xiàn)的圖像處理算法,將其作為Image Processor 1。系統(tǒng)運(yùn)行后,以Image Processor 1的處理結(jié)果作為標(biāo)準(zhǔn),與FPGA中Image Processor 2的處理數(shù)據(jù)進(jìn)行對(duì)比,以此驗(yàn)證FPGA處理的正確性。

總結(jié)

思爾芯的Genesis芯神匠Virtual Platform虛擬平臺(tái)憑借其獨(dú)特的搭建方式和廣泛的應(yīng)用場(chǎng)景,在芯片設(shè)計(jì)與驗(yàn)證領(lǐng)域發(fā)揮著不可替代的作用。它不僅為開發(fā)人員提供便捷、高效的開發(fā)環(huán)境,還為芯片的質(zhì)量和性能提供有力保障,推動(dòng)著芯片行業(yè)不斷向前發(fā)展。隨著技術(shù)的不斷進(jìn)步,虛擬平臺(tái)有望在更多領(lǐng)域展現(xiàn)其強(qiáng)大魅力,為芯片設(shè)計(jì)與開發(fā)帶來(lái)更多創(chuàng)新與突破。

-

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1160瀏覽量

56719 -

仿真

+關(guān)注

關(guān)注

55文章

4509瀏覽量

138540 -

思爾芯

+關(guān)注

關(guān)注

0文章

150瀏覽量

1738

發(fā)布評(píng)論請(qǐng)先 登錄

匠芯創(chuàng)ArtInChip 2026年1-2月資訊

思爾芯2025年度成果回溯:拓技術(shù)疆土,促軟硬升級(jí),見生態(tài)成效

思爾芯、MachineWare與Andes晶心科技聯(lián)合推出RISC-V協(xié)同仿真方案,加速芯片開發(fā)

喜遷新址 共赴“芯”程 | 匠芯創(chuàng)深圳分公司喬遷誌慶

匠芯創(chuàng)ArtInChip 2025年12月資訊

思爾芯榮登“國(guó)產(chǎn)EDA工具口碑榜”,以“芯神瞳”原型驗(yàn)證解決方案賦能芯片創(chuàng)新

匠芯創(chuàng)ArtInChip 2025年11月資訊

思爾芯原型驗(yàn)證系統(tǒng)助力昆明湖V2成功啟動(dòng)GUI OpenEuler

“芯”啟杭 創(chuàng)未來(lái) | 匠芯創(chuàng)杭州辦事處盛大開業(yè)

思爾芯亮相2025進(jìn)博會(huì),以數(shù)字EDA解決方案賦能產(chǎn)業(yè)創(chuàng)新

匠芯創(chuàng)ArtInChip 2025年9月資訊

【喜報(bào)】芯神瞳原型驗(yàn)證解決方案榮膺工博會(huì)“集成電路創(chuàng)新成果獎(jiǎng)”

匠芯創(chuàng)ArtInChip 2025年8月資訊

思爾芯超大容量S8-100,簡(jiǎn)化并加速開芯院香山昆明湖16核RISC-V+NOC驗(yàn)證

產(chǎn)學(xué)研融合!思爾芯數(shù)字EDA工具走進(jìn)北航課堂

解鎖思爾芯Genesis芯神匠虛擬原型平臺(tái):混合仿真與多元應(yīng)用實(shí)踐

解鎖思爾芯Genesis芯神匠虛擬原型平臺(tái):混合仿真與多元應(yīng)用實(shí)踐

評(píng)論