低電壓 1:10 LVPECL 可選擇輸入時鐘驅動器 CDCLVP111-EP 深度解析

在電子設計領域,時鐘驅動器的性能優劣對整個系統的穩定性和可靠性起著至關重要的作用。今天,我們就來深入探究 Texas Instruments 公司推出的低電壓 1:10 LVPECL 可選擇輸入時鐘驅動器 CDCLVP111-EP。

文件下載:cdclvp111-ep.pdf

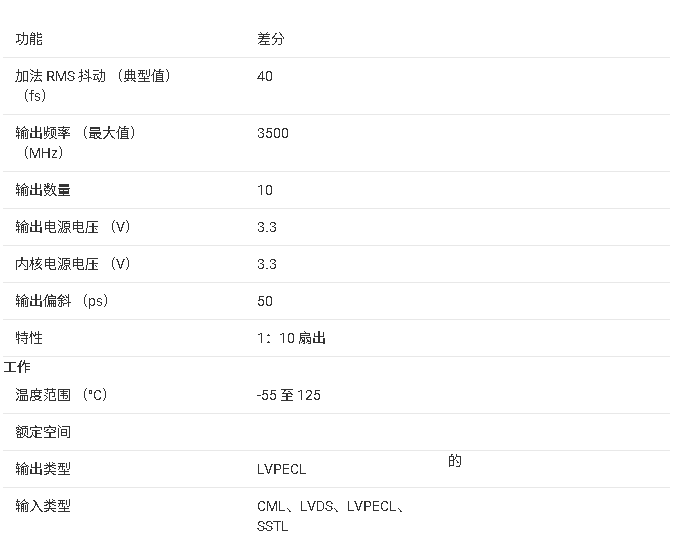

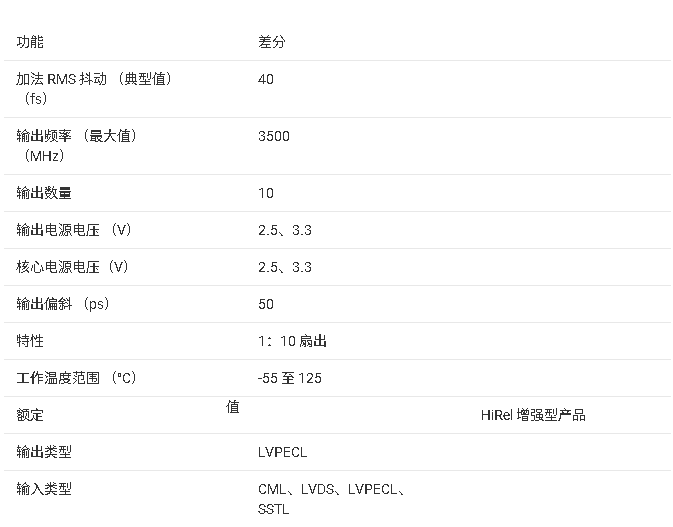

1. 產品特性亮點

信號分配與兼容性

CDCLVP111-EP 能夠將一路差分時鐘輸入對從 LVPECL 轉換并分配到 10 路差分 LVPECL 輸出。這一功能使得它在處理時鐘信號分配時表現出色,而且完全兼容 LVECL 和 LVPECL 標準,大大增強了其在不同電路環境中的適用性。

電源電壓與輸入選擇

該驅動器支持 2.375 V 至 3.8 V 的寬電源電壓范圍,為設計人員在電源配置上提供了更多的靈活性。同時,通過 CLK_SEL 引腳可以實現時鐘輸入的選擇,方便在不同時鐘源之間進行切換。

低輸出偏斜與抖動控制

在時鐘分配應用中,低輸出偏斜是非常關鍵的指標。CDCLVP111-EP 的典型輸出偏斜僅為 15 ps,并且附加抖動小于 1 ps,傳播延遲小于 355 ps。這些優秀的性能指標確保了時鐘信號能夠準確、穩定地傳輸到各個輸出端口。

其他特性

它還提供了 (V_{BB}) 參考電壓輸出,用于單端時鐘操作;具備開放輸入默認狀態,并且與 LVDS、CML、SSTL 輸入兼容。此外,產品采用 32 引腳 LQFP 封裝,頻率范圍從 DC 到 3.5 GHz,還與 MC100 系列等部分產品引腳兼容,方便進行替換和升級。

2. 應用領域廣泛

傳輸線驅動

CDCLVP111-EP 專門設計用于驅動 50 Ω 傳輸線,能夠有效地將時鐘信號傳輸到較遠的距離,并且保持信號的完整性。這在一些需要長距離傳輸時鐘信號的系統中非常有用,比如通信基站和工業自動化設備。

高性能時鐘分配

在高性能時鐘分配系統中,對時鐘信號的精度和穩定性要求極高。該驅動器憑借其低輸出偏斜和抖動控制的優勢,能夠滿足這些嚴苛的要求,確保各個模塊都能接收到準確一致的時鐘信號。

特定領域應用

它還適用于國防、航空航天和醫療等對產品可靠性和性能要求極高的領域。產品具有受控基線、單一組裝和測試地點、單一制造地點等特點,并且可在 -55°C 至 125°C 的軍事溫度范圍內工作,同時具備延長的產品生命周期和產品變更通知,以及產品可追溯性等優勢。

3. 功能與引腳解析

功能選擇

通過 CLK_SEL 引腳可以選擇不同的時鐘輸入。當 CLK_SEL 為 0 時,選擇 CLK0 作為有效時鐘輸入;當 CLK_SEL 為 1 時,選擇 CLK1 作為有效時鐘輸入。

引腳功能

該驅動器的引腳功能明確,CLK0 和 CLK1 為差分 LVECL/LVPECL 輸入對;Q[9:0] 和 Q[9:0] 分別為 LVECL/LVPECL 時鐘輸出和互補時鐘輸出;VBB 為單端輸入操作的參考電壓輸出;VCC 為電源電壓;VEE 為設備接地或 ECL 模式下的負電源電壓。同時,需要注意 CLKn、CLK_SEL 等引腳的上拉和下拉電阻值。

4. 電氣特性分析

絕對最大額定值

在使用 CDCLVP111-EP 時,需要注意其絕對最大額定值,如電源電壓(相對于 VEE)范圍為 -0.3 至 4.6 V,輸入電壓范圍為 -0.3 至 VCC + 0.5 V 等。超過這些額定值可能會對器件造成永久性損壞。

推薦工作條件

推薦的電源電壓(相對于 VEE)范圍為 2.375 至 3.8 V,推薦的工作結溫范圍為 -55°C 至 125°C。在這些條件下使用,能夠確保器件的性能和可靠性。

直流電氣特性

分別介紹了 LVECL 和 LVPECL 模式下的直流電氣特性,包括電源內部電流、輸出和內部電源電流、輸入電流、內部生成的偏置電壓、高低電平輸入電壓、輸入幅度、共模電壓、高低電平輸出電壓以及差分輸出電壓擺幅等參數。這些參數在不同的溫度條件下會有所變化,設計人員需要根據實際應用場景進行合理選擇。

交流電氣特性

交流電氣特性包括差分傳播延遲、輸出到輸出偏斜、部件到部件偏斜、附加相位抖動、最大頻率以及輸出上升和下降時間等。其中,部分規格通過工作臺表征保證,但在生產中不進行測試,設計人員在使用時需要特別關注。

5. 封裝與訂購信息

封裝形式

產品采用 32 引腳 LQFP(VF)封裝,同時提供了封裝的熱阻信息,如熱阻結到環境(θJA)和熱阻結到外殼(θJC)等,這些信息對于散熱設計非常重要。

訂購信息

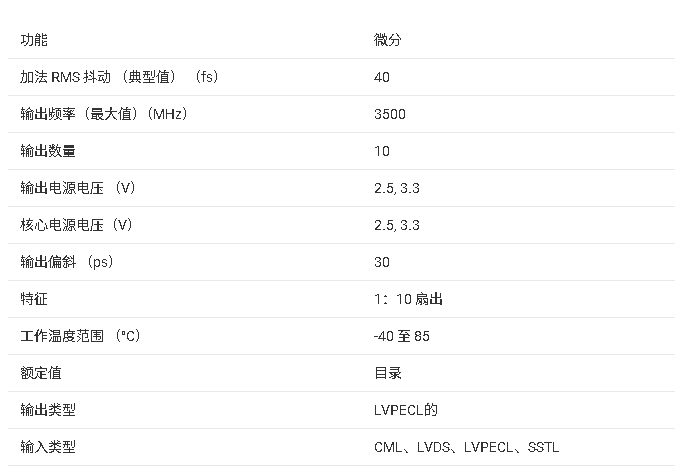

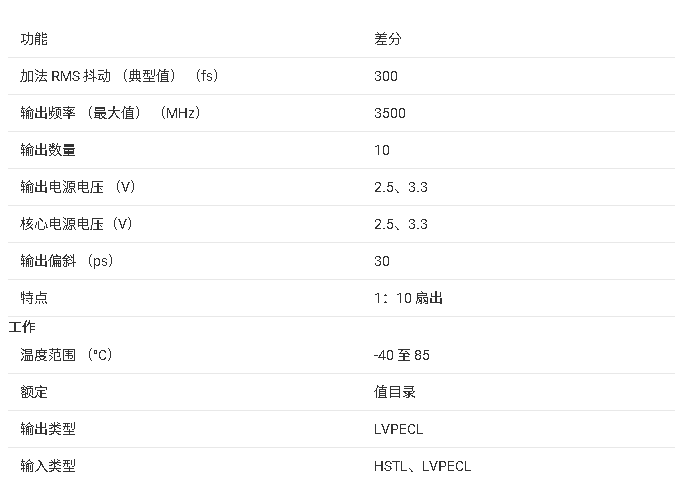

提供了特定溫度范圍(-55°C 至 125°C)下的可訂購部件編號、頂部標記和 VID 編號等信息。同時,還給出了其他合格版本,如目錄版 CDCLVP111 和太空版 CDCLVP111 - SP,它們分別適用于不同的應用場景。

6. 設計注意事項

ESD 保護

由于該器件內置的 ESD 保護有限,在存儲或處理時,應將引腳短路在一起或將器件放置在導電泡沫中,以防止 MOS 柵極受到靜電損壞。

輸出引腳處理

當輸出引腳不使用時,建議將其開路以降低功耗。如果只使用差分對中的一個輸出引腳,則另一個輸出引腳必須同樣端接到 50 Ω。

工作模式選擇

對于高達 3.5 GHz 的高速性能,強烈建議使用差分模式。如果需要單端輸入操作,則使用 (V_{BB}) 參考電壓輸出,并將 VBB 引腳連接到 CLK0 并通過 10-nF 電容器旁路到 GND。

CDCLVP111-EP 作為一款高性能的時鐘驅動器,具備多種優秀的特性和廣泛的應用領域。電子工程師在進行硬件設計時,需要充分了解其特性和參數,結合實際應用場景進行合理設計和選擇,以確保系統的穩定性和可靠性。大家在使用這款驅動器的過程中遇到過哪些問題呢?歡迎在評論區分享交流。

-

電子設計

+關注

關注

42文章

1681瀏覽量

49848 -

時鐘驅動器

+關注

關注

0文章

122瀏覽量

14382

發布評論請先 登錄

CDCLVP111-SP CDCLVP111-SP 具有可選輸入時鐘驅動器的低電壓 1:10 LVPECL

CDCLVP111-EP 具有可選輸入的 1:10 LVPECL 緩沖器

CDCLVP111-SP具有可選輸入時鐘驅動器的低電壓1:10 LVPECL數據表

CDCLVP111低壓1:10 LVPECL,內置可選輸入時鐘驅動器數據表

低電壓 1:10 LVPECL 可選擇輸入時鐘驅動器 CDCLVP111-EP 深度解析

低電壓 1:10 LVPECL 可選擇輸入時鐘驅動器 CDCLVP111-EP 深度解析

評論