CDCLVP111時鐘驅動器分配一個差分時鐘對的LVPECL輸入, (CLK0、CLK1)至10對差分LVPECL時鐘(Q0、Q9)輸出,時鐘偏移最小 分配。該CDCLVP111可以接受兩個時鐘源進入輸入多路復用器。The CDCLVP111 專為驅動 50 Ω輸電線路而設計。當不使用輸出引腳時, 建議將其打開以降低功耗。如果只有一個輸出引腳來自 使用差分對時,另一個輸出引腳必須相同端接至 50 Ω。

*附件:cdclvp111.pdf

V 型BB型如果單端輸入,則使用參考電壓輸出 需要作。在這種情況下,VBB型引腳應連接到 CLK0 并通過 10-nF 電容器旁路到 GND。

然而,對于高達 3.5 GHz 的高速性能,差分模式很強 推薦。

CDCLVP111器件的工作溫度范圍為–40°C至85°C。

特性

- 將一個差分時鐘輸入對

LVPECL分配到10個差分LVPECL - 與 LVECL 和 LVPECL 完全兼容

- 支持2.375 V至3.8 V的

寬電源電壓范圍 - 通過CLK_SEL可選擇時鐘輸入

- 用于時鐘分配應用的低輸出偏斜(典型值15 ps)

- 附加抖動小于 1 ps

- 傳播延遲小于350 ps

- 打開輸入默認狀態(Open Input Default State)

- 兼容 LVDS、CML、SSTL 輸入

- V

BB型用于單端時鐘的基準電壓輸出 - 采用32引腳LQFP和QFN封裝

- 頻率范圍從直流到3.5 GHz

- 與 MC100 系列 EP111、ES6111、

LVEP111 PTN1111 引腳兼容 - 應用

- 專為驅動 50 Ω輸電線路而設計

- 高性能時鐘分配

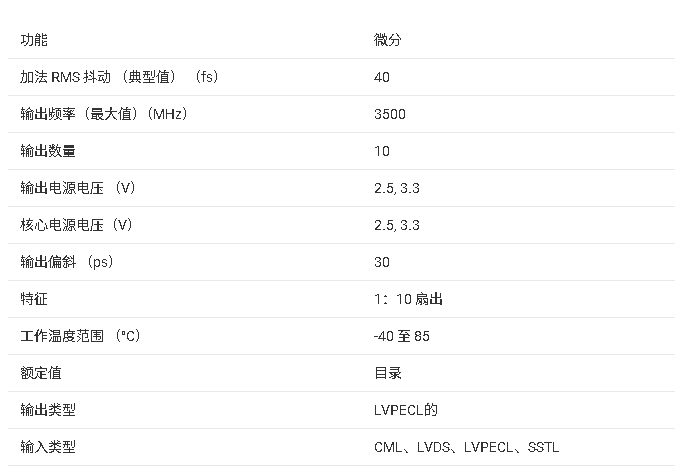

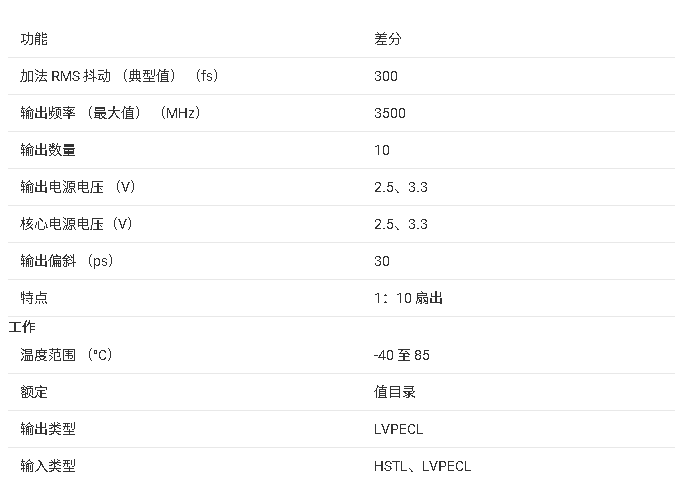

參數

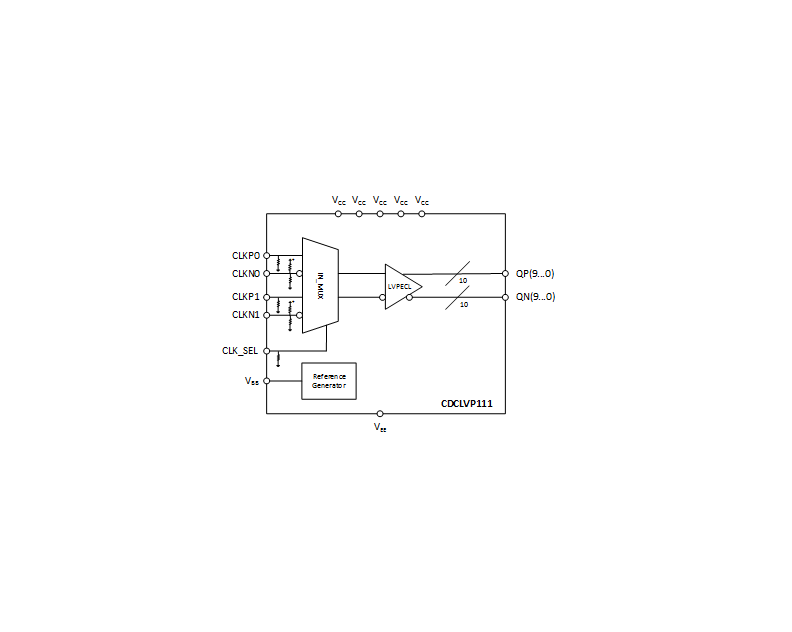

方框圖

?1. 核心特性?

- ?高性能時鐘分配?:支持1路差分LVPECL輸入轉換為10路差分LVPECL輸出,輸出偏斜低至15 ps(典型值)。

- ?寬電壓范圍?:工作電壓2.375 V至3.8 V,兼容LVECL/LVPECL標準。

- ?低抖動設計?:附加相位抖動小于1 ps,傳播延遲低于350 ps,頻率范圍覆蓋DC至3.5 GHz。

- ?靈活輸入選擇?:通過CLK_SEL引腳選擇兩路差分輸入(CLK0/CLK1),支持LVDS、CML、SSTL輸入兼容。

- ?熱管理優化?:提供32引腳LQFP和QFN封裝,集成散熱焊盤(PowerPAD)以提升散熱性能。

?2. 關鍵應用場景?

?3. 功能描述?

- ?輸入處理?:內置多路復用器支持兩路差分輸入切換,VBB引腳提供單端輸入參考電壓(需外接10 nF電容接地)。

- ?輸出配置?:未使用的輸出建議懸空以降低功耗;若僅使用差分對中單端,需通過50 Ω終端匹配。

?4. 電氣參數?

- ?電源電流?:典型值380 mA(全負載,3.3 V供電)。

- ?輸入靈敏度?:差分輸入幅度(VID)最小0.5 V,支持100 mV容限。

- ?溫度范圍?:-40°C至85°C,結溫上限110°C。

?5. 設計建議?

- ?布局與散熱?:推薦PCB布局中為散熱焊盤添加多通孔至地平面,確保熱阻(RθJA)優化。

- ?電源濾波?:每個電源引腳就近放置0.1 μF去耦電容,建議串聯鐵氧體磁珠抑制高頻噪聲。

?6. 封裝與訂購信息?

- ?封裝選項?:32引腳VQFN(5×5 mm)和LQFP(7×7 mm)。

- ?環保認證?:符合RoHS標準,提供無鉛(NIPDAU)焊盤處理。

?7. 文檔支持?

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

輸電線路

+關注

關注

1文章

812瀏覽量

24542 -

引腳

+關注

關注

16文章

2115瀏覽量

55948 -

多路復用器

+關注

關注

9文章

1061瀏覽量

66823 -

LVPECL

+關注

關注

2文章

75瀏覽量

18883 -

時鐘驅動器

+關注

關注

0文章

124瀏覽量

14404

發布評論請先 登錄

相關推薦

熱點推薦

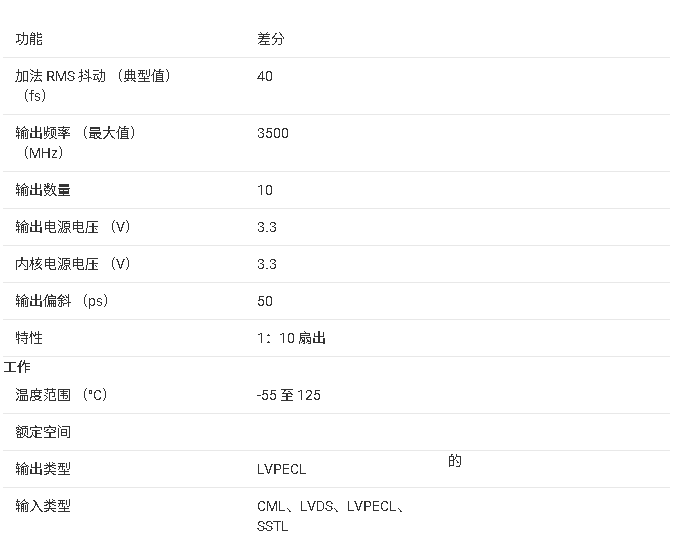

CDCLVP111-SP具有可選輸入時鐘驅動器的低電壓1:10 LVPECL數據表

電子發燒友網站提供《CDCLVP111-SP具有可選輸入時鐘驅動器的低電壓1:10 LVPECL

發表于 08-20 09:15

?0次下載

CDCLVP111低壓1:10 LVPECL,內置可選輸入時鐘驅動器數據表

電子發燒友網站提供《CDCLVP111低壓1:10 LVPECL,內置可選輸入時鐘驅動器數據表.pdf》資料免費下載

發表于 08-21 11:37

?0次下載

CDCVF111 1:9差分LVPECL時鐘驅動器數據表

電子發燒友網站提供《CDCVF111 1:9差分LVPECL時鐘驅動器數據表.pdf》資料免費下載

發表于 08-21 09:13

?0次下載

深入解析CDCLVP111-SEP:低電壓1:10 LVPECL時鐘驅動器

深入解析CDCLVP111-SEP:低電壓1:10 LVPECL時鐘驅動器 在電子設計領域,

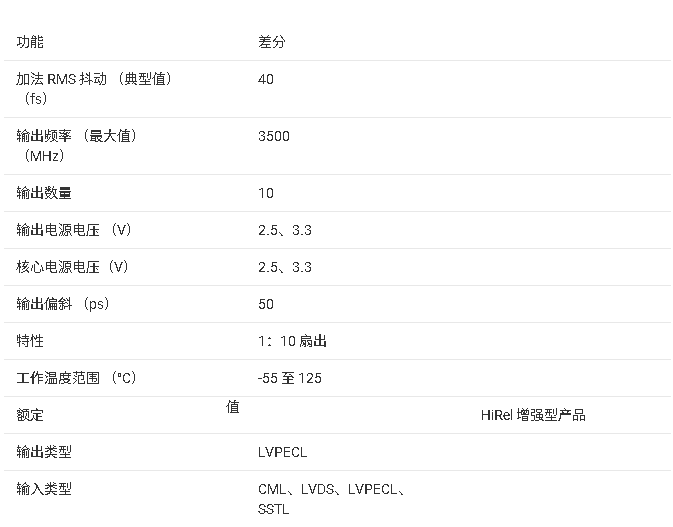

低電壓 1:10 LVPECL 可選擇輸入時鐘驅動器 CDCLVP111-EP 深度解析

低電壓 1:10 LVPECL 可選擇輸入時鐘驅動器 CDCLVP111-EP 深度解析 在電子

CDCLVP111:高性能低電壓時鐘驅動器的卓越之選

低電壓1:10 LVPECL(低壓正發射極耦合邏輯)時鐘驅動器,看看它在實際應用中能為我們帶來哪些優勢。 文件下載:

深入剖析 CDCLVP215:低電壓雙差分 1:5 LVPECL 時鐘驅動器

深入剖析 CDCLVP215:低電壓雙差分 1:5 LVPECL 時鐘驅動器 在電子設計領域,時鐘驅動器

?CDCLVP111 低電壓1:10 LVPECL時鐘驅動器技術文檔總結

?CDCLVP111 低電壓1:10 LVPECL時鐘驅動器技術文檔總結

評論