0 引言

在后摩爾定律的時(shí)代背景下,通過(guò)傳統(tǒng)的縮小晶體管尺寸的方式來(lái)提高集成度變得非常困難。現(xiàn)在的電子系統(tǒng)正朝著小型化、多樣化、智能化的方向發(fā)展,并最終形成具有感知、通信、處理、傳輸?shù)裙δ艿奈⑾到y(tǒng)。微系統(tǒng)的核心技術(shù)是集成,正在由平面集成向三維集成、由芯片級(jí)向集成度和復(fù)雜度更高的系統(tǒng)集成發(fā)展。近年來(lái),半導(dǎo)體工藝技術(shù)快速發(fā)展,不僅體現(xiàn)在射頻、模擬、混合信號(hào)等傳統(tǒng)的半導(dǎo)體工藝,還體現(xiàn)在系統(tǒng)的異質(zhì)集成等非傳統(tǒng)的半導(dǎo)體工藝。

1 異質(zhì)集成

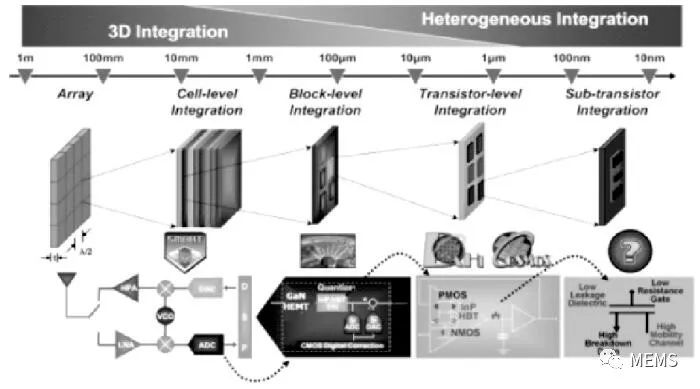

美國(guó)國(guó)防部高級(jí)研究計(jì)劃局(DARPA)在1990年代末率先提出了異質(zhì)集成的概念,并勾畫(huà)出異質(zhì)集成的發(fā)展方向,如圖1所示。異質(zhì)集成可以集成的器件有:射頻/模擬電子系統(tǒng)中的雙極器件(SiGe和Ⅲ-Ⅴ族 HBT)、低頻模數(shù)混合信號(hào)系統(tǒng)中的CMOS器件、MEMS/NEMS等機(jī)械量檢測(cè)器件、光電/電光轉(zhuǎn)換器件等。

圖1 DARPA提出的三維集成和異質(zhì)集成計(jì)劃

異質(zhì)集成可以分為混合集成和單片集成。混合集成是將不同襯底材料的芯片通過(guò)鍵合實(shí)現(xiàn)的集成方式。它的代表技術(shù)是三維芯片堆疊,類似于系統(tǒng)級(jí)封裝(SiP)的概念。單片集成是將各種不同功能的器件在單芯片上集成,省去了這些芯片的封裝,但工藝制造難度較大。單片異質(zhì)集成類似于片上系統(tǒng)(SoC)的概念,是工業(yè)界和學(xué)術(shù)界的研究熱點(diǎn)之一。可以預(yù)見(jiàn),單片異質(zhì)集成技術(shù)將有較大的發(fā)展空間。

2 單片異質(zhì)集成

國(guó)外在異質(zhì)集成方面的研究主要為單片異質(zhì)集成:Si基CMOS微電子器件、Ⅲ-Ⅴ族微電子器件、Ⅲ-Ⅴ族光電子器件和MEMS器件等。Si基CMOS器件與Ⅲ-Ⅴ族器件的結(jié)合可以充分發(fā)揮各自的技術(shù)優(yōu)勢(shì),實(shí)現(xiàn)單一器件無(wú)法達(dá)到的性能。單片異質(zhì)集成通常采用類似post-CMOS工藝的方法,首先制作Si基CMOS器件,然后進(jìn)行Ⅲ-Ⅴ族器件的制作以及二者之間的互聯(lián)。這種方法的優(yōu)點(diǎn)是Si基CMOS器件與Ⅲ-Ⅴ族器件的制作工藝相對(duì)獨(dú)立,制作Ⅲ-Ⅴ族器件時(shí)不會(huì)對(duì)已經(jīng)完成的CMOS器件產(chǎn)生影響,采用Si材料作為襯底可以有效降低成本。

2.1 Si基CMOS和Ⅲ-Ⅴ族微電子器件

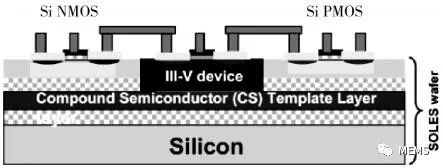

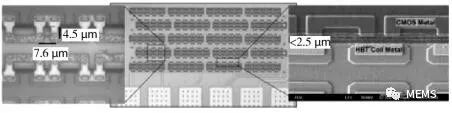

美國(guó)雷神公司在Ⅲ-Ⅴ族與Si基CMOS器件的異質(zhì)集成方面進(jìn)行了較多的 研究。該公司在2010年實(shí)現(xiàn)了在Si襯底上集成InP HBT和Si基CMOS器件,如圖2所示。這種單片異質(zhì)集成方法基于美國(guó)麻省理工學(xué)院提出的SOLES工藝。SOLES工藝包括一個(gè)由Ⅲ-Ⅴ族化合物構(gòu)成的模板層(template layer),在這個(gè)模板層上直接外延生長(zhǎng)高質(zhì)量的Ⅲ-Ⅴ族器件。SOLES工藝的模板層兼容標(biāo)準(zhǔn)的Si基CMOS工藝,但后續(xù)Ⅲ-Ⅴ族器件的制作并不與標(biāo)準(zhǔn)CMOS工藝兼容,需要額外的Ⅲ-Ⅴ族工藝配合完成。圖3給出了異質(zhì)集成的CMOS-InP HBT器件的掃描電子SEM照片,可以看到兩種器件的間隔只有2.5μm,顯示出較高的集成度。雷神公司采用這種工藝實(shí)現(xiàn)了一種單位增益帶寬積高達(dá)20GHz的差分放大器和一種13位500MHz帶寬的高速高精度DAC,與傳統(tǒng)的InP襯底下同質(zhì)外延生長(zhǎng)和加工的HBT管相比,電學(xué)性能相當(dāng)。

圖2 雷神公司基于SOLES工藝的Si基CMOS器件與Ⅲ-Ⅴ族器件的異質(zhì)集成

圖3 雷神公司異質(zhì)集成的CMOS-InP HBT器件的SEM照片

2011年,雷神公司采用相同的方法,實(shí)現(xiàn)了GaN HEMT和Si基CMOS器件的異質(zhì)集成,但仍然存在不足:1)只能在小尺寸(100mm)的晶圓上實(shí)現(xiàn);2)需要兩種制造工藝,Si基CMOS器件的制造在Si代工廠完成,而GaN HEMT以及后續(xù)的互聯(lián)工藝需要在Ⅲ-Ⅴ族代工廠完成。之后,研究人員采用一些方法解決了上述問(wèn)題。比如,在200mm的Si襯底上采用分子束外延方法(MBE)外延生長(zhǎng)GaN。相比于標(biāo)準(zhǔn)金屬有機(jī)化學(xué)氣相外延(MOCVD)生長(zhǎng)技術(shù),MBE外延技術(shù)的優(yōu)點(diǎn)是所需的溫度較低,由高溫導(dǎo)致Si基CMOS器件性能退化的影響變小,還可提高GaN管的射頻性能。另外,傳統(tǒng)的GaN器件的歐姆接觸采用金屬Au,與Si基CMOS工藝不兼容。還有些研究人員則采用Ti/Al/W的歐姆接觸,實(shí)現(xiàn)了在Si基代工廠完成GaN器件的代工。

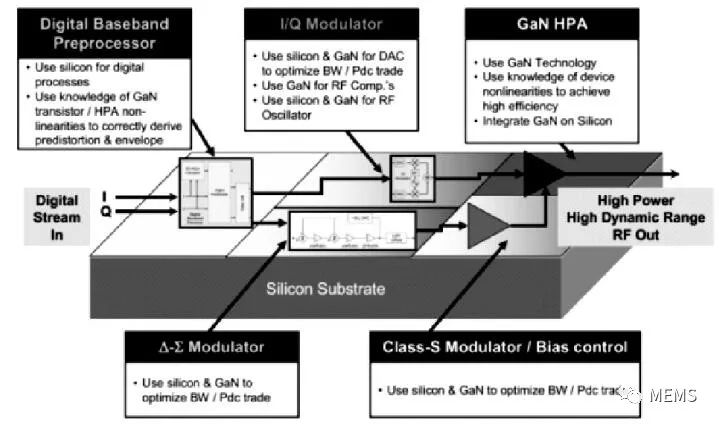

在實(shí)現(xiàn)Si基CMOS器件與GaN HEMT器件的單片異質(zhì)集成后,雷神公司進(jìn)一步實(shí)現(xiàn)了單片發(fā)射機(jī)芯片,在一個(gè)芯片上集成了數(shù)字基帶處理器、高線性度功率放大器、高輸出功率DAC、射頻發(fā)射機(jī)等,如圖4所示。該發(fā)射機(jī)芯片證明了單片異質(zhì)集成技術(shù)在射頻、混合信號(hào)、數(shù)字電路等領(lǐng)域具有巨大的應(yīng)用潛力。

圖4 雷神公司采用單片異質(zhì)集成技術(shù)實(shí)現(xiàn)的線性化發(fā)射機(jī)

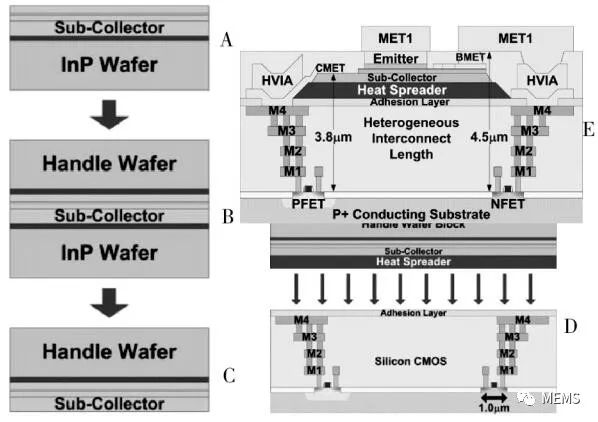

美國(guó)HRL公司也對(duì)單片異質(zhì)集成進(jìn)行了大量的研究。與雷神公司直接在模板層上異質(zhì)集成外延Ⅲ-Ⅴ族材料的方法不同,HRL公司通過(guò)兩種器件襯底材料的直接鍵合實(shí)現(xiàn)芯片晶圓級(jí)的異質(zhì)集成。工藝步驟如圖5所示,先在InP晶圓上外延生長(zhǎng)InP DHBT外延層,隨后刻蝕掉InP襯底,將Si基與InP進(jìn)行晶圓級(jí)鍵合,然后刻蝕制作出InP器件并與Si基CMOS器件互聯(lián),最終實(shí)現(xiàn)250nm InP DHBT工藝與130nm RF CMOS工藝的單片異質(zhì)集成。單片異質(zhì)集成后的工藝可以稱為InP BiCMOS工藝。2014年,HRL公司又分別將40nm GaN HEMT工藝和250nm InP HBT工藝與65nm CMOS工藝進(jìn)行了單片異質(zhì)集成。

圖5 HRL公司的InP DHBT和CMOS工藝異質(zhì)集成

2.2 Si基CMOS微電子器件和Ⅲ-Ⅴ族光電子器件、MEMS器件

光電子器件在超高速信號(hào)傳輸上的獨(dú)特優(yōu)勢(shì)使得光電集成技術(shù)具有較好的應(yīng)用前景。Si是間接帶隙材料,發(fā)光效率較低,不適合用作高效的發(fā)光器件。而Ⅲ-Ⅴ族化合物屬于直接帶隙材料,易于發(fā)射和吸收光。因此,將Ⅲ-Ⅴ族材料制造的光源和Si材料制造的微電子器件集成在一起,就可以實(shí)現(xiàn)Si基單片光電集成電路。

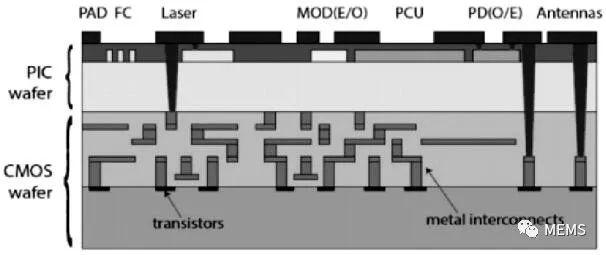

與成熟的Si基電子器件相比,Ⅲ-Ⅴ族光電集成電路(Photonic Integrated Circuits,PIC)仍然處于發(fā)展階段。2016年,荷蘭埃因霍溫理工大學(xué)的研究人員在60GHz毫米波頻率下,采用OTTD(Optical True Time Delay)的波束控制技術(shù)實(shí)現(xiàn)了相控陣列毫米波收發(fā)系統(tǒng),并采用片上集成天線(Antenna-on-Chip,AoC)技術(shù),將天線與電子器件互聯(lián)的損耗最小化。采用光傳輸?shù)牟ㄊ刂萍夹g(shù)具有超寬頻帶和低損耗等優(yōu)點(diǎn)。PIC電路主要包括InP材料實(shí)現(xiàn)的激光器和光電二極管。

圖6給出了單芯片上集成CMOS器件、光電集成電路以及片上天線等的器件結(jié)構(gòu)圖。首先,獨(dú)立制作CMOS和PIC晶圓,并將PIC晶圓粘合在CMOS晶圓之上,然后將天線部分制作在PIC晶圓之上,最后加入CMOS器件、PIC電路和天線三者之間的互連線。圖6中,F(xiàn)C為光纖耦合器,MOD為電光調(diào)制器,PCU為光子控制單元,PD為光電二極管。

圖6 單芯片集成CMOS器件、光電集成電路、片上天線

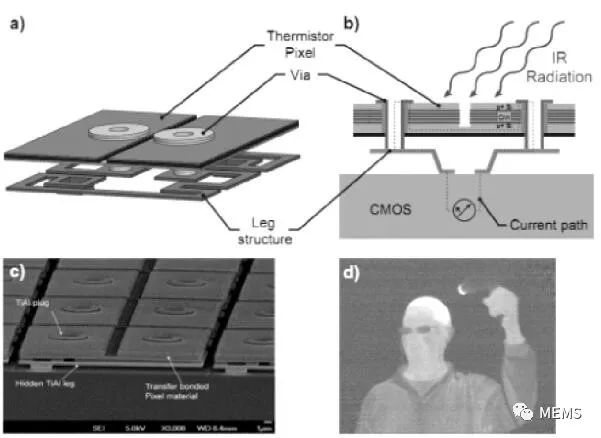

MEMS器件近年來(lái)也有了長(zhǎng)足的發(fā)展,其主要發(fā)展方向是兼容Si基CMOS工藝。2016年,瑞典皇家理工學(xué)院微納系統(tǒng)實(shí)驗(yàn)室的研究人員實(shí)現(xiàn)了微測(cè)熱輻射計(jì)陣列(由Si/SiGe量子阱熱敏電阻單元構(gòu)成)和標(biāo)準(zhǔn)CMOS工藝實(shí)現(xiàn)的讀出電路的單片異質(zhì)集成,如圖7所示。圖7給出了單個(gè)像素的微測(cè)熱輻射計(jì)的原理圖和微測(cè)熱輻射計(jì)陣列的SEM照片。

圖7 輻射熱測(cè)量器陣列和CMOS讀出電路的異質(zhì)集成

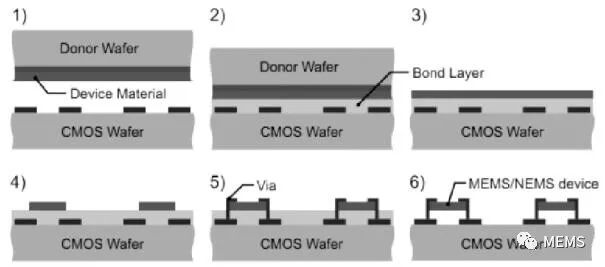

在工藝制造中,Si/SiGe量子阱熱敏電阻制作工藝的溫度超過(guò)了CMOS電子器件制作工藝的溫度。因此,Si/SiGe量子阱熱敏電阻器件首先被制作于SOI晶圓上,隨后被轉(zhuǎn)移到CMOS晶圓上,然后將SOI晶圓的襯底去除,刻蝕出器件,并制作通孔,實(shí)現(xiàn)CMOS與MEMS器件的互連,最終完成單片異質(zhì)集成工藝。工藝步驟如圖8所示。

圖8 CMOS器件和MEMS器件單片異質(zhì)集成工藝步驟

2.3 國(guó)內(nèi)研究進(jìn)展

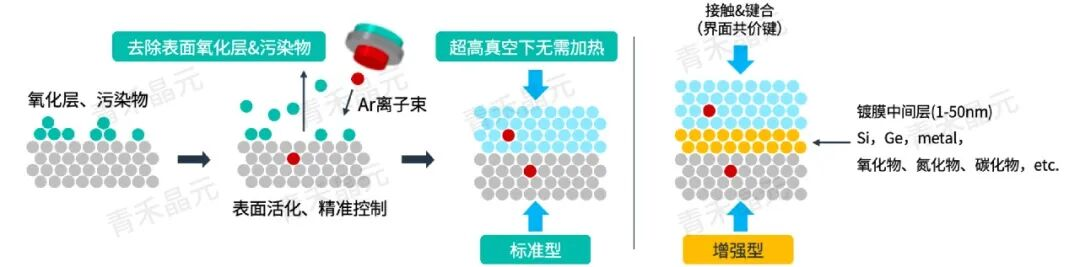

國(guó)內(nèi)已有不少研究機(jī)構(gòu)和公司開(kāi)展異質(zhì)集成技術(shù)方面的研究,但大多數(shù)仍處于起步階段。國(guó)內(nèi)研究以異質(zhì)外延為主,即在Si襯底上直接外延生長(zhǎng)Ⅲ-Ⅴ族化合物。但Ⅲ-Ⅴ族化合物與Si之間存在較大的晶格失配和熱失配,很難得到高質(zhì)量的外延層,器件的可靠性較低。如何解決異質(zhì)材料之間的晶格失配也是近年來(lái)的研究熱點(diǎn)之一。比如,有學(xué)者提出低溫晶片鍵合的方法,可廣泛應(yīng)用于光電子器件、微機(jī)械智能系統(tǒng)和三維器件等。

2015年,南京電子器件研究所的吳立樞等人基于外延層剝離轉(zhuǎn)移、異類器件互聯(lián)等技術(shù),實(shí)現(xiàn)了GaAs pHEMT與Si基CMOS器件異質(zhì)集成的單片電路。最終實(shí)現(xiàn)的單片數(shù)字控制開(kāi)關(guān)電路與傳統(tǒng)的GaAs pHEMT單片電路相比,芯片面積減小了15%。該異質(zhì)集成電路如圖9所示。

圖9 異質(zhì)集成電路FIB截面圖

3 面臨的挑戰(zhàn)

國(guó)內(nèi)外異質(zhì)集成技術(shù)雖然有了長(zhǎng)足的發(fā)展,但由于技術(shù)較為復(fù)雜,仍然需要克服很多問(wèn)題才能實(shí)現(xiàn)大規(guī)模的應(yīng)用。本文列出了幾個(gè)關(guān)鍵的問(wèn)題。

(1)技術(shù)限制。異質(zhì)集成的工藝還不完善,尤其是單片異質(zhì)集成,雖然目前已能實(shí)現(xiàn),但尚未進(jìn)行大規(guī)模量產(chǎn)。異質(zhì)集成涉及的工藝步驟多且復(fù)雜,對(duì)工藝精度要求較高,同時(shí)對(duì)能夠異質(zhì)集成的器件也有一定的約束。量產(chǎn)后的產(chǎn)品良率還有待進(jìn)一步驗(yàn)證。

(2)三維互連技術(shù)。異質(zhì)器件的集成需要采用三維互聯(lián)中的硅通孔(TSV)技術(shù)。基于TSV工藝的三維集成可以實(shí)現(xiàn)短且密的層間互聯(lián),有效縮短了互連線長(zhǎng)度。但是TSV工藝較復(fù)雜,是易受到制造缺陷影響的敏感工藝。另外,一個(gè)芯片上的TSV數(shù)目較多,一個(gè)TSV的損壞會(huì)導(dǎo)致整個(gè)芯片損壞。因此,需要研究TSV工藝的故障機(jī)理,并提出降低故障概率的方法。

(3)異質(zhì)集成芯片的測(cè)試技術(shù)。測(cè)試技術(shù)是異質(zhì)集成面臨的主要挑戰(zhàn)之一。異質(zhì)集成芯片的集成度遠(yuǎn)高于二維芯片,但芯片的封裝引腳數(shù)量基本與二維芯片相同,因此,分配給每個(gè)電路模塊的測(cè)試引腳數(shù)相對(duì)變少,芯片的可控制性、可觀察性均有所降低,測(cè)試難度增大。

(4)散熱和可靠性問(wèn)題。Ⅲ-Ⅴ族化合物的一個(gè)重要應(yīng)用環(huán)境是高輸出功率放大器。異質(zhì)集成技術(shù)提高了芯片的集成度,在十分有限的芯片面積下集成多種器件后,散熱問(wèn)題就顯得尤為重要。在可靠性方面,需要對(duì)材料的性能、退化和失效機(jī)理作進(jìn)一步研究,以建立有效的、多種物理、多尺度模型來(lái)準(zhǔn)確預(yù)測(cè)失效的發(fā)生,提高芯片的可靠性。

(5)軟件和工藝PDK文件支持。軟件在集成電路制作中的作用越來(lái)越大。在器件級(jí)、芯片晶圓級(jí)和子系統(tǒng)級(jí)的設(shè)計(jì)、仿真、加工和驗(yàn)證方面,需要一套完整的、EDA軟件支持的解決方案。同時(shí),新器件的研發(fā)需要代工廠商配套開(kāi)發(fā)相應(yīng)的PDK文件。

4 總結(jié)

現(xiàn)代微系統(tǒng)技術(shù)正從二維集成到三維集成、從微電子/光電集成到異質(zhì)集成、從結(jié)構(gòu)/電氣一體化到多功能一體化集成等方向發(fā)展。異質(zhì)集成技術(shù)作為超越摩爾定律發(fā)展的重要手段之一,已從多種不同材料芯片的二維/三維集成發(fā)展到同一襯底上集成多種不同材料、不同結(jié)構(gòu)的器件,并實(shí)現(xiàn)了不同工藝器件的一體化互連。國(guó)外在單片異質(zhì)集成方面的研究多集中在Si基CMOS器件與Ⅲ-Ⅴ族器件的異質(zhì)集成,可以利用器件各自的優(yōu)勢(shì)在單芯片上集成射頻、混合信號(hào)系統(tǒng)中的CMOS器件、MEMS/NEMS器件、光電/電光轉(zhuǎn)換器件等,實(shí)現(xiàn)片上子系統(tǒng),但仍存在量產(chǎn)的良率較低、芯片散熱能力有限、可靠性較低等問(wèn)題。

-

芯片

+關(guān)注

關(guān)注

463文章

54007瀏覽量

465903 -

mems

+關(guān)注

關(guān)注

129文章

4475瀏覽量

198778 -

微電子

+關(guān)注

關(guān)注

18文章

413瀏覽量

42860

原文標(biāo)題:?jiǎn)纹愘|(zhì)集成技術(shù)研究現(xiàn)狀與進(jìn)展

文章出處:【微信號(hào):MEMSensor,微信公眾號(hào):MEMS】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

青禾晶元常溫鍵合方案,破解第三代半導(dǎo)體異質(zhì)集成熱損傷難題

CoWoS產(chǎn)能狂飆的背后:異質(zhì)集成芯片的“最終測(cè)試”新范式

【原理到實(shí)戰(zhàn)】實(shí)驗(yàn)異質(zhì)性分析

【2025九峰山論壇】破局摩爾定律:異質(zhì)異構(gòu)集成如何撬動(dòng)新賽道?

MEMS加速度計(jì)與石英加速度計(jì)的發(fā)展現(xiàn)狀與水平對(duì)比

中國(guó)芯片發(fā)展現(xiàn)狀和趨勢(shì)2025

鋁電解電容的行業(yè)發(fā)展現(xiàn)狀與未來(lái)趨勢(shì)展望

臺(tái)階儀應(yīng)用 | 半導(dǎo)體GaAs/Si異質(zhì)外延層表面粗糙度優(yōu)化

RISC-V 發(fā)展現(xiàn)狀及未來(lái)發(fā)展重點(diǎn)

國(guó)產(chǎn)功分器行業(yè)發(fā)展現(xiàn)狀

AI在醫(yī)療健康和生命科學(xué)中的發(fā)展現(xiàn)狀

功率半導(dǎo)體與集成技術(shù):開(kāi)啟能源與智能新紀(jì)元

工業(yè)電機(jī)行業(yè)現(xiàn)狀及未來(lái)發(fā)展趨勢(shì)分析

新能源汽車(chē)驅(qū)動(dòng)電機(jī)專利信息分析

最新議程出爐! | 2025異質(zhì)異構(gòu)集成封裝產(chǎn)業(yè)大會(huì)(HIPC 2025)

單片異質(zhì)集成的發(fā)展現(xiàn)狀

單片異質(zhì)集成的發(fā)展現(xiàn)狀

評(píng)論