電子發燒友網報道(文/梁浩斌)博通最近推出了3.5D XDSiP的芯片封裝平臺技術,面向下一代高性能AI、HPC應用的定制XPU和ASIC。3.5D XDSiP的最大亮點,在于可以將超過6000平方毫米的3D堆疊硅晶片和12個HBM模塊集成到一個系統級封裝中。這是什么概念?

目前手機移動端的旗艦處理器驍龍8Elite核心面積是124.1平方毫米;英偉達H200核心面積1526平方毫米;今年英偉達推出的首款Blackwell架構GPU B200,采用雙die合封,核心面積也達到1600平方毫米左右。也就是說博通的3.5D XDSiP平臺,可以支持近4個B200核心集成在一個封裝中。

那么這么“巨大”的芯片是怎么封裝的,市場上真的需要這么大規模的芯片嗎?

2.5D封裝、3D堆棧、F2F堆疊結合,首批產品2026上市

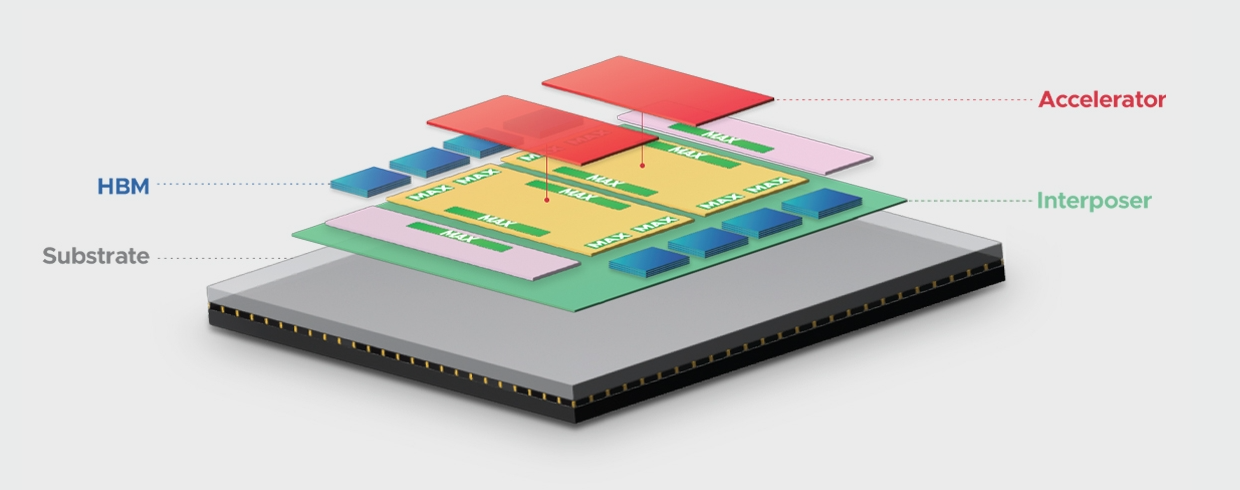

圖源:博通

隨著摩爾定律的進一步減緩,先進封裝在大規模計算集群中XPU上的應用已經成為了業界共識,在AI計算中,XPU需要計算、內存、I/O等功能的復雜集成,以最大限度地降低功耗和成本。

而博通的3.5D XDSiP平臺,作為用于定制計算芯片的平臺,優勢主要包括:

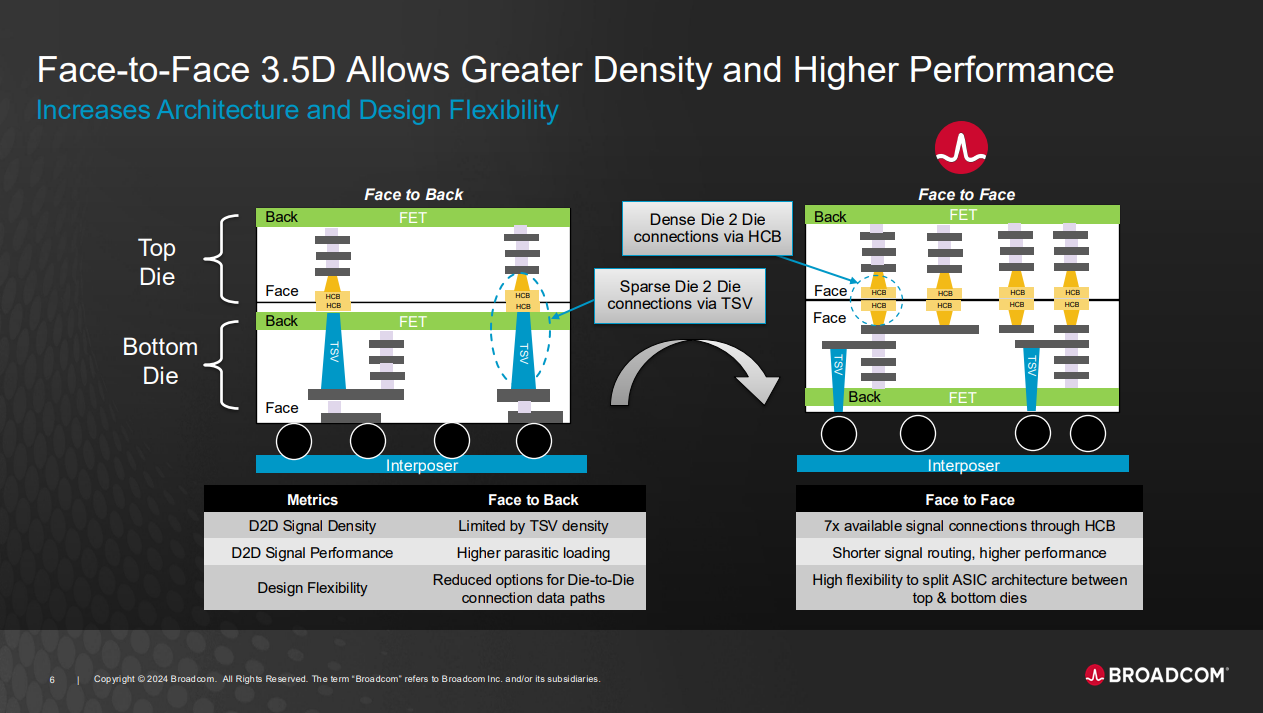

圖源:博通

增強的互連密度:與傳統采用硅通孔TVS的F2B(面到背)的技術相比,3.5D XDSiP采用HCB(混合銅鍵合)以F2F(面對面)的方式將邏輯芯片堆疊,堆疊芯片之間的信號密度提高了7倍;

高能效:通過利用3D HCB代替平面芯片到芯片物理接口,芯片到芯片接口的功耗降低了90%;

低延遲:最大限度地減少3D堆棧中計算、內存和I/O組件之間的延遲;

小尺寸:支持更小的轉接板和封裝尺寸,從而節省成本并改善封裝翹曲。

這項封裝技術是博通與臺積電多年合作的成果,博通ASIC產品部高級副總裁兼總經理Frank Ostojic表示:“隨著我們達到摩爾定律的極限,先進封裝對于下一代XPU集群至關重要。通過與我們的客戶密切合作,我們在臺積電和EDA合作伙伴的技術和工具基礎上創建了一個3.5D XDSiP平臺。通過垂直堆疊芯片組件,Broadcom的3.5D平臺使芯片設計師能夠為每個組件配對正確的制造工藝,同時縮小插入器和封裝尺寸,從而顯著提高性能、效率和成本。”

臺積電業務發展高級副總裁張曉強博士表示,臺積電和博通在過去幾年中密切合作,將臺積電最先進的邏輯處理和3D芯片堆疊技術與博通的設計專業知識結合在一起。

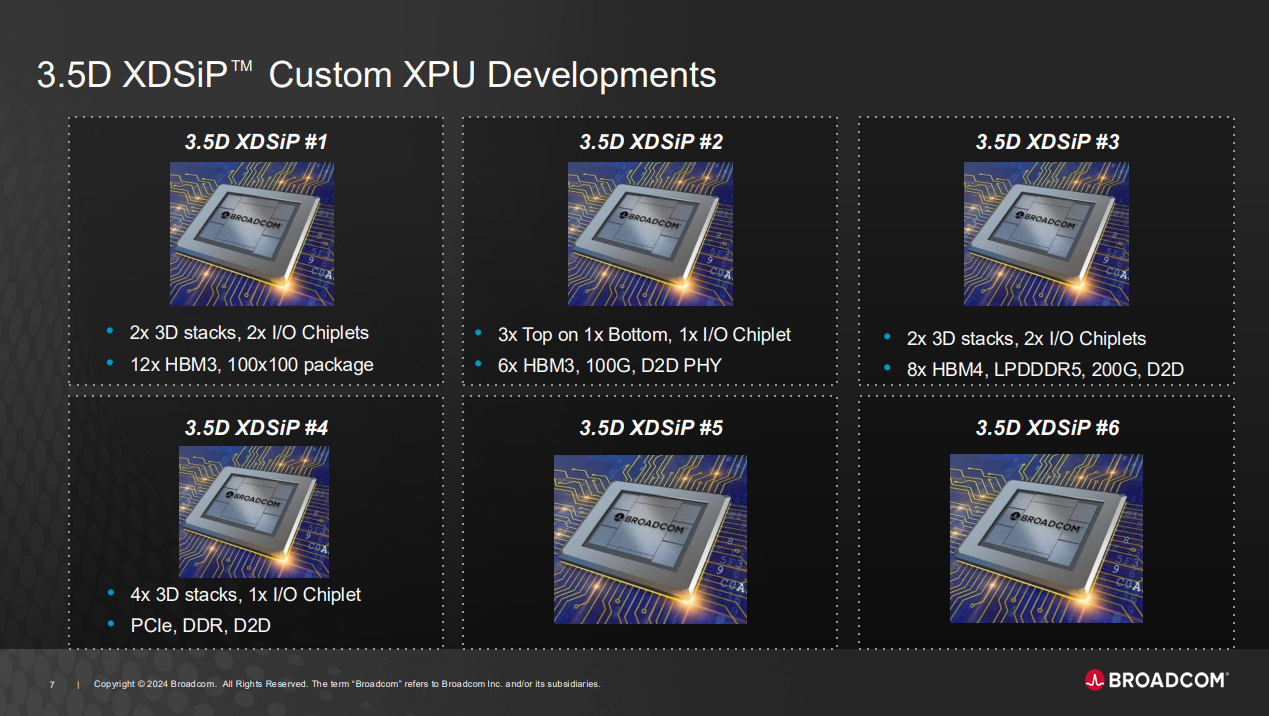

圖源:博通

博通表示,3.5D XDSiP技術目前已經被主要的AI領域客戶使用,已經有6款產品正在開發中。其中富士通下一代2nm制程的Arm處理器FUJITSU-MONAKA已經確認使用博通3.5D XDSiP技術,這款處理器面向數據中心、邊緣計算等應用,據此前富士通的介紹,MONAKA每顆CPU包含一個中央的I/O die和四個3D垂直堆疊die,并集成SRAM,預計2027年出貨。

使用3.5D XDSiP技術的芯片產品,博通預計最早在2026年2月實現出貨。

小結:

先進封裝作為未來AI計算芯片的重要部分,博通這種大面積的芯片封裝方案,能夠極大程度上提高系統集成度,同時通過創新的互連方案,提高片內互連的帶寬和提高能效,有望成為未來高性能處理器的一個重要方向。

-

博通

+關注

關注

36文章

4346瀏覽量

109131

發布評論請先 登錄

H200 解禁!預交付8萬顆,傳阿里砸數億抄底對手

如何用一顆低成本Flash語音芯片,同時實現高性能與設計自由?WTN6 F系列給出答案

美國政府正式批準英偉達H200芯片對華出口

如何用一顆芯片搞定語音、顯示與傳感?解碼唯創高集成語音IC方案

美國將允許英偉達H200對華出口,但要抽成25%

突發!特朗普批準英偉達H200芯片對華出口,抽成25%

一顆芯片賣爆了是什么感覺

今日看點:馬斯克:特斯拉已部署超百萬顆 AI 芯片;長鑫存儲發布全新 DDR5 內存新品

長晶接口電路CJLSF0102系列一顆料同時替代TI與安世

從 2D 到 3.5D 封裝演進中焊材的應用與發展

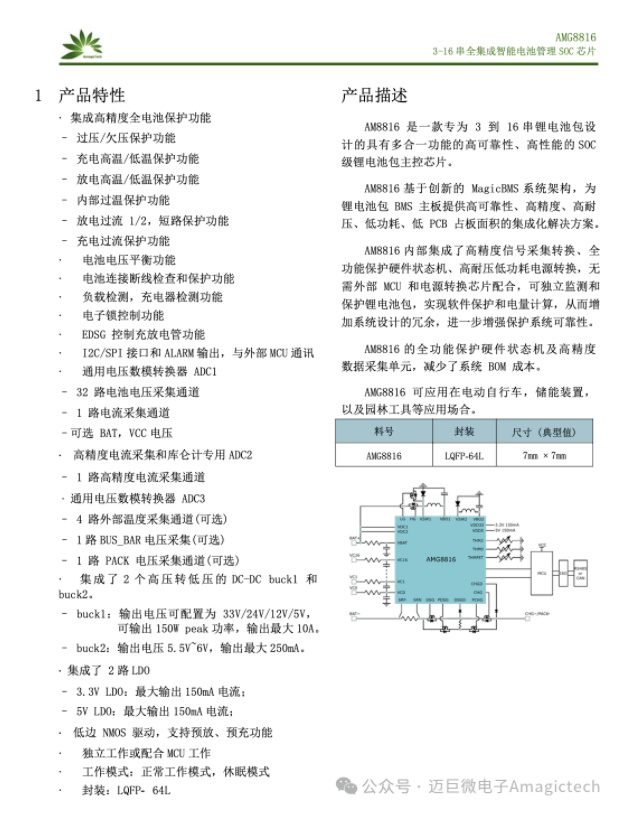

3-16串一顆芯片搞定 全解AMG8816全集成BMS主控的參數真相

請問VL53L4CXV0DH/1,這一顆tof, 是否支持100赫茲的測量頻率?

LED 燈壞一顆全滅?這招讓故障 “無感自愈”,90% 工程師都在抄!

如何用一顆SOP8芯片實現色溫+亮度精準控制?

一顆芯片面積頂4顆H200,博通推出3.5D XDSiP封裝平臺

一顆芯片面積頂4顆H200,博通推出3.5D XDSiP封裝平臺

評論