2024年8月21-23日,思爾芯亮相第四屆RISC-V中國峰會,與全球RISC-V生態伙伴共同探討了AI時代RISC-V架構的未來發展。

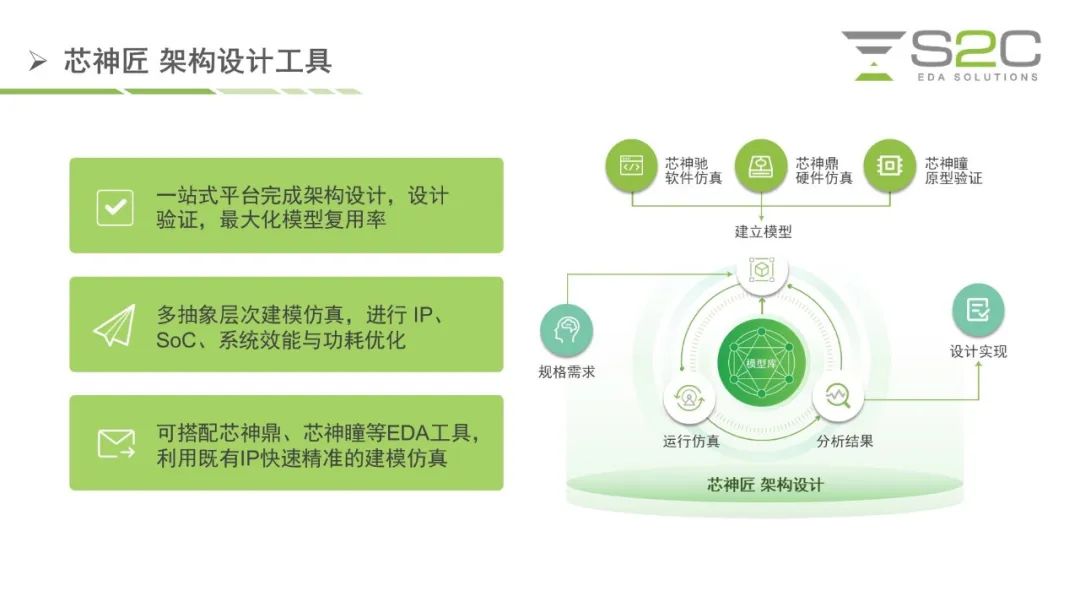

峰會期間,由于近期思爾芯在架構設計軟件的研發上取得了進展,該項目的成員——產品經理梁琪與研發工程師被邀請至演講臺,他們為與會者帶來了題為《基于 RISC-V 的架構建模及混合仿真驗證方法》的技術演講。面對當前計算架構日新月異的變革,梁琪深刻剖析道:“RISC-V憑借其簡潔的指令集架構,在開源處理器中脫穎而出,前景非常廣闊。同時隨著多個領域的深入應用,要發展其潛力和優勢也將面臨很多挑戰。”梁琪詳細介紹了思爾芯的“芯神匠”架構設計工具,該平臺能夠一站式完成架構設計、設計驗證,并通過不同抽象層次的建模仿真優化IP、SoC及系統。同時可搭配芯神鼎、芯神瞳、芯神馳等EDA工具進行混合仿真。

針對混合仿真技術,梁琪進一步闡述了其重要性及應用場景,包括系統組件間的協同仿真、不同抽象層級模型的結果對比驗證等。她強調,混合仿真技術對于提升設計驗證效率與關鍵部件的驗證是一種重要的手段。

隨后,由開發這一EDA工具的工程師深入剖析了混合仿真技術在架構設計中的技術邏輯。他表示,思爾芯的混合仿真框架不僅基于圖形化的架構建模方式,提供了直觀易用的操作界面,還通過緊密結合架構建模與混合仿真驗證,實現了對設計錯誤的快速發現與精確定位,極大地提升了設計效率與質量。

展會現場,思爾芯更是以一系列硬核產品驚艷亮相,通過生動的現場Demo體驗,向與會者全方位展示了其在RISC-V領域的技術實力與創新成果。其中,RISC-V香山圖形化顯示項目作為RISC-V架構芯片設計的先鋒之作,不僅彰顯了思爾芯在原型驗證技術方面的獨特優勢,更為RISC-V架構的廣泛應用樹立了新的標桿。此外,演講中提及的架構設計與軟件仿真的實際運行Demo,同樣吸引了眾多與會者的目光,成為展會上一大亮點。

此次RISC-V中國峰會的成功舉辦,不僅為RISC-V生態的繁榮發展注入了新的活力,也為思爾芯等優秀企業提供了展示自我、交流合作的寶貴平臺。展望未來,思爾芯將繼續秉承創新精神,攜手全球生態伙伴,共同推動RISC-V架構在AI時代的蓬勃發展,開啟計算架構的新篇章。

-

仿真驗證

+關注

關注

0文章

27瀏覽量

8354 -

RISC-V

+關注

關注

48文章

2886瀏覽量

53001 -

思爾芯

+關注

關注

0文章

150瀏覽量

1721

發布評論請先 登錄

思爾芯、MachineWare與Andes晶心科技聯合推出RISC-V協同仿真方案,加速芯片開發

硬核加速,軟硬協同!混合仿真賦能RISC-V芯片敏捷開發

2025 RISC-V中國峰會 | 匠芯創SoC芯片引領工業應用新潮流

普華基礎軟件亮相2025 RISC-V中國峰會

Andes晶心科技亮相2025 RISC-V中國峰會

奕斯偉計算亮相2025 RISC-V中國峰會

燦芯半導體亮相2025 RISC-V中國峰會

睿思芯科亮相第五屆RISC-V中國峰會

思爾芯攜手Andes晶心科技,加速先進RISC-V 芯片開發

思爾芯亮相RISC-V中國峰會,展示架構建模與混合仿真驗證方法

思爾芯亮相RISC-V中國峰會,展示架構建模與混合仿真驗證方法

評論