在今年的IEEE IMW 2024活動中,三星DRAM業務的資深副總裁Lee指出,已有多家科技巨頭如三星成功制造出16層3D DRAM,其中美光更是發展至8層水平。

然而,他也強調,現階段三星正致力于探索3D DRAM及垂直堆疊單元陣列晶體管(VS-CAT)的可行性,暫無大量量產的計劃。值得注意的是,Lee曾在美光擔任過未來存儲芯片的研究工作,后于去年加入三星。

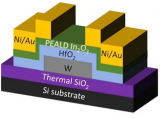

VS-CAT與傳統DRAM有所區別,其采用雙硅晶圓設計,外圍設備和邏輯/存儲單元獨立連接。若將外圍設備直接連接至單元層,會導致表面積過大。

因此,外圍設備通常在另一片晶圓上制造,再與存儲單元通過鍵合方式連接。預計3D DRAM將采用晶圓對晶圓(wafer-to-wafer)等混合鍵合技術進行生產,此項技術已廣泛運用于NAND和CMOS圖像傳感器的制造過程。

此外,三星還計劃將背面供電網絡(BSPDN)技術引入3D DRAM領域。

同時,三星亦在研究垂直溝道晶體管(VCT)。VCT又稱4F2,較之先前的6F2技術,可大幅降低晶粒表面積,最高可達30%。據悉,原型產品有望于明年問世。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

DRAM

+關注

關注

41文章

2394瀏覽量

189143 -

硅晶圓

+關注

關注

4文章

276瀏覽量

22127 -

三星

+關注

關注

1文章

1766瀏覽量

34191

發布評論請先 登錄

相關推薦

熱點推薦

鎧俠公布3D DRAM 技術

電子發燒友網綜合報道,日前,Kioxia鎧俠公司宣布開發出高性能晶體管技術,該技術將使得高密度、低功耗 3D DRAM 的實現成為可能。這項技術在 12月 10 日于美國舊金山舉行的

Kioxia研發核心技術,助力高密度低功耗3D DRAM的實際應用

全球存儲解決方案領域的領軍企業Kioxia Corporation今日宣布,已研發出具備高堆疊性的氧化物半導體溝道晶體管技術,該技術將推動高密度、低功耗3D

三星公布首批2納米芯片性能數據

三星公布了即將推出的首代2nm芯片性能數據;據悉,2nm工藝采用的是全柵極環繞(GAA)晶體管技術,相比第二代3nm工藝,性能提升5%,功耗效率提高8%,

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

。

叉行片:連接并集成兩個晶體管NFET和PFET,它們之間同時被放置一層不到10nm的絕緣膜,放置缺陷的發生。

CFET:屬于下一代晶體管結構,采用3D

發表于 09-15 14:50

半導體存儲芯片核心解析

(FTL,磨損均衡,糾錯等),存在讀寫干擾問題。

結構演進:

平面 NAND:傳統二維結構,工藝微縮遇到瓶頸。

3D NAND:將存儲單元垂直堆疊(幾十

發表于 06-24 09:09

下一代高速芯片晶體管解制造問題解決了!

,10埃)開始一直使用到A7代。

從這些外壁叉片晶體管的量產中獲得的知識可能有助于下一代互補場效應晶體管(CFET)的生產。

目前,領先的芯片制造商——英特爾、臺積電和三星——正在利用

發表于 06-20 10:40

無結場效應晶體管詳解

當代所有的集成電路芯片都是由PN結或肖特基勢壘結所構成:雙極結型晶體管(BJT)包含兩個背靠背的PN 結,MOSFET也是如此。結型場效應晶體管(JFET) 垂直于溝道方向有一個 PN

三星在4nm邏輯芯片上實現40%以上的測試良率

三星電子在 HBM3 時期遭遇了重大挫折,將 70% 的 HBM 內存市場份額拱手送給主要競爭對手 SK 海力士,更是近年來首度讓出了第一大 DRAM 原廠的寶座。這迫使

發表于 04-18 10:52

三星電子研發16層3D DRAM芯片及垂直堆疊單元晶體管

三星電子研發16層3D DRAM芯片及垂直堆疊單元晶體管

評論