簡(jiǎn)介

本文可讓開(kāi)發(fā)者們看懂 AMD Vivado Design Tool 2023.2 中的“AMD Versal Adaptive SoCCPM PCIE PIO EP 設(shè)計(jì)”CED 示例。?

“AMD VersalAdaptive SoCCPM PCIE PIO EP 設(shè)計(jì)”支持您使用可以正常工作的既定設(shè)計(jì)來(lái)初始化您的系統(tǒng)開(kāi)發(fā)板,以驗(yàn)證此開(kāi)發(fā)板的連接與功能。

PCI Express 系統(tǒng)主機(jī) CPU 通常使用編程輸入/輸出 (PIO) 傳輸事務(wù)來(lái)訪問(wèn) PCI Express 邏輯中的存儲(chǔ)映射輸入/輸出 (MMIO) 位置和配置映射輸入/輸出 (CMIO) 位置。

Endpoints for PCI Express 可接受“Memory and I/O Write”傳輸事務(wù),并以“Completion with Data”傳輸事務(wù)來(lái)響應(yīng)“Memory and I/O Read”傳輸事務(wù)。

功能特性

AMD VersalAdaptive SoCPIO 設(shè)計(jì)的 CED 示例按“DWORD Aligned Mode”來(lái)配置。以下提供了您可利用設(shè)計(jì)示例來(lái)實(shí)踐的部分功能特性:

此設(shè)計(jì)在 AMD Versal Adaptive SoC器件塊 RAM 內(nèi)實(shí)現(xiàn)一個(gè)目標(biāo)空間。

此目標(biāo)空間可通過(guò)存儲(chǔ)器寫 32 TLP 和存儲(chǔ)器讀 32 TLP 來(lái)訪問(wèn)。

對(duì)于來(lái)自核的有效的存儲(chǔ)器讀 32 TLP 請(qǐng)求,PIO 會(huì)生成完成包(大小即有效載荷的大小)以作為響應(yīng)。

PIO 設(shè)計(jì)會(huì)通過(guò)將有效載荷更新到 AMDVersal Adaptive SoC器件中的塊 RAM 空間的目標(biāo)地址內(nèi)來(lái)處理 1DW/2DW 存儲(chǔ)器寫或 I/O 寫 TLP。

雖然此鏈接指向 PL PCIE IP 核設(shè)計(jì)示例,但 AMD Versal Adaptive SoCPIO 設(shè)計(jì)的 CED 示例同樣基于此設(shè)計(jì)示例,因此該鏈接中提供的詳細(xì)信息同樣適用于 CPM PIO 設(shè)計(jì)。

設(shè)計(jì)生成

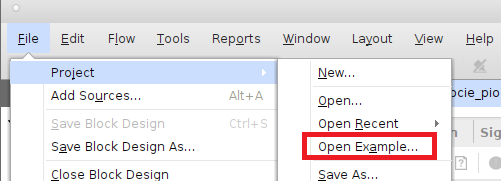

在 AMD Vivado Design Tool 中,轉(zhuǎn)至“File -> Project -> Open Example”。

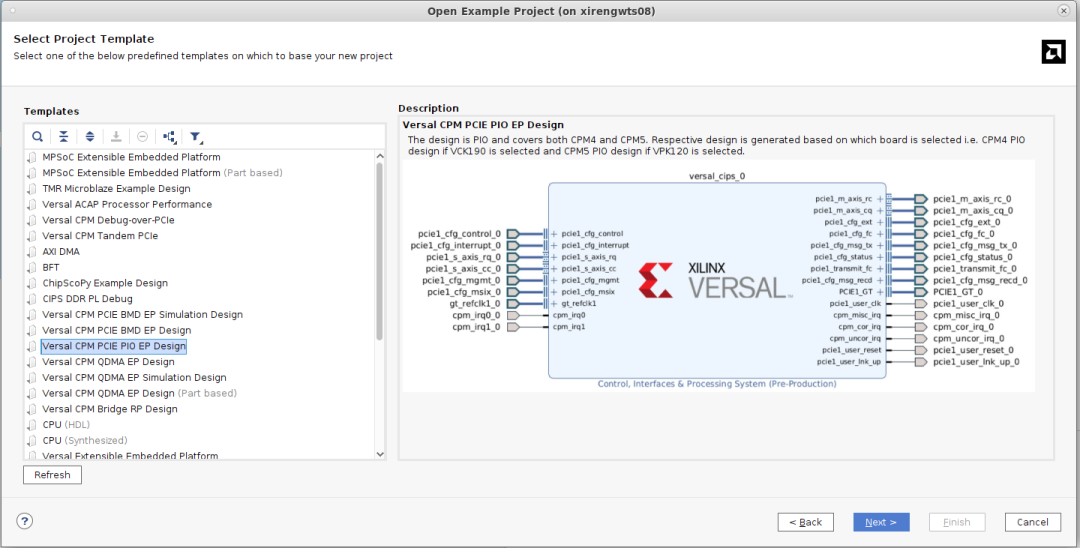

這樣即可看到如下可用示例列表。選中“AMD Versal Adaptive SoCCPM PCIE PIO EP Design”,然后單擊“Next”。

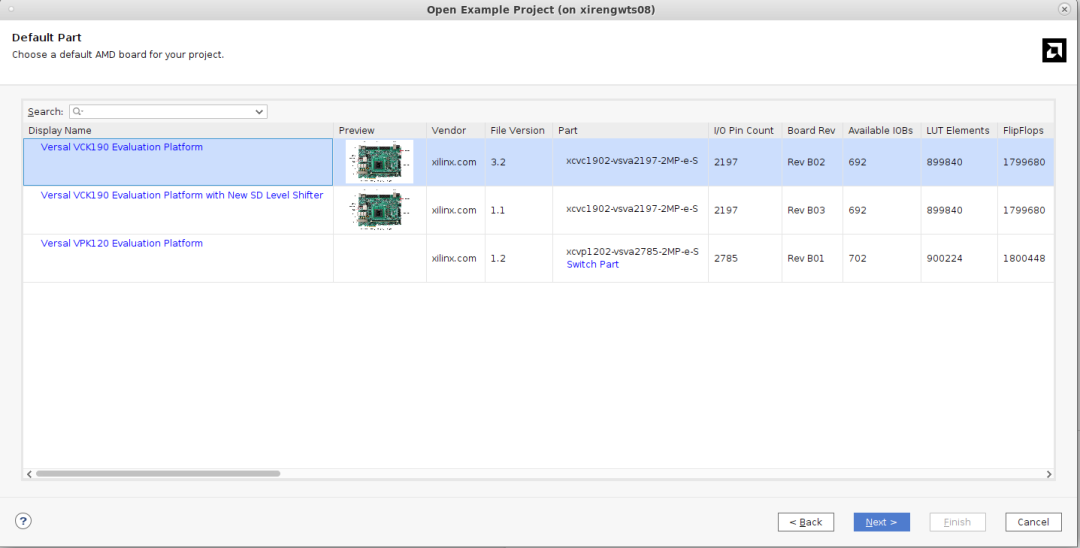

所提供的設(shè)計(jì)示例支持 VCK190 評(píng)估板和 VCK120 評(píng)估板。對(duì)于其他開(kāi)發(fā)板,為其中任一開(kāi)發(fā)板生成的設(shè)計(jì)示例均可作為參考用于為所需開(kāi)發(fā)板進(jìn)行設(shè)計(jì)轉(zhuǎn)換。

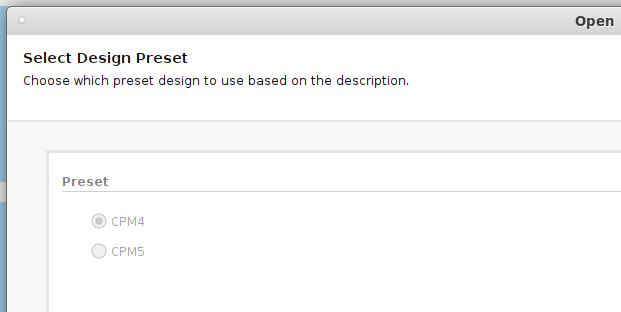

根據(jù)所選開(kāi)發(fā)板,將自動(dòng)選擇“Preset”,針對(duì) VCK190 將選中 CPM4,針對(duì) VPK120 則選中 CPM5。

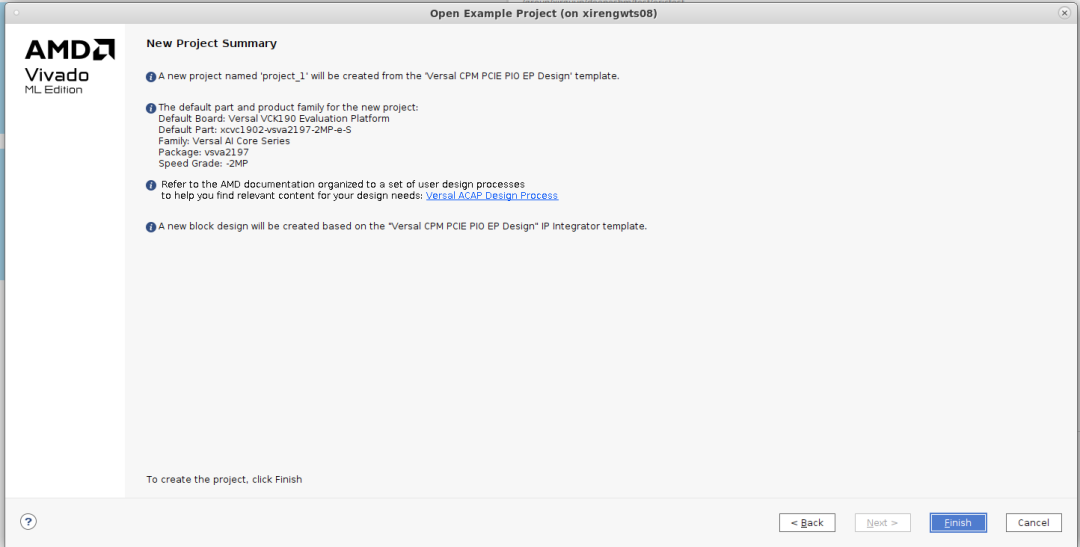

復(fù)查工程匯總信息,確認(rèn)所選部件和產(chǎn)品系列正確。

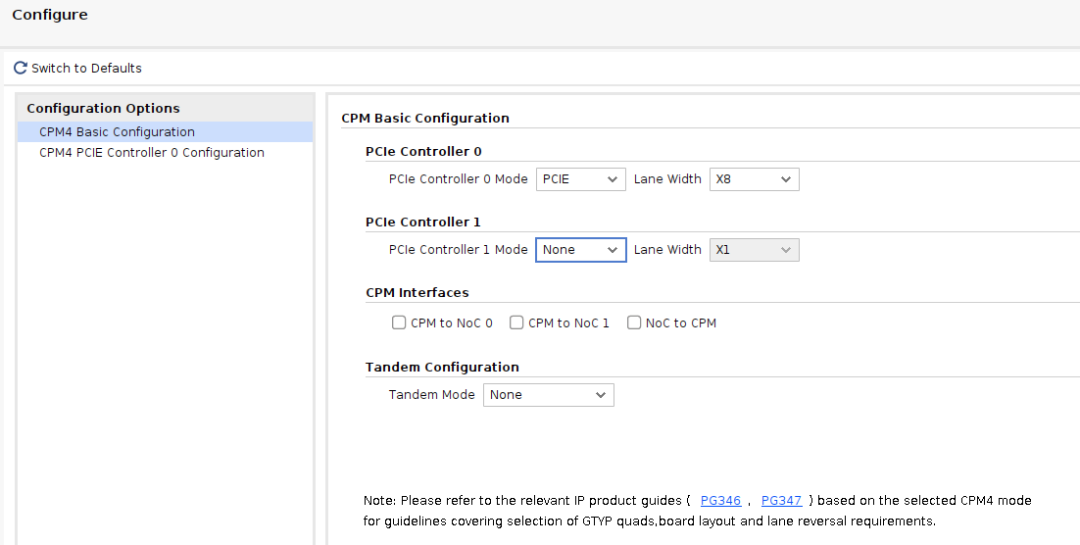

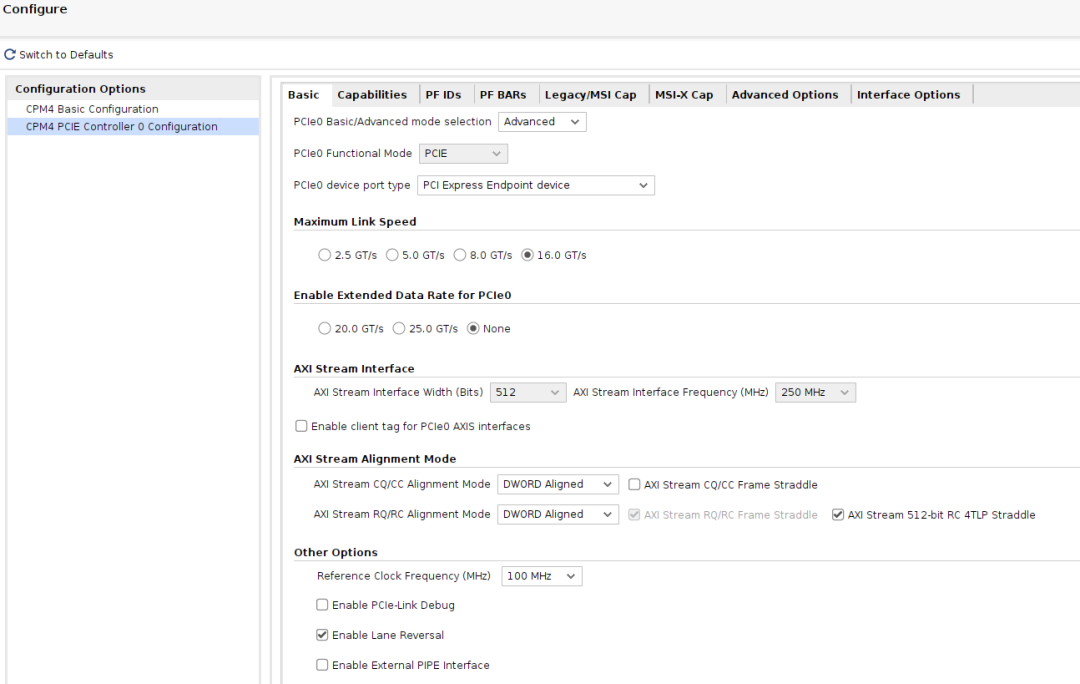

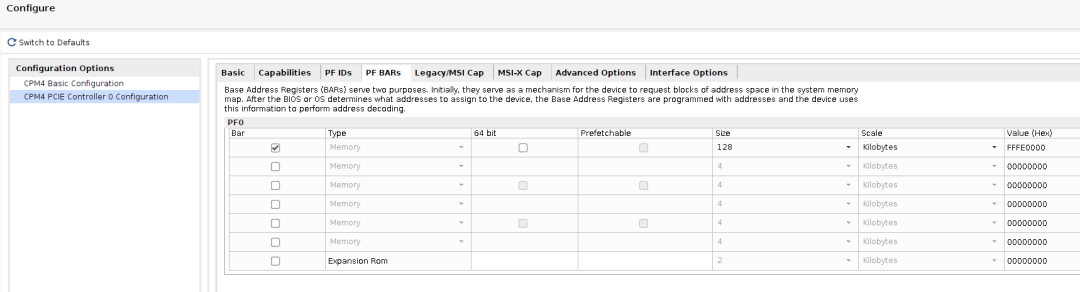

CPM 配置

生成的默認(rèn) AMD Versal Adaptive SoCCPM PCIE PIO EP 設(shè)計(jì)配置如下:

Gen4x8。

DWORD 對(duì)齊。

啟用 AXI Stream 512 位 RC 4TLP 跨接。

禁用 AXI Stream CQ/CC 跨幀。

啟用通道翻轉(zhuǎn)。

使用 PCIE 控制器 0。

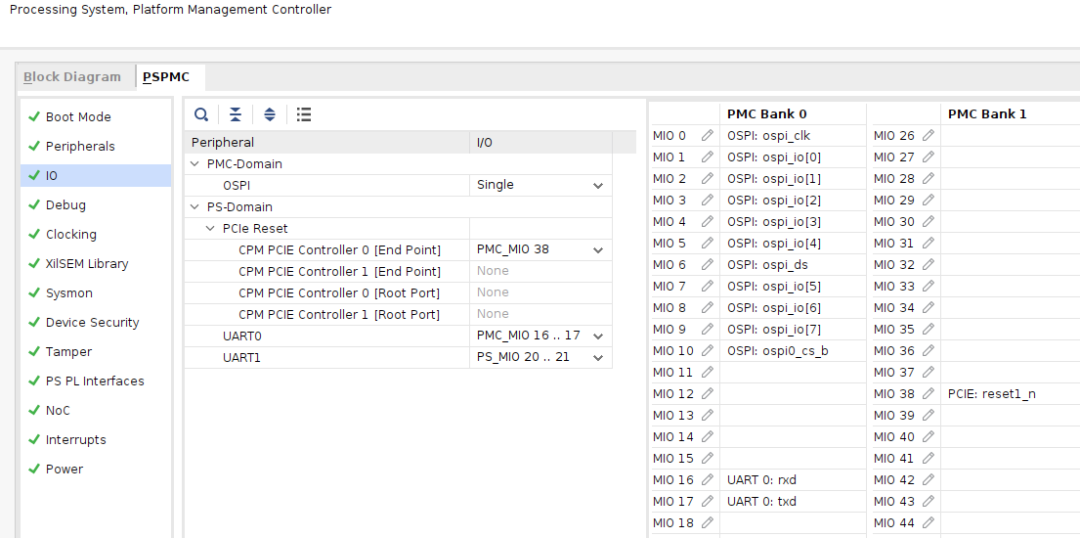

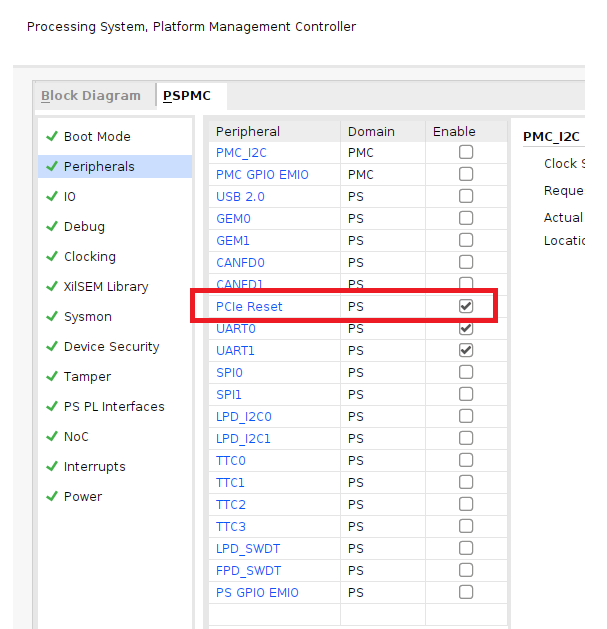

針對(duì)所選開(kāi)發(fā)板和控制器將復(fù)位配置到 PMC_MIO 38。

PS PMC 配置

設(shè)計(jì)示例模塊框圖

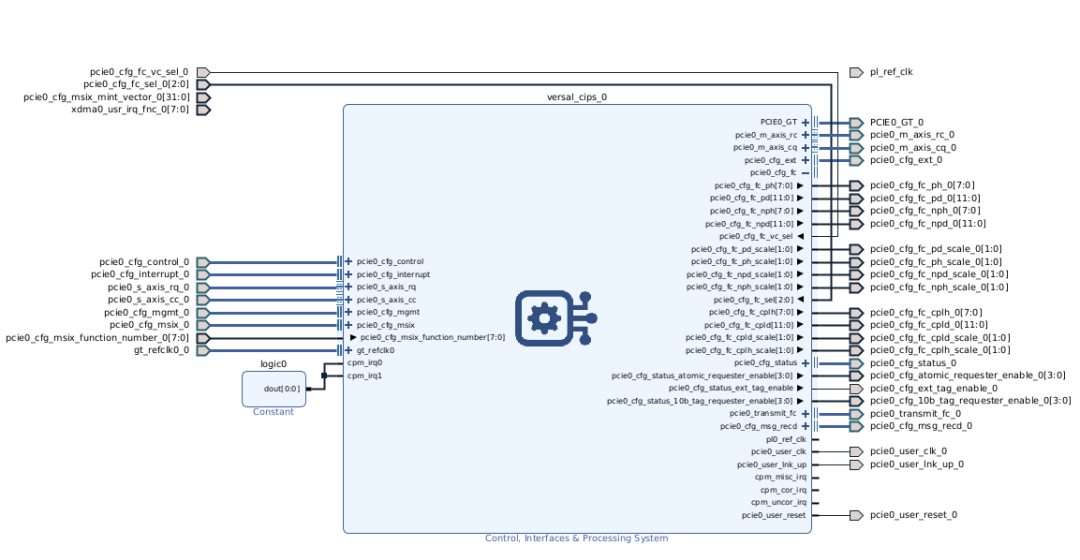

以下是生成的 CIPS 的最終模塊框圖。I/O 和復(fù)位約束均由設(shè)計(jì)示例基于所選開(kāi)發(fā)板來(lái)進(jìn)行分配。

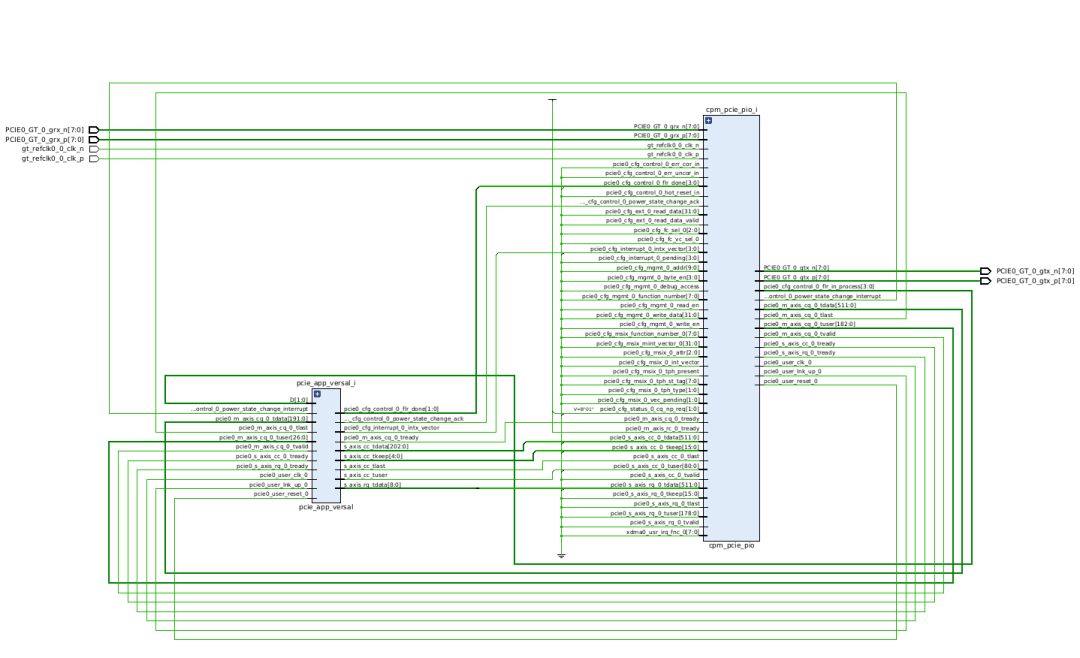

以下板級(jí)原理圖設(shè)計(jì)顯示了由 CPM 與 PIO 應(yīng)用在后端組成的整體設(shè)計(jì)示例。

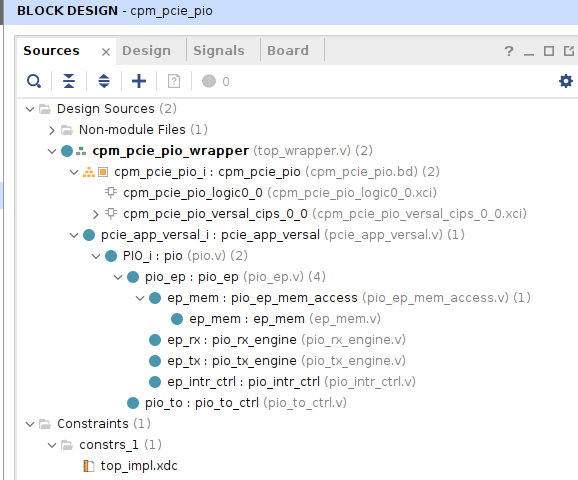

設(shè)計(jì)示例源文件

pcie_app_versal_i是設(shè)計(jì)示例模塊,負(fù)責(zé)處理傳入的“Memory Read”和“Memory Write”,并以“Completion”包來(lái)響應(yīng)。

下表顯示了 PIO 示例設(shè)計(jì)的文件結(jié)構(gòu)。

| 文件 | 描述 |

| PIO.v | 頂層設(shè)計(jì)封裝 |

| PIO_INTR_CTRL.v | PIO 中斷控制器 |

| PIO_EP.v | PIO 應(yīng)用模塊 |

| PIO_TO_CTRL.v | PIO 關(guān)閉控制器模塊 |

| PIO_RX_ENGINE.v | 32 位接收引擎 |

| PIO_TX_ENGINE.v | 32 位發(fā)射引擎 |

| PIO_EP_MEM_ACCESS.v | 端點(diǎn)存儲(chǔ)器訪問(wèn)模塊 |

| PIO_EP_MEM.v | 端點(diǎn)存儲(chǔ)器 |

| PIO_EP_XPM_SDRAM_WRAP.v | 采用 Dword 對(duì)齊模式的端點(diǎn)存儲(chǔ)器 |

審核編輯:劉清

-

控制器

+關(guān)注

關(guān)注

114文章

17787瀏覽量

193074 -

存儲(chǔ)器

+關(guān)注

關(guān)注

39文章

7738瀏覽量

171650 -

SoC設(shè)計(jì)

+關(guān)注

關(guān)注

1文章

151瀏覽量

19541

原文標(biāo)題:開(kāi)發(fā)者分享|AMD Versal? Adaptive SoC CPM PCIE PIO EP 設(shè)計(jì) CED 示例

文章出處:【微信號(hào):gh_2d1c7e2d540e,微信公眾號(hào):XILINX開(kāi)發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

基于AMD Versal器件實(shí)現(xiàn)PCIe5 DMA功能

在AMD Versal自適應(yīng)SoC上使用QEMU+協(xié)同仿真示例

AMD 7nm Versal系列器件NoC的使用及注意事項(xiàng)

使用Aurora 6466b協(xié)議實(shí)現(xiàn)AMD UltraScale+ FPGA與AMD Versal自適應(yīng)SoC的對(duì)接

AMD Versal自適應(yīng)SoC內(nèi)置自校準(zhǔn)的工作原理

Spartan6 PCIe PIO示例無(wú)法使用lspci查看卡

Versal CPM AXI Bridge模式的地址轉(zhuǎn)換

AMD Versal自適應(yīng)SoC CPM5 QDMA的Tandem PCIe啟動(dòng)流程介紹

AMD推出第二代Versal Premium系列

AMD Vivado Design Suite 2024.2全新推出

如何通過(guò)PMC_GPIO喚醒AMD Versal? Adaptive SoC Linux系統(tǒng)

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(上)

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(下)

AMD Versal? Adaptive SoC CPM PCIE PIO EP設(shè)計(jì)CED示例

AMD Versal? Adaptive SoC CPM PCIE PIO EP設(shè)計(jì)CED示例

評(píng)論