在功耗敏感的系統(tǒng)里,我們通常會在系統(tǒng)空閑的時候?qū)⑾到y(tǒng)休眠,然后可以通過一些外設(shè)的輸入來喚醒系統(tǒng),比如 Uart、USB 和 GPIO。AMD VersalAdaptive SoC 系統(tǒng)的休眠喚醒指導(dǎo)頁面和 MPSoC 系統(tǒng)在同一個 Wiki 網(wǎng)頁。本文將通過 PMC_GPIO 作為例子來描述如何喚醒 Versal 系統(tǒng)。

Wiki 網(wǎng)頁:

https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18842232/Zynq+UltraScale+MPSoC+Power+Management+-+Linux+Kernel

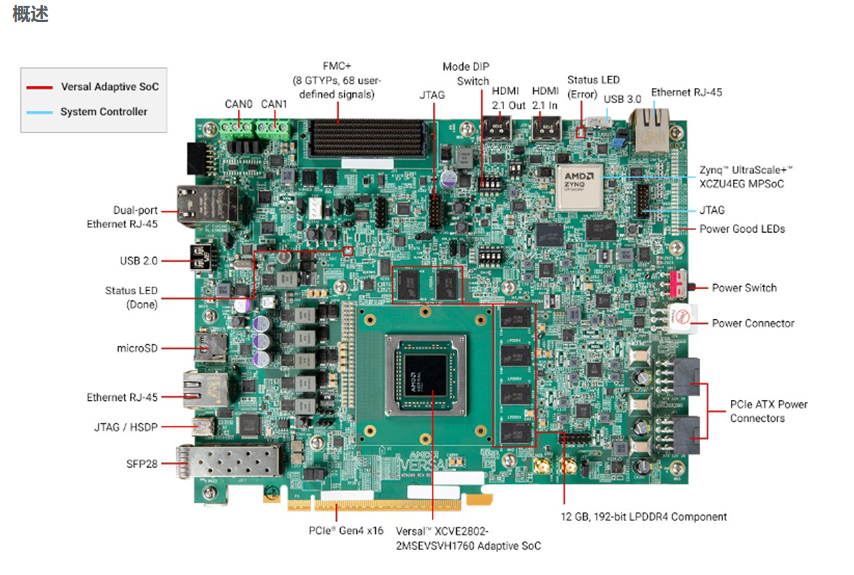

我們這里采用 VPK120 板卡作為平臺,這個板卡上面沒有通過 PMC MIO 連接 GPIO 器件,所以我們需要使用 PMC EMIO 來實現(xiàn) GPIO。我們可以在 VPK120 Petalinux BSP 里的 AMD VivadoDesign Suite 工程基礎(chǔ)上增加 PMC_GPIO_EMIO。

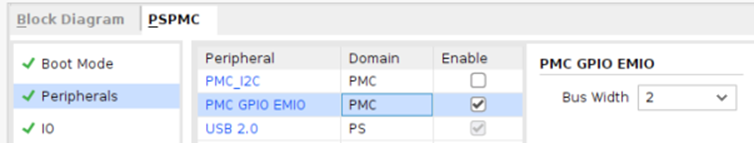

1. 首先打開 Vivado 工程進(jìn)入 CIPS core 配置界面并使能 PMC_GPIO_EMIO,板卡上有兩個 Button 器件連接到了兩個 PL 管腳,所以位寬選擇為 2。這兩個 Button 在板卡上分為名為 SW4 和 SW5。

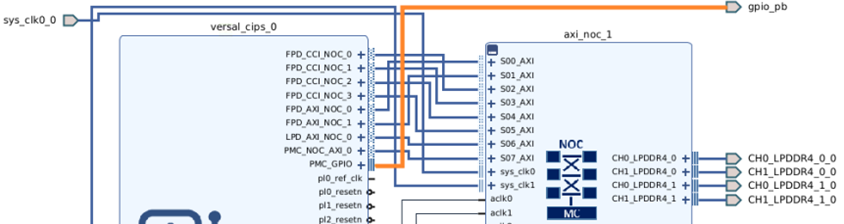

2. 這時 CIPS core 的界面上會多出 PMC_GPIO 端口,右鍵點擊這個端口,菜單中選擇 Make External Pins 可以把這個接口的兩個 GPIO 信號連接到 PL 管腳,我們需要在 XDC 約束文件里增加這兩個管腳的約束。

3. 最后完成 Implementation 并導(dǎo)出 XSA。附件里有預(yù)先做好的 Block design tcl 腳本、頂層 Wrapper 和約束文件。可以用它們直接創(chuàng)建 Vivado 工程。

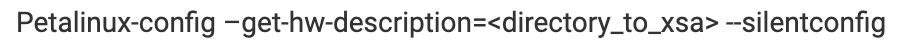

4. 導(dǎo)出 XSA 后,可以用下面命令將 XSA 導(dǎo)入 VPK120 petalinux BSP 里的 Petalinux 工程。

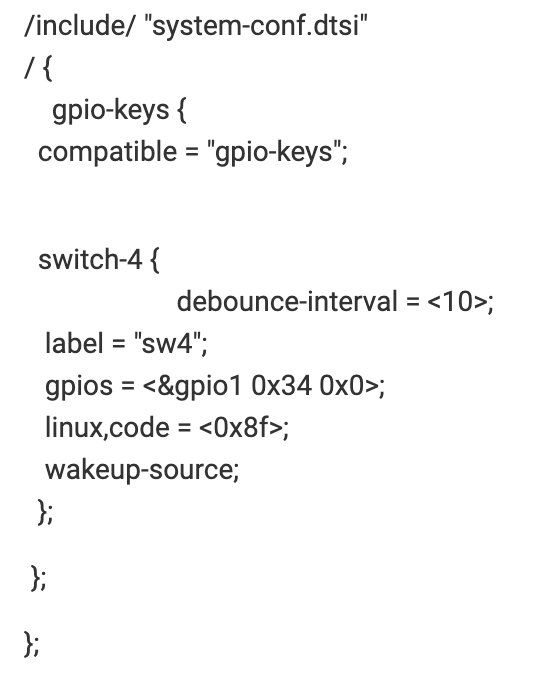

5. 按照上面提到的 Wiki 頁面里對 GPIO 的要求配置 Kernel,并在“project-spec/meta-user/recipes-bsp/device-tree/files/system-user.dtsi“里增加 gpio-keys節(jié)點。

6. 在 2023.2 版本里,ATF 和 PLM 需要兩個 Patch 來支持 GPIO 喚醒。使用下面方法將兩個 Patch 應(yīng)用到 Petalinux 工程,最后執(zhí)行 petalinux-build 命令。

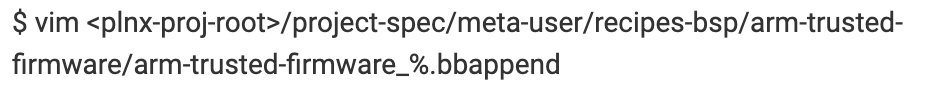

將ATF patch "0001-fix-xilinx-map-PMC_GPIO-device-node-to-interrupt-for 1.patch"拷貝到“project-spec/meta-user/recipes-bsp/arm-trusted-firmware/files/”,如果沒有這個路徑就手動創(chuàng)建。

執(zhí)行下面命令創(chuàng)建“arm-trusted-firmware_%.bbappend”文件。

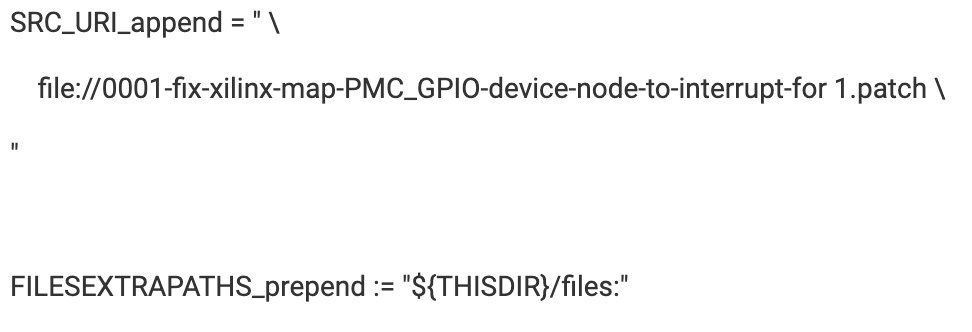

將下面內(nèi)容拷貝到“arm-trusted-firmware_%.bbappend”并保存。

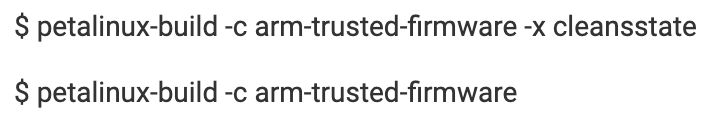

執(zhí)行下面命令。

參考 Wiki 頁面,將 PLM patch 文件“0001-xilpm-versal-server-Add-entry-for-PMC_GPIO-in-Wakeup.patch” 應(yīng)用到 Petalinux 工程。

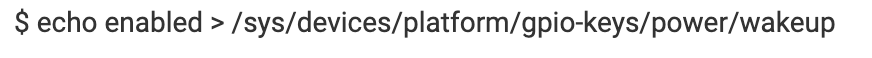

7. 使用下面命令使系統(tǒng)休眠。使用下面命令使能 gpio 為 Wakeup source。

8. 使用下面命令使系統(tǒng)休眠。

9. 按動板卡上的 SW4 button,Linux 系統(tǒng)就會喚醒。

-

soc

+關(guān)注

關(guān)注

38文章

4525瀏覽量

227805 -

Linux

+關(guān)注

關(guān)注

88文章

11641瀏覽量

218190 -

GPIO

+關(guān)注

關(guān)注

16文章

1314瀏覽量

55789 -

Versal

+關(guān)注

關(guān)注

1文章

172瀏覽量

8390

原文標(biāo)題:開發(fā)者分享|如何通過 PMC_GPIO 喚醒 AMD Versal? Adaptive SoC Linux 系統(tǒng)

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

探索AMD XILINX Versal Prime Series VMK180評估套件,開啟硬件創(chuàng)新之旅

AMD Vivado Design Suite 2025.2版本現(xiàn)已發(fā)布

AMD Versal自適應(yīng)SoC內(nèi)置自校準(zhǔn)的工作原理

AMD Vivado IP integrator的基本功能特性

在AMD Versal自適應(yīng)SoC上使用QEMU+協(xié)同仿真示例

基于AMD Versal器件實現(xiàn)PCIe5 DMA功能

AMD第二代Versal AI Edge和Versal Prime系列加速量產(chǎn) 為嵌入式系統(tǒng)實現(xiàn)單芯片智能

利用AMD VERSAL自適應(yīng)SoC的設(shè)計基線策略

AMD Versal Adaptive SoC Clock Wizard AXI DRP示例

適用于Versal的AMD Vivado 加快FPGA開發(fā)完成Versal自適應(yīng)SoC設(shè)計

第二代AMD Versal Premium系列SoC滿足各種CXL應(yīng)用需求

面向AI與機(jī)器學(xué)習(xí)應(yīng)用的開發(fā)平臺 AMD/Xilinx Versal? AI Edge VEK280

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(下)

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(上)

AMD Versal自適應(yīng)SoC DDRMC如何使用Micron仿真模型進(jìn)行仿真

如何通過PMC_GPIO喚醒AMD Versal? Adaptive SoC Linux系統(tǒng)

如何通過PMC_GPIO喚醒AMD Versal? Adaptive SoC Linux系統(tǒng)

評論