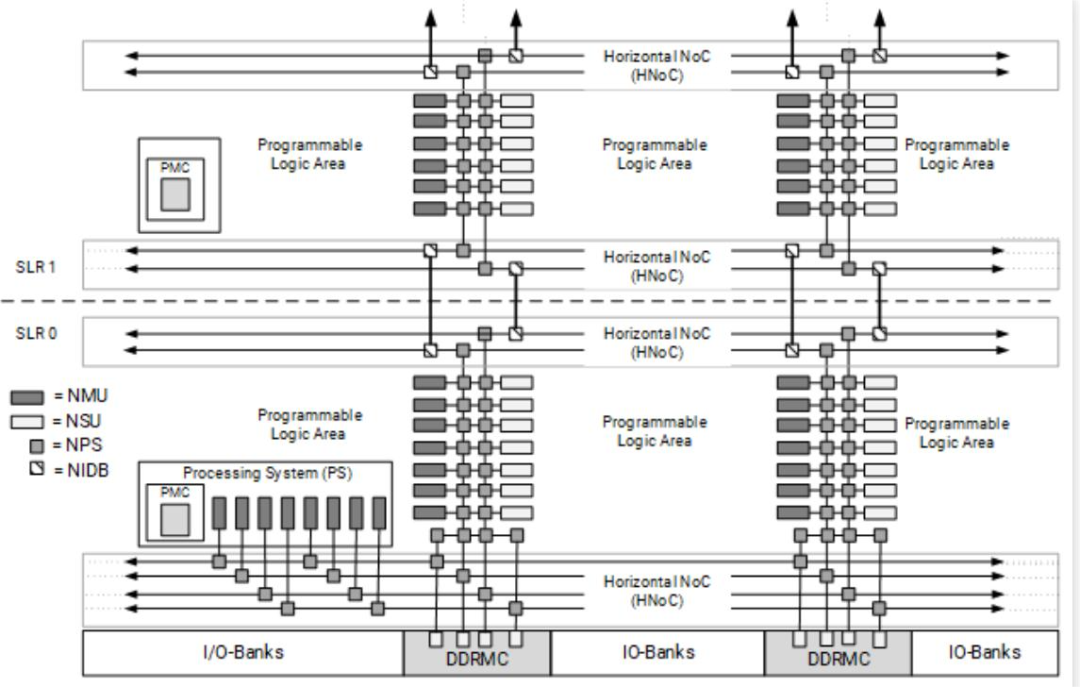

AMD 7nm Versal系列器件引入了可編程片上網絡(NoC, Network on Chip),這是一個硬化的、高帶寬、低延遲互連結構,旨在實現可編程邏輯(PL)、處理系統(PS)、AI引擎(AIE)、DDR控制器(DDRMC)、CPM(PCIe/CXL)等模塊之間的高效數據交換。

NoC的出現,替代了傳統PL內部布線實現復雜總線互連的方式,通過專用硬化通道提升吞吐量、降低延遲、減少邏輯資源占用,并且能實現跨Die(SSIT封裝)的高速通信。

NoC架構與特性

NoC包含以下主要組件:

NMU(NoC Master Unit):將AXI請求轉換為NoC數據包(NPP),支持時鐘域轉換與速率匹配;

NSU(NoC Slave Unit):接收并解析NoC數據包(NPP),轉換為AXI協議;

NPS(NoC Packet Switch):全雙工交換機,連接多個NoC節點;

NIDB(NoC Inter-Die Bridge):跨Die的垂直NoC橋接模塊。

核心特性

水平(HNoC)與垂直(VNoC)通道:減少PL內布線壓力,提高拓展能力;

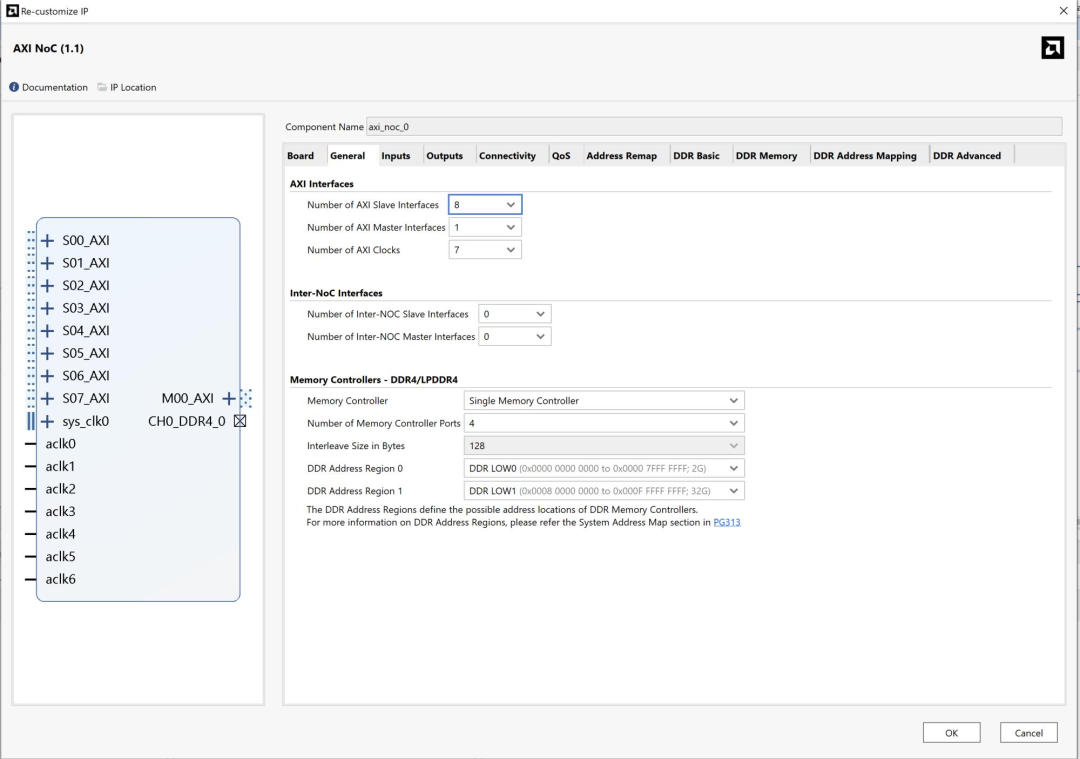

AXI接口靈活配置:支持32位~512位AXI Mem位寬,以及128位~512位AXI4-Stream;

自動交錯訪問:跨多個DDR控制器分配請求,提升帶寬利用率;

QoS(服務質量):提供基于延遲/帶寬的優先級控制;

跨Die通信:多Die設計中提供高效數據通道;

硬化路徑固定延遲:相比可編程互連,延遲更可預測,利于實時應用。

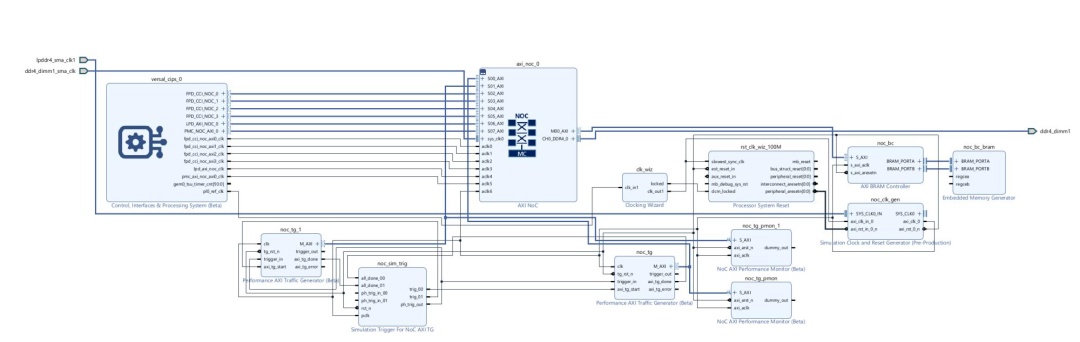

此文結合Vivado工程,快速熟悉NoC的使用

Vivado中的NoC使用步驟:

新建工程 & BD→添加Versal NoC IP

配置AXI\_Slave(NMU)與AXI\_Master(NSU)

連接DDR控制器、CPM、AI Engine等模塊

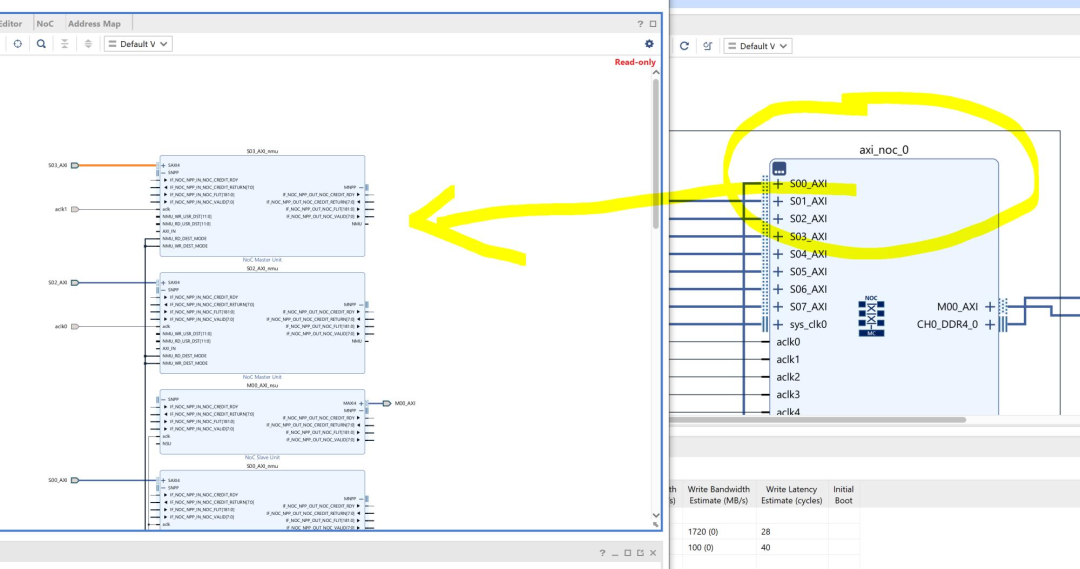

在NoC Compiler中查看拓撲,配置QoS、帶寬、路由路徑

必要時在XDC中固定NMU/NSU位置以減少路徑延遲

分析帶寬與延遲,迭代優化

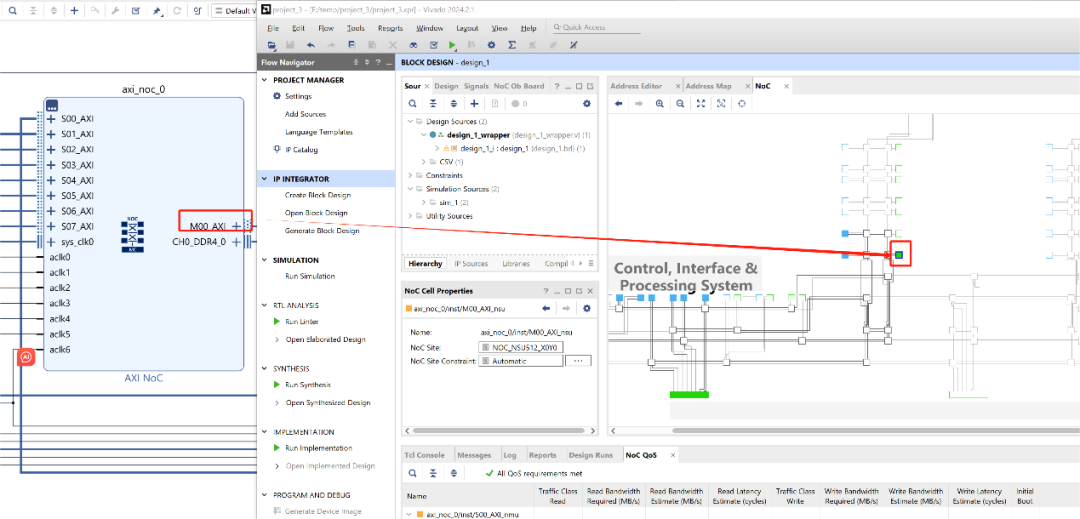

可以看到界面中有AXI_Slave與AXI_Master兩種接口,分別對應NMU與NSU。

NoC內部的組件

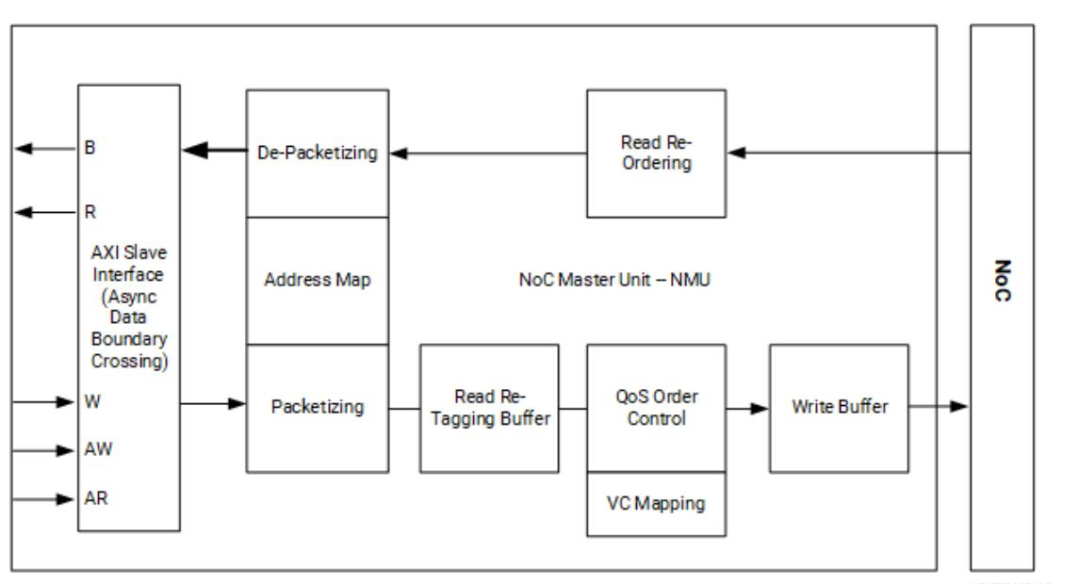

1、NoC Master Unit (NMU)

NMU的作用是將AXI協議轉換為NoC數據包協議(NPP),同時,NMU還支持AXI端口和NoC之間的異步時鐘域轉換與速率匹配。

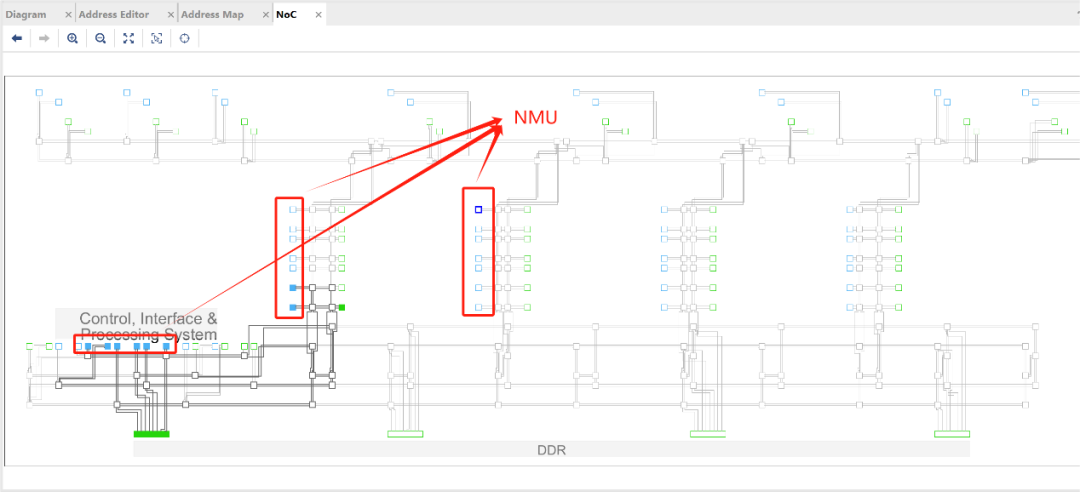

下圖為Vivado工程中NMU的示例:

NMU內部結構:

當AXI請求進入NMU時鐘域時,將執行數據分組,讀寫事務被分解為更小的傳輸(此過程稱為chopping)。

NPP寫入的最大大小為256字節。超過256字節的AXI寫入可以跨越多個NPP寫入。De-Packetizing&Packetizing會將粒度大于或等于256字節的事務切分為256字節的傳輸。例如,一個從0x0開始的1K傳輸事務將分為4 packet進行傳輸:0-255、256-511、512-767、768-1023。

Re-tagging模塊在讀取時重新標記以允許無序傳輸并防止互連阻塞。

在對外的AXI接口上支持配置32位~512位,在AXI4-Stream上支持從128位~512位的可配置數據寬度接口。AXI數據寬度通過參數傳播從連接的IP,無需手動指定位寬。

2、NoC Slave Unit (NSU)

NSU的主要功能是接收和響應來自NoC的數據包,這些數據包尋址到NSU數據包接口,旨在發送到對應的AXI端口。

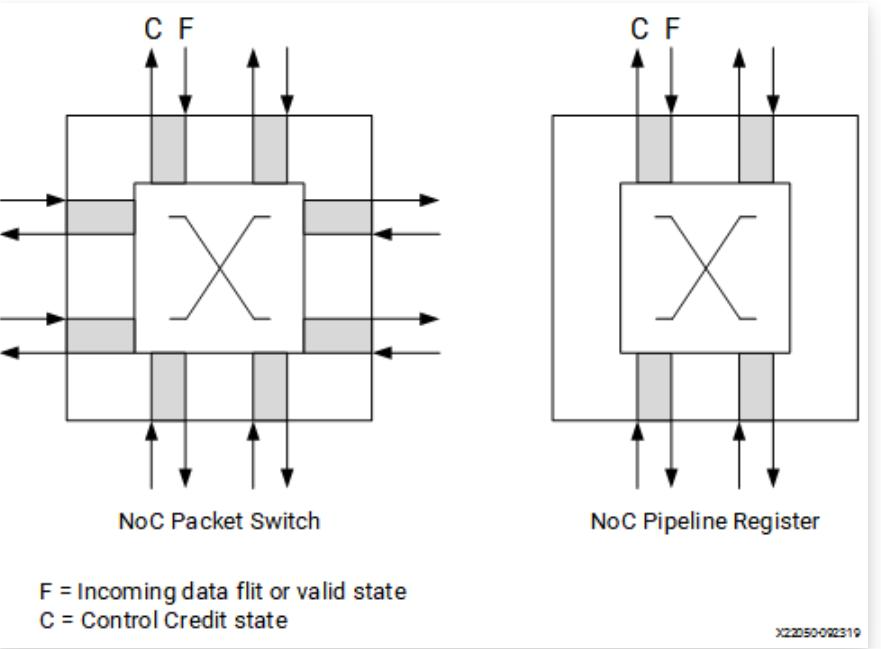

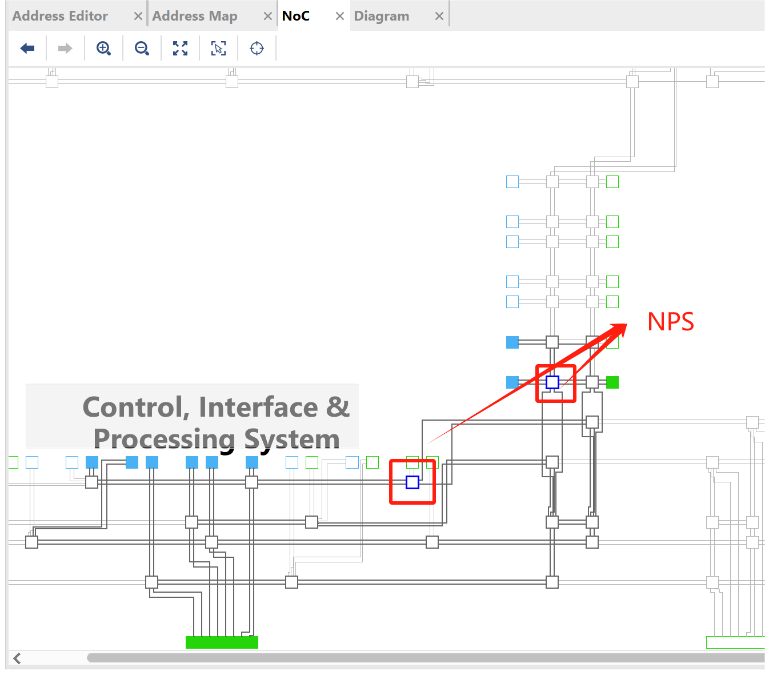

3、NoC Packet Switch (NPS)

連接NoC塊以形成完整NoC網絡交換。每個NPS都是全雙工4x4 Switch,通過Switch至少有兩個延遲周期。

NSU512(PL) NSU512(PL)

4、NoC Inter-Die Bridge (NIDB)

在多個SSIT芯片之間橋接垂直NoC(VNoC)。

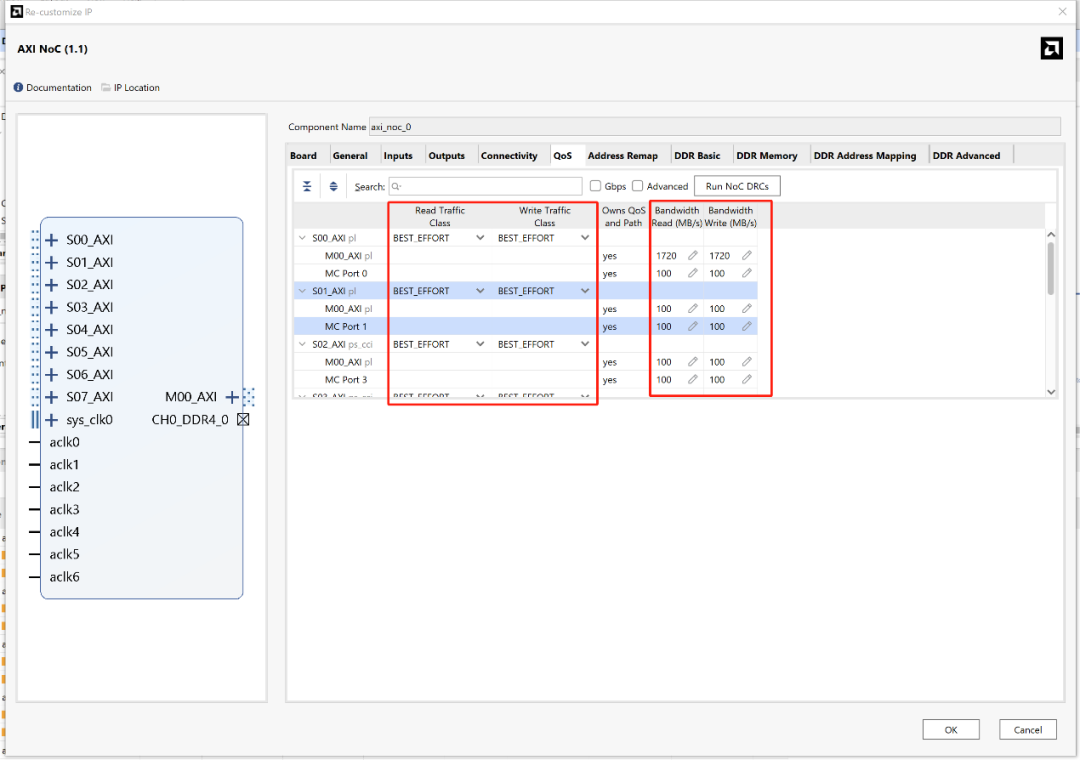

Quality of Service(QoS)

Traffic Class與Read and Write Bandwidth

1、流量類別(Traffic Class)

定義了連接上的流量在NoC編譯器和硬件中的優先級。流量類在NMU上設置,適用于從該NMU開始的所有路徑。Traffic Class支持如下3種模式:

Low Latency:盡量減少結構延遲,DDR仲裁中優先級最高;

Isochronous:保證最大延遲;DDR隊列中設定超時提前處理;

Best Effort:最低優先級,適合非關鍵流量。

2、帶寬需求(Bandwidth Requirement)

單獨設置讀/寫帶寬(單位MB/s或Gb/s);

Vivado NoC Compiler會基于此進行資源分配與仲裁優化。

性能優化建議

關鍵流量優先保障:通過QoS將低延遲或同步流量優先級調高;

減少跨交換機跳數:布局時盡量縮短NMU→NSU的路徑;

合理位寬分配:帶寬與功耗需權衡,避免過度配置浪費資源;

多Die優化:跨Die數據盡量走專用VNoC通道,減少延遲;

路徑可視化:在NoC Compiler拓撲圖中檢查關鍵路徑是否經過不必要的節點。

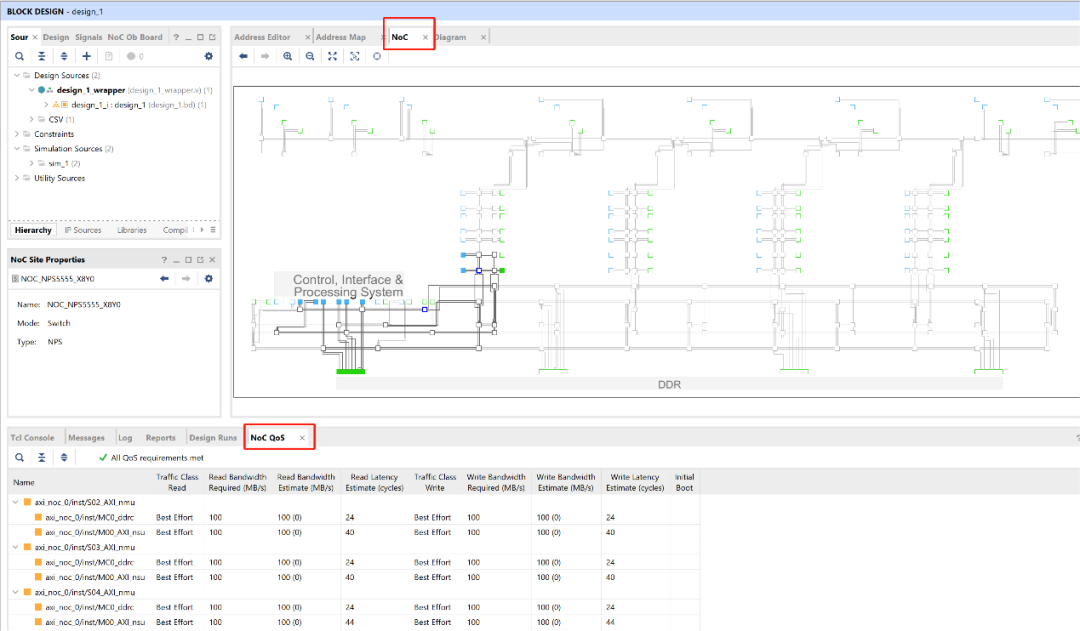

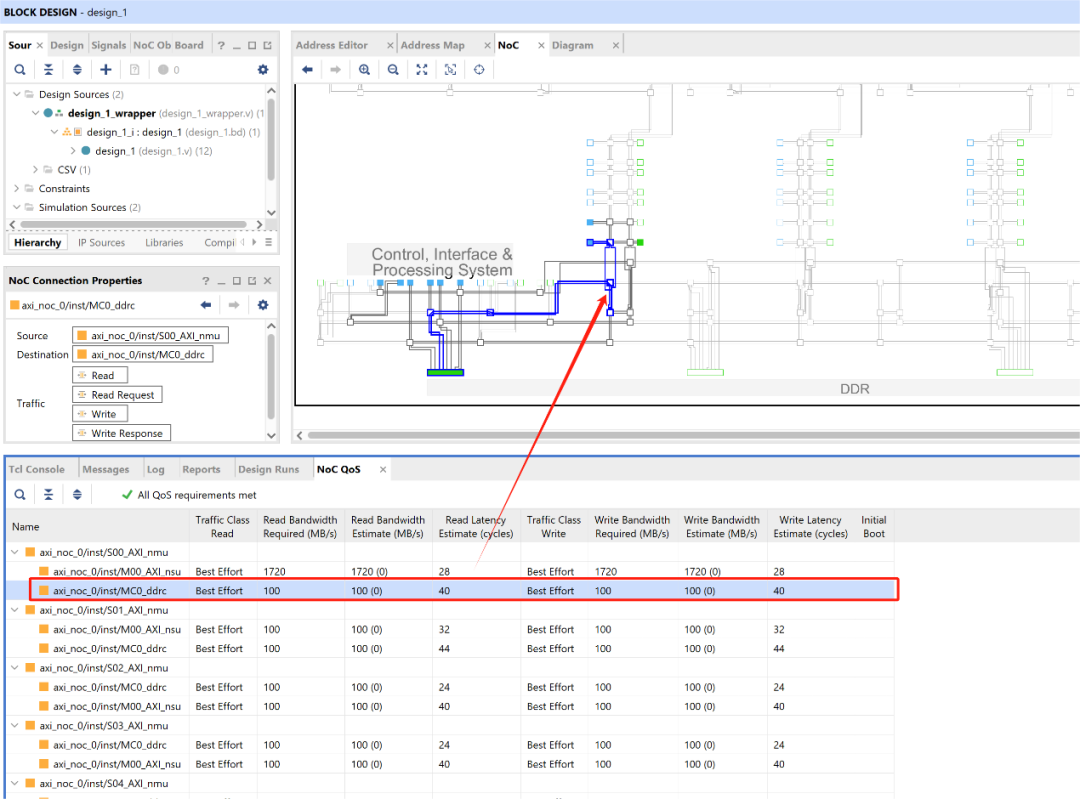

在Vivado BD的NoC界面,可以看到DDRNMUNSUNPSQoS等。

點擊如下QoS選擇卡中的條目,可以看到此路徑下的NoC拓撲。

關于安富利

安富利是全球領先的技術分銷商和解決方案提供商,在過去一個多世紀里一直秉持初心,致力于滿足客戶不斷變化的需求。通過遍布全球的專業化和區域化業務覆蓋,安富利可在產品生命周期的每個階段為客戶和供應商提供支持。安富利能夠幫助各種類型的公司適應不斷變化的市場環境,在產品開發過程中加快設計和供應速度。安富利在整個技術價值鏈中處于中心位置,這種獨特的地位和視角讓其成為了值得信賴的合作伙伴,能夠幫助客戶解決復雜的設計和供應鏈難題,從而更快地實現營收。

-

amd

+關注

關注

25文章

5657瀏覽量

139140 -

片上網絡

+關注

關注

0文章

34瀏覽量

12089 -

NoC

+關注

關注

0文章

43瀏覽量

12105 -

Vivado

+關注

關注

19文章

848瀏覽量

70553

原文標題:AMD技術干貨|NoC的使用及注意事項

文章出處:【微信號:AvnetAsia,微信公眾號:安富利】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

隨著AMD 7nm制程芯片的加速落地,AMD將爆發更強悍的性能

AMD:7nm明年有望出現

AMD公開VEGA GPU架構使用7nm工藝

AMD 7nm處理器和Intel 7nm處理器有什么區別?

Q3季度AMD芯片均價大漲40% 7nm正在給AMD帶來豐厚回報

AMD或使用三星7nm制程來制造RX 5500系列顯卡

AMD Radeon Pro W5700系列專業卡開售,核心基于7nm Navi 10

超越蘋果和海思,AMD在臺積電7nm產能占比第一

AMD 7nm U/H系列處理器支持面容和指紋登陸

AMD推出銳龍4000系列APU處理器 7nm銳龍APU尤其重要

AMD加速甩掉14nm工藝,IO核心有望使用臺積電7nm工藝

消息稱AMD明年成7nm最大客戶:暴增80%

AMD Versal自適應SoC器件Advanced Flow概覽(下)

AMD 7nm Versal系列器件NoC的使用及注意事項

AMD 7nm Versal系列器件NoC的使用及注意事項

評論