據4月26日網友Izzukias分享的一份114頁AMD官方文件確認,將于明年發布的Zen 5 APU具有強大性能,Strix Halo APU將運用多芯粒(Chiplet)設計,其內嵌的40個CU(即20xWGP)超越了現今主流獨立顯卡。

文件進一步夯實之前的曝料,AMD Zen 5 APU將包含常規版Strix Point和增強型“大杯”Strix Halo兩款產品。

Strix Point

常規版Strix Point將保持單芯片設計,但核心數量從8核16線程的Zen 4提升至12核24線程的Zen 5,核顯部分由12個RDNA 3.1 CU增至16個RDNA 3.5 CU,NPU運算能力提高至50 TOPS,功耗范圍在45W~65W之間。

“大杯”Strix Halo

Strix Halo APU則更加強勁,采用多芯粒設計,搭載兩個8核心Zen 5芯片,共計16核32線程,同時配備40個RDNA 3.5 CU核顯,相較之下,AMD RX 7600 XT獨顯僅有32個CU。

廠家表示,Strix Halo的GPU性能堪比RTX 4060 Laptop,NPU運算能力最高可達60 TOPS。Strix Halo APU的官方TDP設定為70W,但廠家可根據設備散熱設計進行調整,最大可達130W以上。

-

芯片

+關注

關注

463文章

54007瀏覽量

465889 -

amd

+關注

關注

25文章

5682瀏覽量

139928 -

線程

+關注

關注

0文章

509瀏覽量

20825

發布評論請先 登錄

英偉達+聯發科,打入游戲本市場?

Cadence工具如何解決芯粒設計中的信號完整性挑戰

UCIe協議代際躍遷驅動開放芯粒生態構建

面向芯粒設計的最佳實踐

借助Arm芯粒技術構建計算未來

芯粒技術的專利保護挑戰與應對策略

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

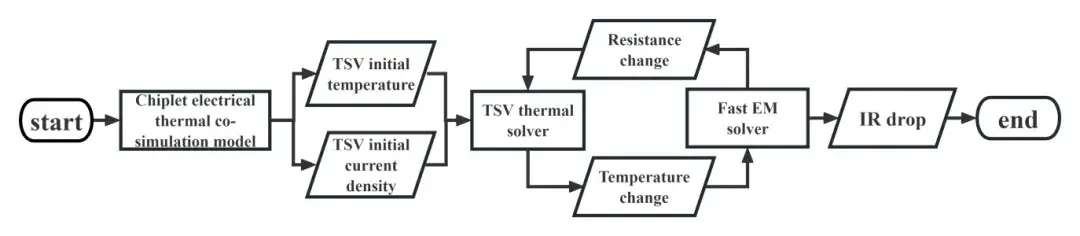

微電子所在芯粒集成電遷移EDA工具研究方向取得重要進展

從Ascend 910D看芯粒創新,半導體行業將迎重大變局

江波龍企業級DDR5 RDIMM率先完成AMD Threadripper PRO 9000WX系列兼容性認證

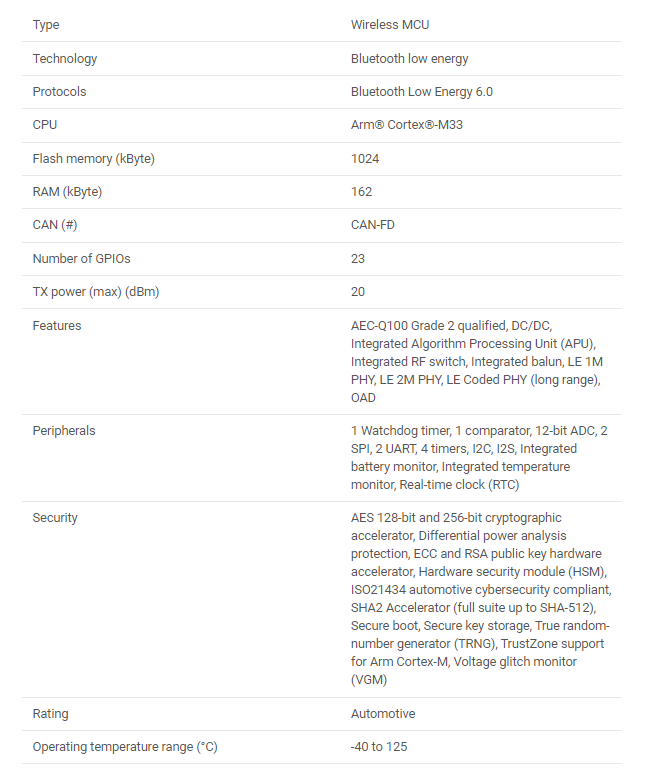

TI芯品CC2745P10-Q1具有1MB閃存、HSM、APU、CAN-FD 和 +20dBm 的汽車級SimpleLink? 低功耗 Bluetooth6.0無線MCU

多芯粒2.5D/3D集成技術研究現狀

AMD明年Zen5 APU性能確切,Strix Halo APU將應用多芯粒

AMD明年Zen5 APU性能確切,Strix Halo APU將應用多芯粒

評論