在半導體設計中,“簽核”通常被視為一個里程碑。但實際上,這涵蓋了多個具有特定目標的獨立驗證階段。

功能簽核和RTL簽核就是其中的兩個環節,二者各自側重于正確性的不同方面,缺一不可。功能簽核主要驗證設計是否按預期運行,而RTL簽核則側重于寄存器傳輸級實現的結構是否合理,能否為后續的綜合和物理實現做好準備。

目前,IP模塊持續增多、多個異步時鐘域并存,電源管理方案也愈加嚴苛,這讓片上系統(SoC)的復雜性不斷增加,與此同時,這些簽核階段也變得越來越專業化。驗證流程必須確認設計的意圖和完整性,才能邁入下一階段。然而,功能層級與RTL層級“完成標準”的界限并不總是清晰,這個問題在覆蓋范圍、功耗設計意圖和時序就緒性方面存在重疊時尤為突出。

值得慶幸的是,新思科技提供了一套完整的工具,為RTL和功能簽核帶來了結構化與智能化的雙重保障。

什么是功能簽核?

功能簽核旨在確認設計是否準確實現了預期功能特性。該驗證在RTL抽象層執行,此時設計通常仍然以Verilog或VHDL等源代碼表示,尚未進行任何綜合或布局轉換。其目標是驗證RTL是否在所有定義的應用場景、運行模式和邊界條件下滿足設計規格,而暫不考慮后續物理實現問題。

此階段通常涉及仿真和形式化分析。開發者常使用基于通用驗證方法(UVM)的測試平臺來施加激勵并檢查預期響應。他們通過覆蓋組和斷言來定義功能覆蓋率,以此衡量在仿真期間是否發生了重要事件和行為。代碼覆蓋率則作為補充指標,用于跟蹤是否RTL的所有部分都已執行。

雖然代碼覆蓋率相對容易達到高值,但功能覆蓋率仍更具主觀性,具體取決于規格的質量和驗證團隊對實際場景的預測能力。即使覆蓋率指標顯示已達100%,開發者仍常懷疑測試是否涵蓋了關鍵部分。這種不確定性導致在流片后仍需持續開展驗證工作。

為了消除這種不確定性,我們在VSO.ai解決方案中引入AI驅動的機器學習技術,該解決方案和新思科技業界領先的VCS功能驗證解決方案集成,能夠識別未測試行為、生成針對性輸入并簡化測試用例選擇。VSO.ai不僅能提高覆蓋結果,還增強了用戶對驗證全面性和有效性的信心。

什么是RTL簽核?

相比于行為,RTL簽核更側重于結構正確性。它可用于確認RTL代碼是否已實施就緒,且不存在可能影響綜合、時序或物理集成的問題。

RTL簽核期間執行的重要檢查包括跨時鐘域(CDC)、跨復位域(RDC)、Lint檢查和低功耗設計意圖驗證。這些分析旨在發現諸如跨獨立時鐘域的信號不同步、復位邏輯不完整或違反命名慣例和設計規則等風險。借助新思科技VC SpyGlass和新思科技VC Formal等工具,我們能夠在流程早期識別這些問題,以免它們在門級或布局層級成為缺陷。

功耗感知驗證同樣是RTL簽核的核心原則。開發者需要確認是否已借助統一功耗格式(UPF)等技術正確定義和集成隔離單元、電壓轉換器和保留策略。這些結構在純RTL層級通常是不可見的,因此需要通過綜合或靜態分析才能揭示它們在實際情境中的行為。

RTL和功能簽核的交集

雖然功能和RTL簽核用途不同,但二者緊密相連。一個用于驗證設計行為,另一個則用于驗證結構可行性。

兩者都是設計收斂的必要條件,且能互相揭示另一種方法無法發現的問題。

二者在時間上常常并行推進,但所要解答的問題卻有著本質區別。

一個領域的問題可能會影響另一個領域。

例如,在RTL簽核過程中發現同步器缺失,這可能會導致間歇性故障,而這類問題單純依靠功能覆蓋率指標難以捕捉。同樣地,功能簽核中如果存在未經測試的狀態轉換,即使通過了結構檢查,也可能導致芯片故障。

將這兩個簽核階段視為既相互獨立又協同配合的過程,有助于避免盲目樂觀,幫助團隊選擇合適的工具和技術解決正確的問題。仿真和測試平臺更適合探索應用場景和邏輯條件,而靜態分析則更擅于發現設計規則違例或同步器缺失。

對于這兩個階段,新思科技Verdi可以作為通用調試平臺,幫助開發者查看、分析和識別故障與覆蓋率缺口的根本原因。

現代簽核中的AI應用

隨著驗證復雜性不斷增加,完成簽核所需的工作量也與日俱增。傳統驗證流程中,工程師往往需要耗費數周時間疲于捕捉那些難以復現的極端案例,或是反復調試測試輸入序列。如今,AI技術正在重塑這一現狀。

VSO.ai解決了功能簽核中最棘手的問題之一,即如何實現重要的覆蓋率目標。區別于單純依賴隨機測試生成或人工調整的技術,該方案側重于分析仿真數據、識別缺口并自主生成更有可能觸發未測試行為的輸入條件。這些功能顯著降低了人工干預強度,大幅縮短了有效覆蓋率目標的達成周期。

我們最新一代Verdi平臺還借助AI技術增強了故障分類和根本原因分析,大幅提升了工作效率。

AI有助于提高覆蓋率本身的質量,同時不可達性分析(VC Formal的一項關鍵功能)有助于確定RTL中永遠不會被執行的部分。這使得設計團隊能夠將無用代碼排除在覆蓋率目標之外,避免在那些對功能可信度沒有幫助的目標上浪費時間。

展望未來,智能體AI將帶來更大潛力。通過將自然語言描述的設計規范轉化為形式化斷言,開發者團隊將能更快、更準確地定義功能覆蓋率。

構建完整的驗證信心體系

功能簽核和RTL簽核代表著同一驗證工作這枚硬幣的兩面,一面確認設計的行為符合預期,而另一面則確認構建方式足以支持可靠的實現。

兩者同等重要,無法相互替代。在如今SoC日益異構化且對功耗極為敏感的背景下,忽視任何一個簽核里程碑都將引入風險,且這種風險難以通過硅后調試徹底修復。

-

半導體

+關注

關注

339文章

31062瀏覽量

265701 -

RTL

+關注

關注

1文章

395瀏覽量

62801 -

新思科技

+關注

關注

5文章

970瀏覽量

52971

原文標題:RTL與功能簽核:新思科技如何為異構低功耗SoC構建雙重驗證堡壘?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

樂鑫 ESP32-H4:新一代雙核超低功耗 SoC,面向長續航與 HMI

新思科技發布全新軟件定義硬件輔助驗證解決方案

基于低功耗藍牙SoC的新國標充電寶方案

西門子Questa One驗證解決方案引入智能體AI功能

新思科技EDA工具和車規IP助力芯粒架構汽車SoC設計

深入解析CC430系列SoC:低功耗無線通信的理想之選

什么是低功耗設計,如何評估低功耗MCU性能?

新思科技HAPS-200助力阿里巴巴達摩院加速玄鐵C930開發驗證

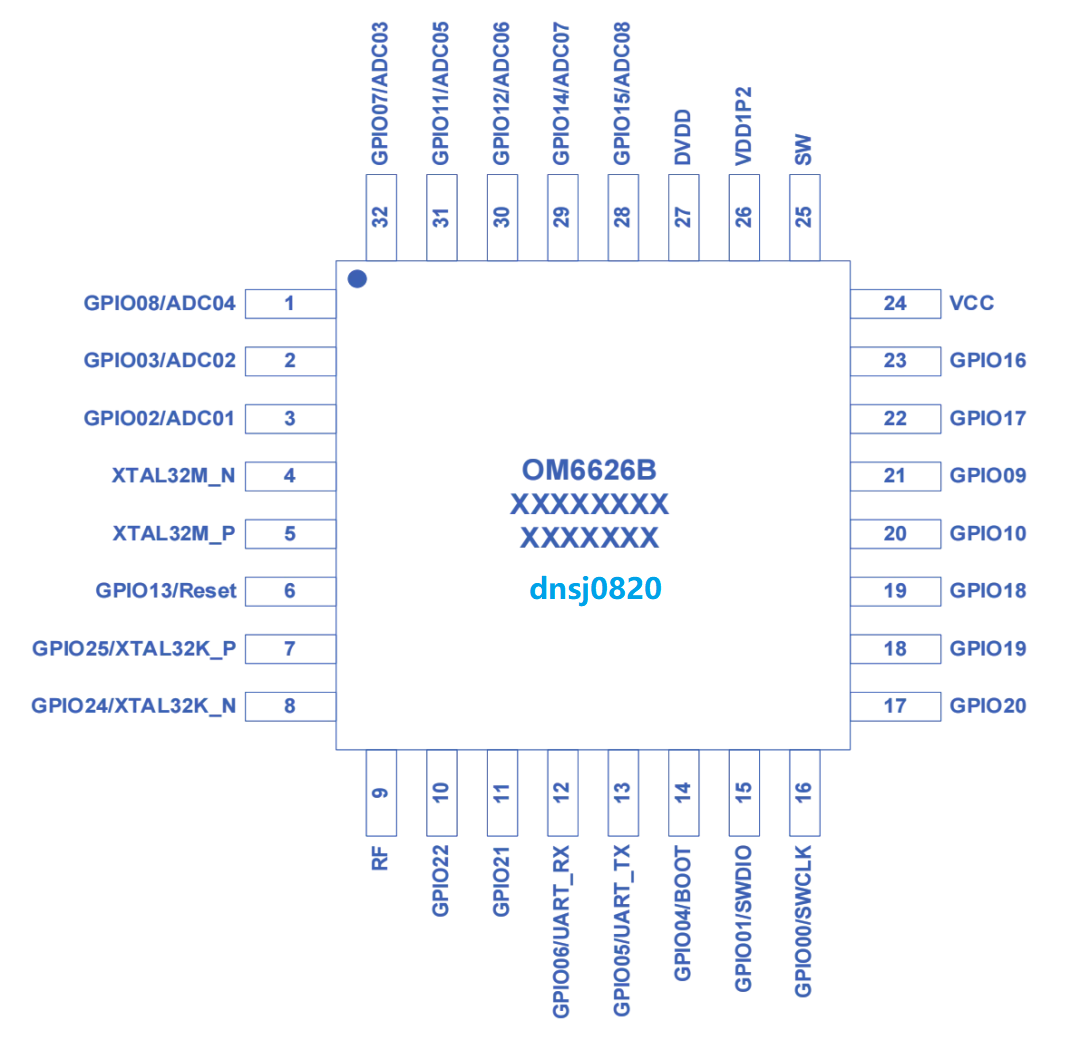

高性能超低功耗藍牙電子價簽方案 OM6626 NRF52832

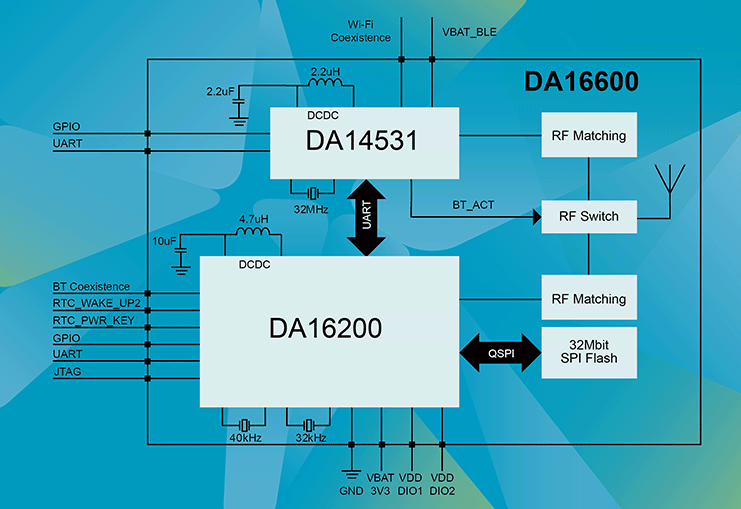

DA16600MOD超低功耗Wi-Fi低功耗藍牙組合模塊數據手冊

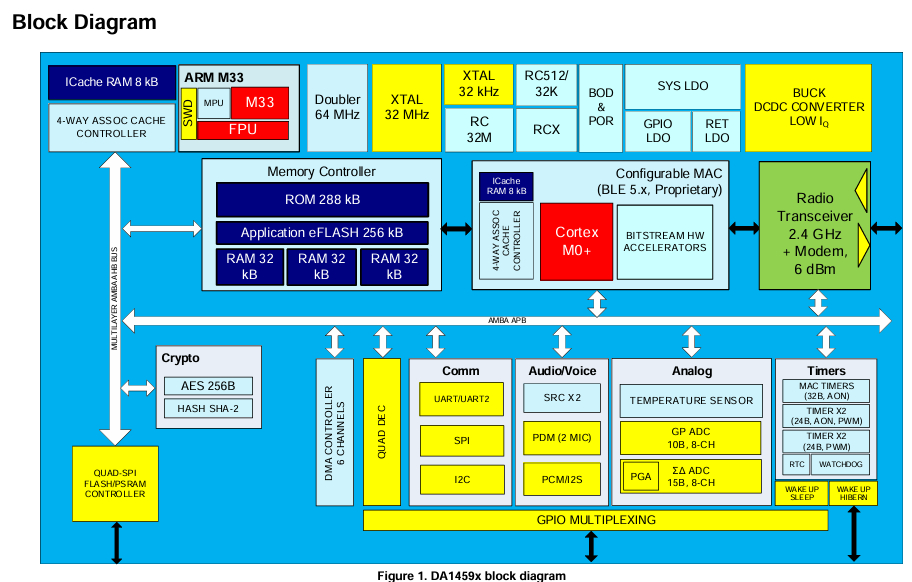

DA14594 SmartBond雙核低功耗藍牙5.3 SoC 數據手冊和產品介紹

新思科技RTL與功能簽核助力低功耗SoC驗證

新思科技RTL與功能簽核助力低功耗SoC驗證

評論