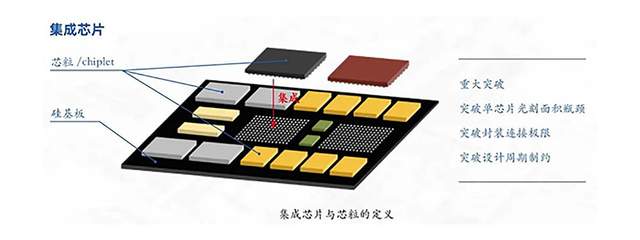

? 在過(guò)去的五年里,處理器已經(jīng)從單個(gè)硅片變成了一組較小的小芯片,這些小芯片共同作用就像一個(gè)大芯片一樣。這種方法意味著 CPU 的功能部件可以使用最適合每個(gè)部件的技術(shù)來(lái)構(gòu)建。AMD的產(chǎn)品技術(shù)架構(gòu)師Sam Naffziger是這種方法的早期支持者。Naffziger 最近回答了IEEE Spectrum就該主題提出的五個(gè)小芯片大小的問(wèn)題。

問(wèn):您認(rèn)為基于小芯片的處理器面臨哪些主要挑戰(zhàn)?

Sam Naffziger:我們五六年前開(kāi)始推出EPYC和Ryzen CPU 系列。當(dāng)時(shí),我們?nèi)隽艘粡埾喈?dāng)廣泛的網(wǎng)來(lái)尋找最適合連接芯片(小硅塊)的封裝技術(shù)。這是一個(gè)由成本、性能、帶寬密度、功耗以及制造能力組成的復(fù)雜方程式。提出出色的封裝技術(shù)相對(duì)容易,但實(shí)際大批量、經(jīng)濟(jì)高效地制造它們卻是完全不同的事情。所以我們?cè)谶@方面投入了大量資金。

問(wèn):小芯片將如何改變半導(dǎo)體制造工藝?

Naffziger:這絕對(duì)是該行業(yè)正在努力解決的問(wèn)題。這就是我們今天所處的位置,也是我們 5 到 10 年后可能達(dá)到的位置。我認(rèn)為今天的技術(shù)基本上都是通用的。它們可以很好地與單片芯片對(duì)齊,也可以用于小芯片。有了小芯片,我們就擁有了更專(zhuān)業(yè)的知識(shí)產(chǎn)權(quán)。因此,未來(lái)人們可以設(shè)想專(zhuān)業(yè)化的工藝技術(shù)并獲得性能優(yōu)勢(shì)、成本降低等。但這并不是當(dāng)今行業(yè)的現(xiàn)狀。

問(wèn):小芯片將如何影響軟件?

Naffziger:我們架構(gòu)的目標(biāo)之一是讓它對(duì)軟件完全透明,因?yàn)檐浖茈y改變。例如,我們的第二代 EPYC CPU 由被計(jì)算芯片包圍的集中式 I/O [輸入/輸出] 小芯片組成。當(dāng)我們采用集中式 I/O 芯片時(shí),它減少了內(nèi)存延遲,消除了第一代的軟件挑戰(zhàn)。

現(xiàn)在,借助 [ AMD Instinct] MI300(AMD 即將推出的高性能計(jì)算加速器),我們正在集成 CPU 和 GPU 計(jì)算芯片。這種集成的軟件含義是它們可以共享一個(gè)內(nèi)存地址空間。因?yàn)檐浖槐負(fù)?dān)心管理內(nèi)存,所以編程更容易。

問(wèn):有多少架構(gòu)可以分離到小芯片上?

Naffziger:我們正在尋找擴(kuò)展邏輯的方法,但 SRAM 更具挑戰(zhàn)性,而模擬的東西絕對(duì)無(wú)法擴(kuò)展。我們已經(jīng)采取了將模擬與中央 I/O 小芯片分離的步驟。借助3D V-Cache(一種與計(jì)算芯片 3D 集成的高密度緩存小芯片),我們分離出了 SRAM。我預(yù)計(jì)未來(lái)會(huì)有更多此類(lèi)專(zhuān)業(yè)化。物理學(xué)將決定我們可以做到多細(xì)粒度,但我對(duì)此持樂(lè)觀態(tài)度。

問(wèn):怎樣才能將不同公司的小芯片混合并匹配到同一個(gè)封裝中才能成為現(xiàn)實(shí)?

Naffziger:首先,我們需要一個(gè)關(guān)于接口的行業(yè)標(biāo)準(zhǔn)。UCIe是 2022 年推出的小芯片互連標(biāo)準(zhǔn),是重要的第一步。我認(rèn)為我們將看到這種模式的逐步發(fā)展,因?yàn)樗鼘?duì)于提供更高水平的每瓦性能和每美元性能至關(guān)重要。然后,您將能夠組裝一個(gè)針對(duì)特定市場(chǎng)或客戶的片上系統(tǒng)。

-

處理器

+關(guān)注

關(guān)注

68文章

20255瀏覽量

252345 -

amd

+關(guān)注

關(guān)注

25文章

5684瀏覽量

139992 -

chiplet

+關(guān)注

關(guān)注

6文章

495瀏覽量

13604

原文標(biāo)題:關(guān)于Chiplet,AMD的5個(gè)經(jīng)驗(yàn)分享

文章出處:【微信號(hào):AI_Architect,微信公眾號(hào):智能計(jì)算芯世界】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

GPS時(shí)鐘授時(shí)裝置常見(jiàn)問(wèn)題與實(shí)戰(zhàn)經(jīng)驗(yàn)分享

多Chiplet異構(gòu)集成的先進(jìn)互連技術(shù)

如何突破AI存儲(chǔ)墻?深度解析ONFI 6.0高速接口與Chiplet解耦架構(gòu)

躍昉科技受邀出席第四屆HiPi Chiplet論壇

得一微電子受邀出席第四屆HiPi Chiplet論壇

解構(gòu)Chiplet,區(qū)分炒作與現(xiàn)實(shí)

CMOS 2.0與Chiplet兩種創(chuàng)新技術(shù)的區(qū)別

手把手教你設(shè)計(jì)Chiplet

基于AMD Versal器件實(shí)現(xiàn)PCIe5 DMA功能

從技術(shù)封鎖到自主創(chuàng)新:Chiplet封裝的破局之路

Chiplet與先進(jìn)封裝設(shè)計(jì)中EDA工具面臨的挑戰(zhàn)

淺談Chiplet與先進(jìn)封裝

Chiplet技術(shù)在消費(fèi)電子領(lǐng)域的應(yīng)用前景

奇異摩爾受邀出席第三屆HiPi Chiplet論壇

Chiplet:芯片良率與可靠性的新保障!

關(guān)于Chiplet,AMD的5個(gè)經(jīng)驗(yàn)分享

關(guān)于Chiplet,AMD的5個(gè)經(jīng)驗(yàn)分享

評(píng)論