本文要點

集成電路與 PCB 中均存在可能由開關數字信號激發的寄生效應。

所有高速數字集成電路都會產生一定的同步開關噪聲,噪聲的強度由集成電路結構和 PCB 布局中的寄生參數決定。

若要區分同步開關噪聲與其他信號完整性問題,需要使用封裝電感、I/O 線路和負載電容進行一些簡單的計算。

觀察眼圖中的比特流或示波器上開關數字信號的波形,您可能會發現多種信號完整性問題同時顯現,這是因為這些問題并非孤立存在。外部電路噪聲、功率波動引起的抖動、背景熱噪聲、過沖、反射以及同步開關噪聲都可能疊加在信號上。同步開關噪聲(亦稱“地彈”)尤為值得關注,因為它常被誤判為其他信號完整性問題,即串擾和反射引起的過沖。

現代 CMOS 集成電路的結構為同步開關噪聲的產生創造了條件

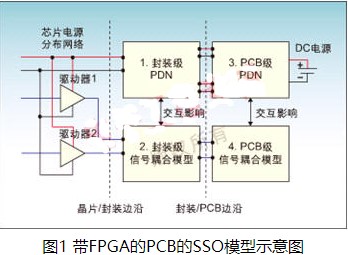

若要探究此類噪聲的真正成因,我們需要分析集成電路中多個緩沖器同步開關時的工作機理(因此稱為“同步開關噪聲”)。集成電路和 PCB 的結構會產生寄生效應,從而在集成電路切換狀態的瞬間激發強烈噪聲。從電路角度剖析 PCB 與集成電路,有助于我們了解切換過程中的潛在問題以及使用電容的原因。

同步開關噪聲的產生機理

若要探究同步開關噪聲的成因,我們需要分析CMOS 緩沖器的結構、同一封裝內各緩沖器之間的連接方式以及多個集成電路之間的連接方式。所有 CMOS 緩沖器均連接至同一個接地網絡,并在系統主時鐘的驅動下切換狀態。當多個緩沖器連接至同一接地網絡并同步開關時,會產生強烈的振蕩,并疊加至目標信號電平上。

由于所有緩沖器同步開關,其產生的噪聲會疊加至電路內的其他緩沖器上。在測量 I/O 線路相對于接地網絡的輸出信號時,由此產生的振蕩在時域中清晰可見。通常情況下,我們可以使用示波器和高衰減比的電感式近場探頭進行測量。

同步開關噪聲特性

關于同步開關噪聲,需掌握以下要點:

所有同步開關噪聲均與 I/O 傳輸線中的電容和電感、接收器的輸入電容以及互連兩端的封裝電感密切相關。

當更多緩沖器同步開關時,產生的振蕩幅度更大(電壓峰-峰值更高)。

雖然無法完全消除此類噪聲,但只要選用合適的旁路電容,即可將振蕩幅度抑制在足夠小的范圍,避免干擾接收端器件。

最理想的情況是,使振蕩達到臨界阻尼或過阻尼,但這需要在 I/O 引腳上添加一個較大的串聯電阻。

要了解此類噪聲的成因,以及同步開關噪聲產生的物理機制,我們可以分析單個緩沖電路。

單個緩沖電路中的同步開關噪聲

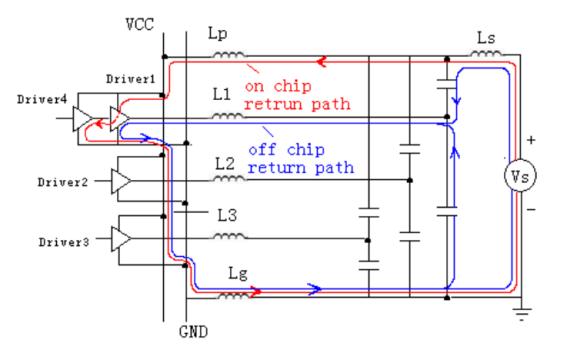

單個緩沖電路中的開關噪聲與I/O 傳輸線的電感和電容、接收器的負載電容、引腳封裝電感以及信號路徑中導體的直流電阻密切相關。下圖展示了從關斷狀態切換到導通狀態過程中的電流返回路徑。正如我們所見,電壓回路與電流路徑均流經一個串聯 LC 電路。

從關斷狀態切換到導通狀態過程中的電流返回路徑

由于上述串聯 LC 電路的電阻趨近于零,其瞬態響應預期表現為欠阻尼振蕩。這是所有阻尼極小的串聯 LC 電路的典型行為。當高速數字集成電路中的多個緩沖器同步開關時,這些寄生效應便會引發前文所說的振鈴現象。我們通常在集成電路的電源引腳與接地引腳之間添加一個旁路電容,通過旁路電容的放電來補償接地參考電平的上移。

經驗豐富的設計人員可能認為“這看起來很像串擾”,這種判斷并無不當。不過,也可能是連接兩個器件的短走線發生了共振。

地彈、串擾與諧振

從示波器波形來看,這三種信號完整性效應的表現可能非常相似,而且還可能同時發生,從而形成時域中所見的復雜行為。若要區分這些效應,需要利用互連線中的電容和電感參數進行一些基礎計算。

專業的 PCB 設計工具通常集成 3D 場求解器,可用于從 PCB 布局中提取串擾耦合參數。基于這些參數,不僅能確定任何電壓峰值的預期大小與瞬態振蕩頻率,還可直接獲得串擾引起的時域響應。這有助您判斷互連線中的噪聲究竟是同步開關噪聲、串擾、諧振,還是這些效應的疊加。

-

集成電路

+關注

關注

5452文章

12572瀏覽量

374534 -

pcb

+關注

關注

4404文章

23878瀏覽量

424251 -

同步開關噪聲

+關注

關注

0文章

4瀏覽量

8816

發布評論請先 登錄

高手告訴你,FPGA同步開關噪聲就得這么分析!

如何應對FPGA同步開關的SSN噪聲的挑戰

FPGA上同步開關噪聲的分析

同步開關輸出噪聲建模方法及仿真研究

電源完整性之同步開關噪聲SSN

技術資訊 I 如何減少接地噪聲

技術資訊 | 開關穩壓電路中的寄生噪聲

技術資訊 I 面向電路的噪聲耦合抑制技術

同步開關噪聲產生的原因和影響

技術資訊 I 如何識別同步開關噪聲

技術資訊 I 如何識別同步開關噪聲

評論