本期為大家帶來的是《雷達應用中射頻轉換器的無雜波電源(第 1 部分)》,介紹了一種基于低噪聲電源管理架構的射頻采樣系統設計方案,以解決相控陣雷達和 5G 通信應用中因開關電源噪聲耦合導致的 ADC 動態性能下降問題。

引言

尋找噪聲源時,電源引腳也被視為輸入,且所有有源器件都具有引腳。在當今的實際設計中,進行射頻 (RF) 相關設計時應考慮電源引腳。任何電源輸入端的噪聲和耦合都會因額外的雜波而導致雷達應用中的性能不達標。

盡管本文的重點是數據轉換器,尤其是在千兆赫茲頻段中進行采樣的射頻轉換器,但是此處討論的原理適用于所有集成電路,包括低頻或高頻應用信號鏈中的全差分放大器、混頻器、低噪聲放大器、增益塊、射頻開關以及數字步進衰減器。

本質上,模數轉換器 (ADC) 是一個巨型混頻器;輸入端的任何信號都將卷積到其輸出頻譜。任何輸入都是如此。可假設“泄漏噪聲”(也稱為白噪聲或雜散)僅來自時鐘和/或模擬輸入。但是,對于先進雷達系統之類的應用,開關模式電源 (SMPS) 也會泄漏噪聲并嚴重破壞頻譜性能。

進入系統板的高噪聲總線軌電壓會偏置 ADC 的各個部分,通常使用低壓差穩壓器 (LDO) 來降低該電壓。但是,如需在組件尺寸和效率之間進行權衡,這并非更實用的方法。這種情況下,某些 SMPS 技術會更適合這些應用,它們對 SMPS 輸出噪聲具有更深刻的認知。

本系列由兩部分組成,第一部分介紹當噪聲耦合到 ADC 的電源時會發生的情況、噪聲如何通過 ADC 的電路進行耦合以及一些常用的電源權衡。

電源噪聲耦合

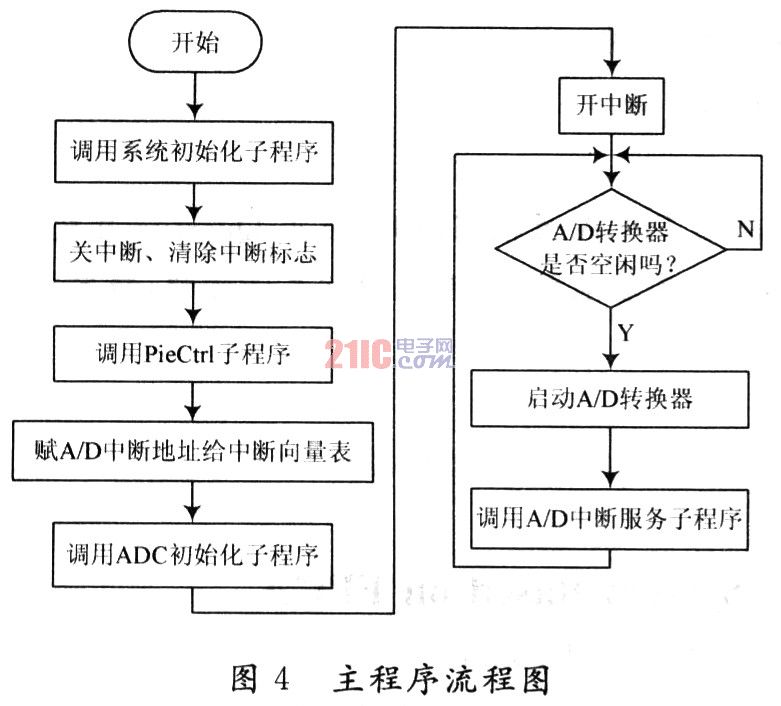

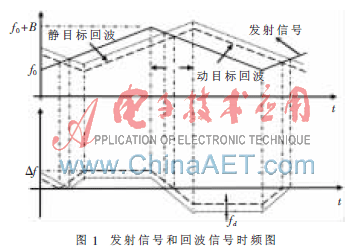

提供給 ADC 的帶有噪聲的采樣時鐘最終會對 ADC 性能造成災難性影響。與此相關的論文有很多,因此下文僅是一種概括性的闡述。當認為時鐘低于標準時,ADC 的信噪比 (SNR) 和噪聲頻譜密度將偏離其數據表規格。如圖 1 所示,快速傅里葉變換頻譜重疊圖展示了抖動時鐘與應用于 ADC 的純凈采樣時鐘之間的差異。請注意,使用低于標準的采樣時鐘時,SNR 會降低 ~3dB。這種下降會極大地減小系統的總動態范圍。

圖 1 帶有噪聲的采樣時鐘與純凈采樣時鐘之間的對比

圖 2 與時鐘輸入的 ADC 輸出頻譜耦合的寬帶噪聲或近端噪聲

為了進一步說明這一點,如果時鐘具有任何寬帶噪聲或近端噪聲,則這兩種噪聲都會在輸出頻譜中占據很大分量。圖 2 中展示了這一點。此前,建議將 ADC 視為巨型混頻器;即使 ADC 處于理想狀態,僅以寬帶或近端方式耦合到時鐘的任何噪聲最終都將卷積到輸出頻譜。

同樣的概念也可應用于電源輸入。如圖 2 所示,通過將基頻(fIN)同樣的概念也可應用于電源輸入。如圖 2 所降低到 DC,DC 附近的任何寬帶噪聲或近端噪聲都將卷積到輸出頻譜。請參見圖 3。

圖 3 與電源輸入的 ADC 輸出頻譜耦合的寬帶噪聲或近端噪聲

噪聲通過時鐘進行耦合的方式與噪聲通過電源引腳進行耦合的方式略有不同。在時鐘示例中,時鐘節點的內部電路與模擬輸入的采樣保持結構緊密相連。因此,該位置是讓通過時鐘引腳耦合的任何噪聲設法進入 ADC 內部信號路徑的理想之選(如圖 2 所示)。在此情況下,耦合路徑幾乎達到零衰減。

注意,圖 4 所示的 ADC 內部電路包含一個衰減符號。此符號表示 ADC 對通過電源引腳耦合的任何噪聲或信號的抑制(抑制程度以電源抑制比 (PSRR) 衡量)。最終,此衰減定義了 ADC 內部電路設計的耦合抑制量,即PSRR。某些電路設計拓撲能夠比其他拓撲提供更少的噪聲衰減,因此更多噪聲將泄漏到 ADC 的數字化路徑中,導致 ADC 性能降低。圖 5 舉例說明了兩個不同的電路結構。

得益于連接到電源軌的高隔離度金屬氧化物半導體結構,圖 5a 中所示的結構類型可帶來更好的噪聲衰減和耦合效果(從而改善 PSRR)。采用簡單的上拉電阻設計,圖 5b 中的電路能夠實現較小的噪聲衰減。

寄生效應是區分良好和不良 PSRR 容差的另一個因素。目前,許多 ADC 設計以及許多其他器件中都采用更小的工藝幾何尺寸和更低的電源電壓范圍。這些幾何尺寸又會導致電壓閾值變小,從而對噪聲更敏感。

圖 4 電源衰減耦合路徑示例

圖 5 連接到電源引腳的ADC 內部電路結構的通用示例

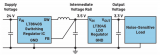

電源權衡:SMPS 與 LDO

高速 ADC 對電源噪聲敏感,因此一種最大限度地減少噪聲的主流方法是將開關模式電源 (SMPS)納入設計方案 ,從而降低系統中有效的主總線軌電壓(例如,28V 或15V)。SMPS 提供一個中軌電壓,使 LDO 能夠向相應的ADC 電源域提供純凈電壓。請參閱圖 6。

圖 6 ADC12DJ5200RF 評估模塊(EVM)的SMPS 和 LDO 設計

與線性電源相比,SMPS 設計具有若干優點。功率損耗的減少轉化為更高效、更優的解決方案。整個電路板上眾多 LDO 的電壓降形成的功率損耗所帶來的功率耗散會降低,同時整個 SMPS 電源電路的尺寸使得可用 PCB面積增大。單獨使用 SMPS 時必須仔細考慮所選的開關電源、濾波和電路設計布局才能實現所要的結果,但這完全可以實現。請參閱圖 7。

圖 7 ADC12DJ5200RF EVM 的“僅 SMPS” 設計

ADC 的交流性能 (SNR/SFDR) 在兩種電源設計之間處于同等水平,因為以 10.4GSPS 采樣率進行采樣時模擬輸入頻率為 1.5GHz 的。此基本測試令人相信 SMPS 設計是可靠,如圖 8 所示。

圖 8 ADC12DJ5200RF 交流性能比較

結論

功率 IC 設計中的新技術突破已讓位于“僅 SMPS”方法,因此可將該方法運用于對噪聲敏感的許多應用(例如雷達和高端儀器)。

本文使用了 TPS62913 低紋波和低噪聲降壓轉換器來展示這些權衡之間的差異。此降壓轉換器經過專門設計,有助于讓電源設計滿足噪聲敏感型高速應用對于噪聲和紋波的要求。第 2 部分第后續文章將使用 12 位 ADC12DJ5200RF射頻采樣 ADC 來定義和測量 PSRR 和電源調制比,并舉例說明了如何正確進行功率管理權衡。

-

射頻

+關注

關注

106文章

6026瀏覽量

173621 -

電源管理

+關注

關注

117文章

7926瀏覽量

148117 -

adc

+關注

關注

100文章

7530瀏覽量

556413 -

模數轉換器

+關注

關注

26文章

4022瀏覽量

130178 -

采樣系統

+關注

關注

0文章

5瀏覽量

6106

原文標題:模擬芯視界 | 射頻轉換器的電源噪聲抑制:實現無雜波雷達設計

文章出處:【微信號:tisemi,微信公眾號:德州儀器】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

采用TMS320F2812變頻電源的交流采樣系統設計方案

基于dsp防撞雷達信號采樣系統設計

一種基于低噪聲電源管理架構的射頻采樣系統設計方案

一種基于低噪聲電源管理架構的射頻采樣系統設計方案

評論