如今IC 封裝的設(shè)計周期越來越短,我們必須盡早發(fā)現(xiàn)并糾正布線問題,仿真愈發(fā)成為設(shè)計周期中不可或缺的一部分。Layout工程師希望采用一種快速而準確的方法,通過觀察附近信號引起的阻抗值變化和高耦合度來發(fā)現(xiàn)layout錯誤。但遺憾的是,Layout工程師通常沒有機會使用昂貴而復雜的信號完整性工具。此外,在項目期限已經(jīng)很緊張的情況下,他們幾乎沒有時間學習一種復雜的新工具。

好消息是,Allegro Package Designer Plus 工具內(nèi)引入了一個高速分析和檢查環(huán)境。Allegro Package Designer Plus SiP Layout Option 中新集成的設(shè)計同步阻抗和耦合工作流程由 Sigrity 求解器提供支持,能夠以快速簡單的方式分析Layout后的封裝,使工程師無需再在復雜的工具上花費時間和精力。

在新發(fā)布的Allegro SPB 17.4 版本中,Allegro Package Designer Plus with SiP Layout 增加了一個新菜單,即 Workflow Manager。本文將帶領(lǐng)大家了解一下運行阻抗和耦合工作流程的步驟。

步驟一:為封裝設(shè)計設(shè)置仿真環(huán)境

在開始仿真之前,請確保滿足以下幾點要求:

設(shè)計必須具備一個地平面

環(huán)境變量 sigrity_eda_dir 指向最新的 Sigrity 設(shè)置,可以通過 Setup ─ User Preferences ─ Paths ─ Signoise 來訪問該變量

步驟二:阻抗分析工作流程

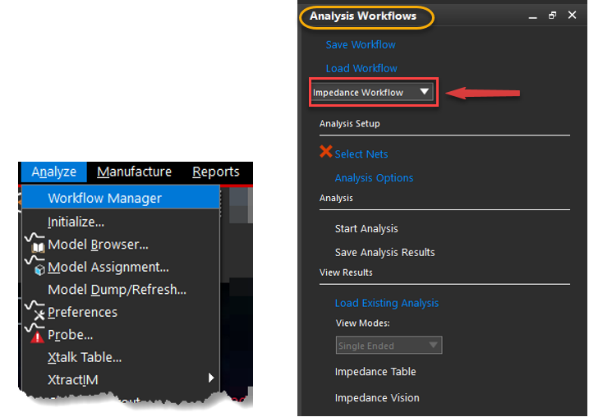

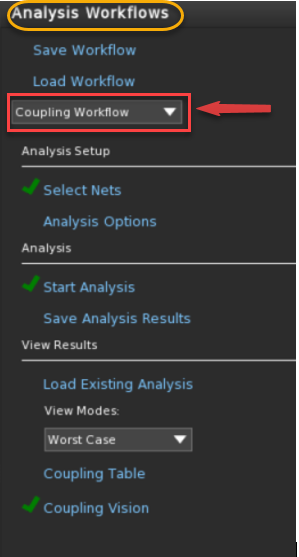

運行阻抗分析工作流程可以識別并解決設(shè)計中真正的阻抗問題。在菜單中選擇Analyze——Workflow Manager,打開 Analysis Workflows 界面:

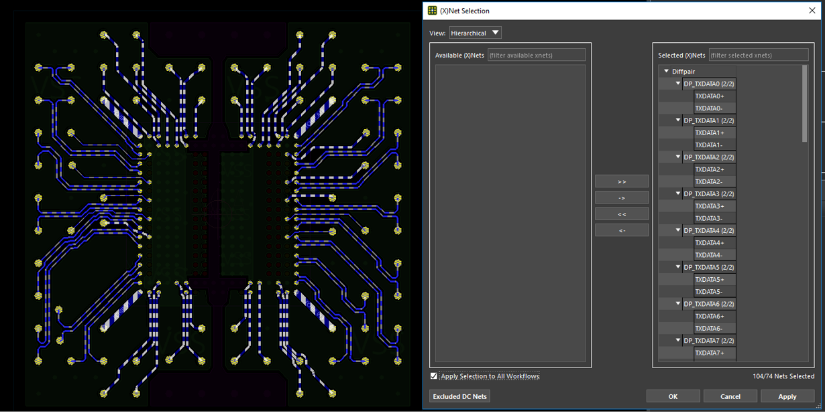

使用 Select Nets 選項來選擇設(shè)計中的關(guān)鍵網(wǎng)絡。這些網(wǎng)絡顯示在用戶界面的 Selected (X)Nets 部分。如果啟用 Apply Selection to All Workflows 復選框,所選擇的網(wǎng)絡也將應用于耦合工作流程。

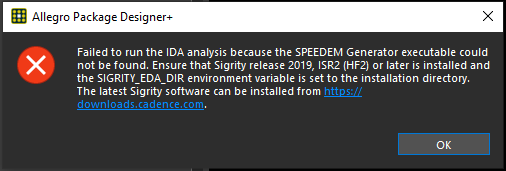

點擊 Start Analysis,開始仿真。如果看到下面的失敗信息,則表示沒有正確設(shè)置 sigrity_eda_dir 變量。請打開 User Preferences Editor,確認設(shè)置該變量并再次運行仿真。設(shè)置和運行仿真非常容易,可以很快完成。

如果沒有看到以上消息,則說明運行成功,結(jié)果已加載到工作流程之中。阻抗分析在仿真時忽略了設(shè)計中存在的引線鍵合。

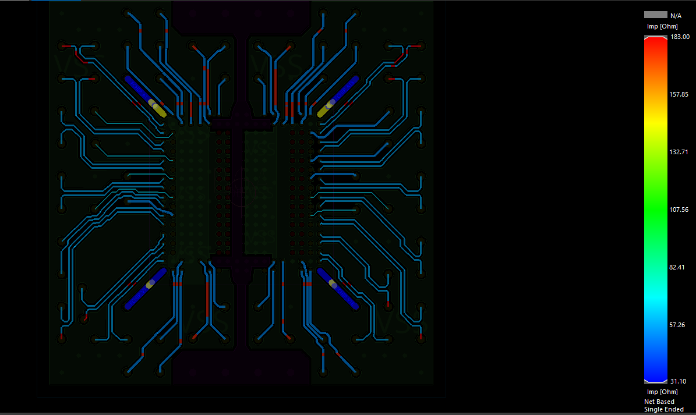

現(xiàn)在,選擇 Impedance Vision,在設(shè)計界面上疊加阻抗結(jié)果的色彩編碼視圖。色彩編碼范圍從紅色到藍色,再加上匯總表,可以很容易地找到哪些地方信號阻抗很高,需要快速進行設(shè)計修復。

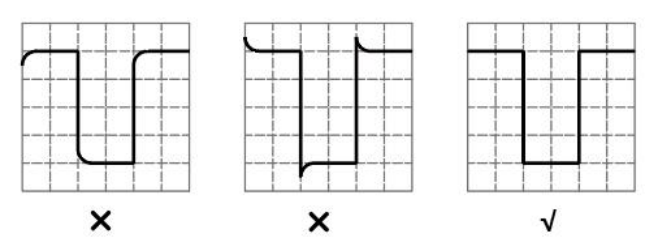

高阻抗可能是由各種原因造成的,如接地平面存在間隙、層發(fā)生變化或走線寬度發(fā)生變化;但是,有一點是肯定的——高阻抗需要快速進行設(shè)計修復。為了使阻抗降到最低,可以點擊表格中的數(shù)據(jù)點,找到該走線。然后修復問題,并重新運行仿真進行驗證。

保存分析結(jié)果,并在之后需要時重新加載。也可以使用 Save Workflow 選項,保存完整的工作流程選擇和設(shè)置,然后使用 Load workflow 選項導入工作流程,以便重新使用保存的工作流程。

步驟三:耦合分析工作流程

在最后設(shè)計確認時,運行“耦合分析”也可以發(fā)現(xiàn)潛在的耦合問題。為此,請在 Analysis Workflows 用戶界面的下拉菜單中選擇 Coupling Workflow。

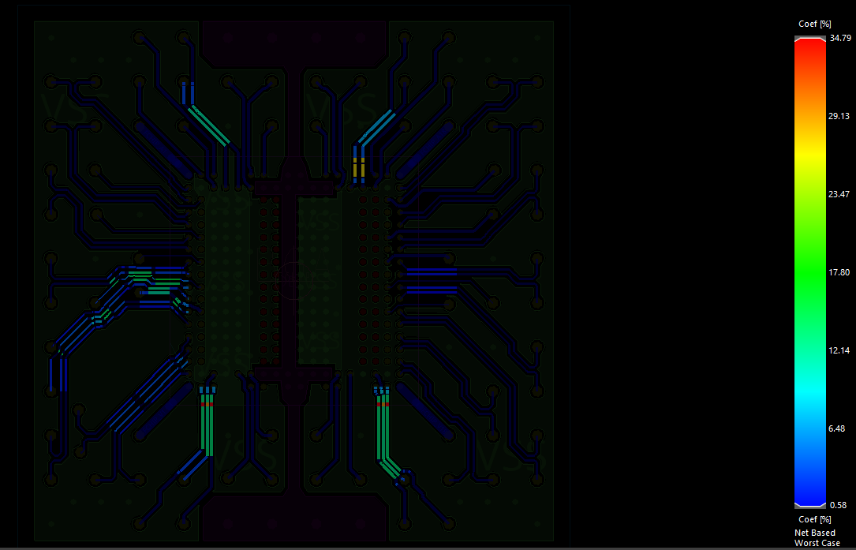

按照阻抗分析流程中提到的方法運行仿真。仿真完成后,選擇 Coupling Vision,在設(shè)計界面上分析結(jié)果。有耦合問題的走線會在畫面上突出顯示,并在表中列出受影響者 (victim) 和影響源 (aggressor) 網(wǎng)絡。調(diào)整走線之間的間距,以消除或減少耦合問題。然后再次運行分析,檢查糾正措施是否有效。

總結(jié)

封裝設(shè)計中的設(shè)計同步分析可以幫助Layout工程師快速找到并解決關(guān)鍵的信號完整性問題,同時無需占用額外時間或資源來學習如何使用復雜的信號完整性工具。

-

IC

+關(guān)注

關(guān)注

36文章

6411瀏覽量

185699 -

封裝

+關(guān)注

關(guān)注

128文章

9254瀏覽量

148671 -

仿真

+關(guān)注

關(guān)注

54文章

4486瀏覽量

138309

發(fā)布評論請先 登錄

技術(shù)資訊 I 如何識別同步開關(guān)噪聲

使用MATLAB和Simulink進行信號完整性分析

PK6350無源探頭在高速數(shù)字總線信號完整性測試中的應用案例

技術(shù)資訊 I 一文速通 MCM 封裝

技術(shù)資訊 I 信號完整性與阻抗匹配的關(guān)系

深圳 9月12-13日《信號完整性--系統(tǒng)設(shè)計及案例分析》公開課,即將開課!

普源DHO5000系列數(shù)字示波器信號完整性分析

上海 6月20-21日《信號完整性--系統(tǒng)設(shè)計及案例分析》公開課,即將開課!

受控阻抗布線技術(shù)確保信號完整性

信號完整性測試基礎(chǔ)知識

普源示波器在信號完整性分析中的應用研究

技術(shù)資訊 I 如何在IC封裝中使用”設(shè)計同步分析”流程解決信號完整性問題

技術(shù)資訊 I 如何在IC封裝中使用”設(shè)計同步分析”流程解決信號完整性問題

評論