本文重點

信號完整性測試需要從測試電路板和原型獲取實驗數據并加以分析。

在理想的工作流程中,還會仿真信號完整性指標,并將其與實際測量值進行比較。

信號完整性測試只能檢查特定的結構,通常需要在測試前設計和仿真測試電路板。

為確保可靠性并符合行業標準,高速 PCB 和高頻 PCB 必須經過一系列測試。其中許多測試都是由層壓板供應商或 PCB 制造商執行,這有助于確保符合安全和環境法規以及基本電氣要求。另外還需要考慮 EMC 測試,對于準備大批量生產并投放到市場的設計而言更是如此。

在保障性能方面,設計團隊負責的一個領域是信號完整性。當設計人員制作具有高速通道的原型時,可能需要執行基本的信號完整性測試程序,以確保產品能夠按預期運行。成功完成測試需要使用正確的儀器,還要將數據與仿真結果進行比較,以全面評估產品性能。

信號完整性測試中需要檢查哪些內容

在信號完整性測試中,我們檢查的一些基本事項對于系統的性能而言至關重要,并且涉及到直接檢查電路板中的信號行為:

傳輸線和電路阻抗,這通常必須在具有已知 S 參數的附加裝置的測試電路板上完成。

信道損耗、抖動和失真,可以使用原型或測試電路板中的測試夾具直接進行信號測量。

來自高速通道的 EMI,這可能表明電路中存在其他問題,或者高速通道中的阻抗匹配存在問題。

信道之間的串擾,只有在具有多條并行線路的測試電路板上才能有效測量。

信號完整性測試并不是始終依賴于直接測量信號。在某些情況下,尤其是在組裝的原型中,我們無法直接執行測量并獲得準確的信號測量值。相反,我們可能必須使用原型電路板來測量其他方面,或者設計一個包含可用于特定測量的夾具的測試電路板。

重要測試設備

以下展示的是市場上一些最常見的信號完整性測試設備。

矢量網絡分析儀

?它用于網絡參數測量,尤其適用于極高頻率的 S 參數。在信號完整性測試中,它通常使用 DUT 或擬議信道設計進行 2 端口或 N 端口 S 參數測量,目的是提取信道中傳輸線部分/DUT 的 S 參數。然后可以在簽核之前將傳輸線或 DUT 的 S 參數與仿真結果或信號標準進行比較。

矢量網絡分析儀

這是將信號測量值重建到時間域的主要工具,允許直接測量振鈴、碼間干擾(ISI)、抖動和差分偏差等。一些示波器可以配置為高速信道的誤碼率測試儀。

使用示波器進行眼圖中的誤碼率測試

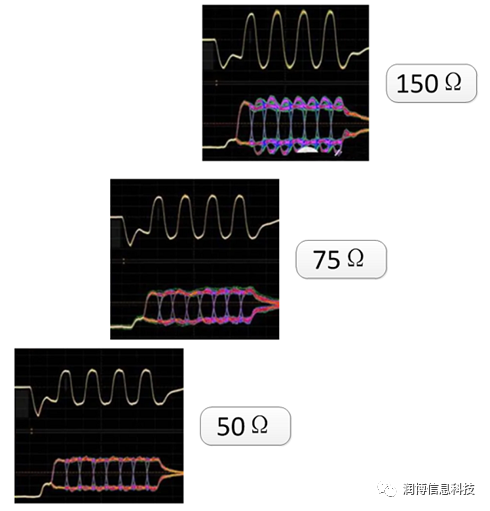

時域反射計

該工具用于檢測光纖電纜中的斷裂、裂縫或低質量保險絲,也可用于測量傳輸線或波導的阻抗和衰減。在這種測量中,會將脈沖發送到測試線路的輸入端,并且可以測量沿線路產生的任何反射,之后在時域中的圖表中顯示。通過將反射脈沖中的峰值信號功率與輸入進行比較,還可以測量輸入和反射之間的衰減。

時域反射計

近場探針

這個簡單的設備用于測量電路或一組器件發出的近場 EMI。該設備非常適合追蹤可能因信號完整性或電源完整性問題而產生的 EMI 問題。此類示例包括布線期間接地不良(例如,在換層的時候),這會產生輻射 EMI 或激發高頻腔體模式的電源總線噪聲。這些探針通常應具有較高的衰減比(10:1),這樣就可以用示波器或頻譜分析儀正確解析輻射信號。

用于測量輻射 EMI 的近場探針

在信號完整性測試之前運行仿真

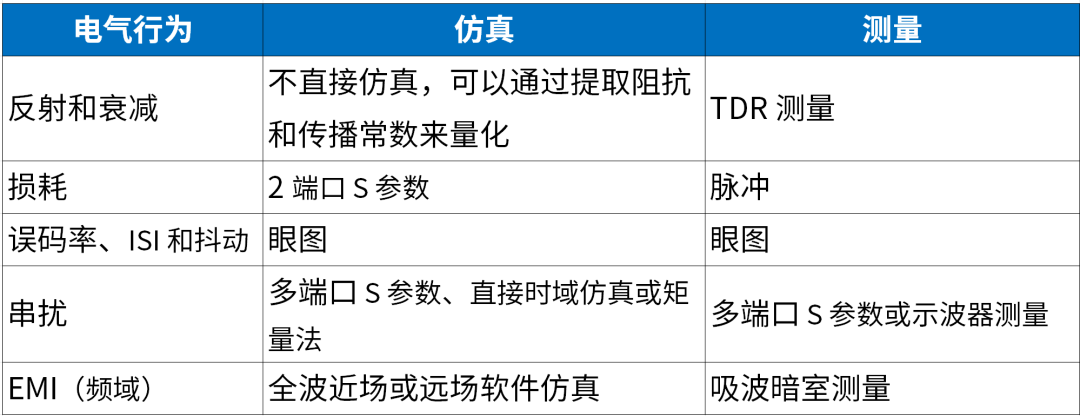

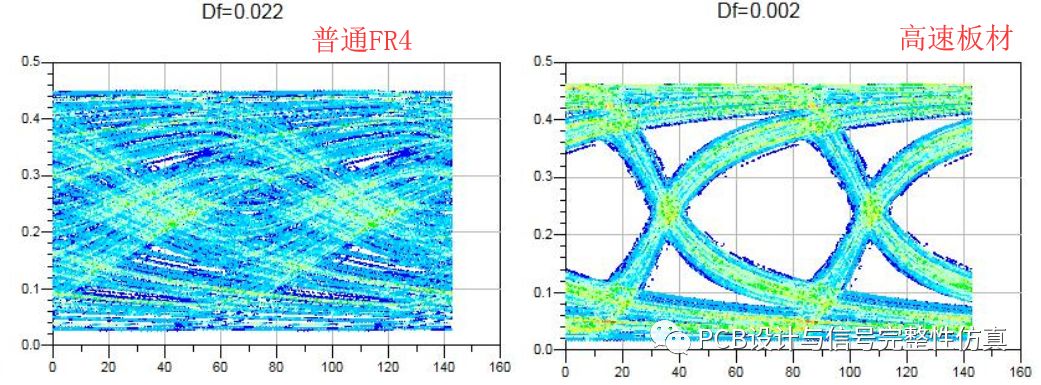

在從測試電路板或原型收集測量結果之前,應該使用仿真來提取重要的電氣參數和性能數據。這有助于在收集測量結果之前為設計生成基準,并在制作原型之前發現簡單的設計問題。以下總結了設計中需要仿真的一些要點以及相應的測量。

關于要仿真的點,具體列表取決于特定的設計和性能標準。無論需要仿真哪些內容,我們都可以使用正確的設計工具來對預期的物理布局和測試電路板進行仿真。這些仿真需要使用集成的 2D 和 3D 電磁場求解器,因為它們是在 PCB layout 中執行的,而不是在 SPICE 仿真的電路原理圖中執行的。當我們可以將物理布局與 3D 場求解器快速連接時,就得到了一個有助于加快設計、測試和仿真的解決方案。

新一代 Sigrity X 可以與 Clarity 3D Solver 配合工作,并與 Cadence Allegro X PCB Designer 和 Allegro X Advanced Package Designer 工具緊密集成。這一全新特性可以幫助 PCB 和 IC 封裝設計師將端到端、multi-fabric 和多電路板系統(從發射端到接收端或從電源到耗電端)相結合,確保 SI/PI 成功簽核。

Sigrity X 也將提供全新的用戶體驗,支持不同分析工作流程間的無縫過渡,進一步縮短復雜系統級 SI/PI 分析的設置時間。

-

測試

+關注

關注

9文章

6297瀏覽量

131525 -

分析儀

+關注

關注

0文章

1768瀏覽量

54854 -

信號完整性

+關注

關注

68文章

1487瀏覽量

98176

發布評論請先 登錄

信號完整性為什么寫電源完整性?

電源完整性基礎知識

技術資訊 | 信號完整性測試基礎知識

技術資訊 | 信號完整性測試基礎知識

評論