內(nèi)容提要

● 基于 DSP 的靈活速率 SerDes IP 已針對(duì) PPA 進(jìn)行優(yōu)化,適用于下一代云網(wǎng)絡(luò)、AI/ML 和 5G 無線應(yīng)用

● 新架構(gòu)提供卓越的 ELR 性能,能實(shí)現(xiàn)有損信道和反射信道的系統(tǒng)穩(wěn)定性

● 該 IP 支持 ELR、LR、MR 和 VSR 應(yīng)用,并在不同的信道上提供靈活的功耗節(jié)省能力

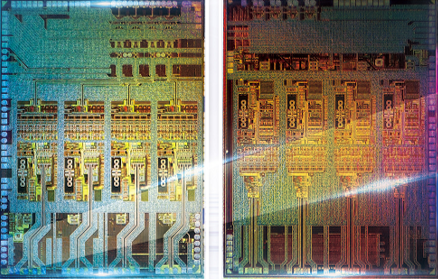

楷登電子(美國 Cadence 公司,NASDAQ:CDNS)今日發(fā)布基于臺(tái)積電 N4P 工藝的 112G 超長距離(112G-ELR)SerDes IP,該 IP 適用于超大規(guī)模 ASIC、人工智能/機(jī)器學(xué)習(xí)(AI/ML)加速器、交換架構(gòu)系統(tǒng)級(jí)芯片(SoC)和 5G 無線基礎(chǔ)設(shè)施。超長距離 SerDes PHY 支持 43db 的插入損耗(IL),比特誤碼率為 10e-7,從而提供超出長距離標(biāo)準(zhǔn)規(guī)范的額外性能裕度,并可為開放箱式平臺(tái)以及較長直連銅(DAC)電纜的有損信道和反射信道提供卓越的系統(tǒng)穩(wěn)定性。

基于臺(tái)積電 N4P 工藝(臺(tái)積電 5nm 技術(shù)平臺(tái)的性能增強(qiáng)版)的 Cadence 112G-ELR SerDes PHY IP 采用業(yè)界領(lǐng)先的基于數(shù)字信號(hào)處理器(DSP)的 SerDes 架構(gòu),配備最大似然序列檢測(MLSD)和反射消除技術(shù)。

該 SerDes PHY IP 符合 IEEE 和 OIF Long-Reach(LR)標(biāo)準(zhǔn),同時(shí)為 ELR 應(yīng)用提供了額外的性能裕度。優(yōu)化的功耗、性能和面積非常適合不同的用戶場景,包括高端口密度應(yīng)用。

除了 ELR 和 LR 信道外,該 IP 還支持中距離(MR)和極短距離(VSR)應(yīng)用,在不同的信道上提供靈活的功耗節(jié)省能力。支持的數(shù)據(jù)速率從 1G 到 112G 不等,采用 NRZ 和 PAM4 信號(hào),可通過背板、直連電纜(DAC)、芯片到芯片和芯片到模塊信道實(shí)現(xiàn)可靠的高速數(shù)據(jù)傳輸。

“基于臺(tái)積電 N4P 工藝的 Cadence 112G-ELR IP 顯著提升了芯片性能,將使我們的共同客戶受益,依托不斷進(jìn)步的 Cadence IP 解決方案和臺(tái)積電先進(jìn)工藝技術(shù),幫助他們應(yīng)對(duì)設(shè)計(jì)挑戰(zhàn),”臺(tái)積電設(shè)計(jì)基礎(chǔ)設(shè)施管理部負(fù)責(zé)人 Dan Kochpatcharin說道,“我們與 Cadence 的最新合作促進(jìn)了超大規(guī)模、人工智能/機(jī)器學(xué)習(xí)、5G 基礎(chǔ)設(shè)施和其他應(yīng)用的新技術(shù)開發(fā)。”

“我們基于臺(tái)積電 N4P 解決方案的下一代 112G-ELR SerDes 為客戶應(yīng)用提供卓越的性能裕度和系統(tǒng)穩(wěn)定性,”Cadence 公司全球副總裁兼 IP 事業(yè)部總經(jīng)理 Sanjive Agarwala說道,“我們與領(lǐng)先的超大規(guī)模和數(shù)據(jù)中心客戶緊密合作,十分了解嚴(yán)苛的行業(yè)要求,因此開發(fā)出增強(qiáng)架構(gòu),可改善 112G SerDes 的所有關(guān)鍵參數(shù)。我們基于臺(tái)積電 N4P 工藝的 112G-ELR SerDes 解決方案進(jìn)一步鞏固了我們?cè)跒槌笠?guī)模數(shù)據(jù)中心提供高性能連接 IP 方面的領(lǐng)導(dǎo)地位。此外,客戶還可以獲得臺(tái)積電 N4P 工藝帶來的相關(guān)技術(shù)優(yōu)勢(shì)。”

Cadence 目前在臺(tái)積電 N4P 測試芯片上包含了 112G-ELR,展現(xiàn)出強(qiáng)大的性能。基于臺(tái)積電 N4P 工藝的 Cadence 112G-ELR SerDes 解決方案現(xiàn)已面向客戶推出,有不同版本可供選擇,為公司的 PAM4 SerDes 建立了龐大的客戶群。基于臺(tái)積電 N4P 工藝的 112G-ELR SerDes PHY IP 是 Cadence IP 產(chǎn)品組合的一部分,支持 Cadence 智能系統(tǒng)設(shè)計(jì)(Intelligent System Design)戰(zhàn)略,該戰(zhàn)略可實(shí)現(xiàn)卓越的先進(jìn)節(jié)點(diǎn) SoC 設(shè)計(jì)。

審核編輯:湯梓紅

-

臺(tái)積電

+關(guān)注

關(guān)注

44文章

5803瀏覽量

176319 -

工藝

+關(guān)注

關(guān)注

4文章

713瀏覽量

30313 -

Cadence

+關(guān)注

關(guān)注

68文章

1011瀏覽量

146925 -

芯片設(shè)計(jì)

+關(guān)注

關(guān)注

15文章

1155瀏覽量

56677

原文標(biāo)題:Cadence 發(fā)布基于臺(tái)積電 N4P 工藝的下一代 112G 擴(kuò)展長距離 SerDes IP,加快超大規(guī)模系統(tǒng)級(jí)芯片設(shè)計(jì)

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

1.4nm制程工藝!臺(tái)積電公布量產(chǎn)時(shí)間表

Cadence公司成功流片第三代UCIe IP解決方案

全球首款4×112G 算力中心模擬CDR電芯片由上海米硅突破!

基于TE Connectivity QSFP-DD 112G連接器數(shù)據(jù)手冊(cè)的技術(shù)解析

TE Connectivity QSFP 112G SMT連接器與屏蔽罩技術(shù)解析

新思科技LPDDR6 IP已在臺(tái)積公司N2P工藝成功流片

Cadence AI芯片與3D-IC設(shè)計(jì)流程支持臺(tái)積公司N2和A16工藝技術(shù)

貿(mào)澤即日起開售適用于數(shù)據(jù)中心和網(wǎng)絡(luò)應(yīng)用的 全新TE Connectivity QSFP 112G SMT連接器

力旺NeoFuse于臺(tái)積電N3P制程完成可靠度驗(yàn)證

晟聯(lián)科受邀出席臺(tái)積電技術(shù)研討會(huì),高速接口IP組合及解決方案助推海量數(shù)據(jù)暢行

Cadence發(fā)布基于臺(tái)積電N4P工藝的112G超長距離SerDes IP

Cadence發(fā)布基于臺(tái)積電N4P工藝的112G超長距離SerDes IP

評(píng)論