華邦電子一直以來提供閃存和DRAM的良品裸晶圓(KGD)產品,KGD可以與SoC進行合封,以實現更優的成本和更小的尺寸。據華邦電子次世代內存產品營銷企劃經理曾一峻介紹,在KGD1.0中裸片最厚處大約為100-150微米,裸片至裸片(dieto die)的I/O 路徑為1000 微米,目前這種性能的KGD信號完整性/電源完整性(SI/PI)是主流也夠用。在對LPDDR4的電源效率進行估算時顯示,其小于35pJ/Byte,帶寬方面 X32 LPDDR4x每I/O為17GB/s。

如今華邦電子KGD進入2.0時代。KGD2.0是以3D堆疊的KGD,通過TSV的深寬比能力(也就是aspect Ratio),可以做到1:10,實現厚度更薄。華邦目前可以實現50微米的深度,相當于需要將芯片打磨至2mil。未來通過HybridBonding工藝可以實現1微米的距離。同時,在KGD2.0工藝下,信號完整性/電源完整性(SI/PI)表現會更好,并且功耗更低,可以低于LPDDR4的四分之一,為8pJ/Byte,而帶寬可以實現16-256GB/s。KGD2.0性能更好、成本更優、更容易按時交付。

CUBEDRAM的3D堆疊技術特點

今年2月,華邦宣布加入了UCIe聯盟,華邦可協助系統單芯片客戶(SoC)設計與 2.5D / 3D 后段工藝(BEOL, back-end-of-life)封裝連結。其推出CUBE解決方案,提供半定制化的緊湊超高帶寬DRAM(Customized/Compact Ultra Bandwidth Elements)。

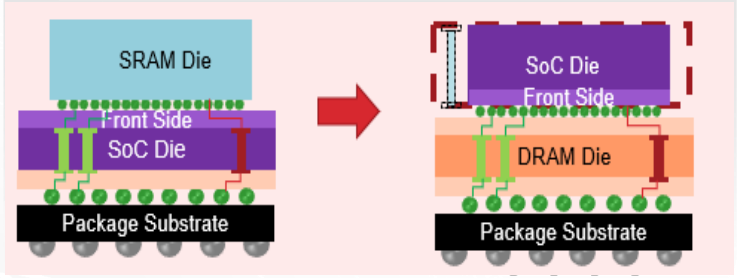

從CUBE的結構來看,是將SoC裸片置上,DRAM裸片置下,省去SoC的TSV工藝。下圖右邊虛線部分所示:

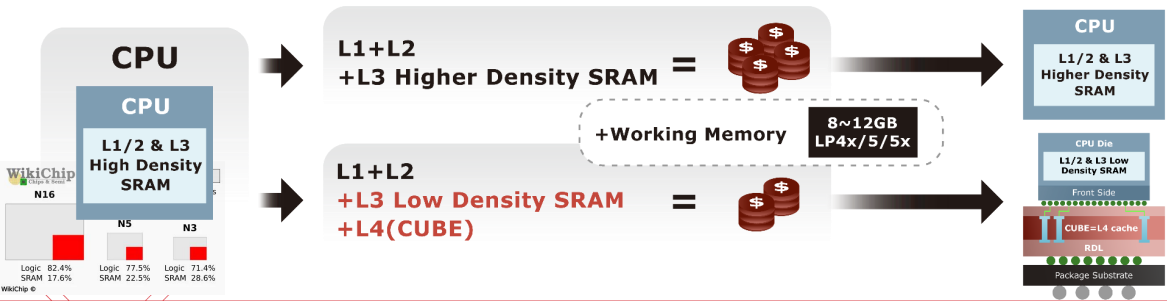

曾一峻分析,傳統上CPU為了增加高速緩存能效,直接增加SRAM的帶寬和容量,這樣的方式會增加非常高的成本。為了節省成本,廠商會使用相對成熟制程的SRAM,例如5nm的 SoC裸片上堆疊7nm的SRAM 裸片。但這種架構下,底部的CPU就需要埋入相當多的TSV,同時增加CPU裸片面積,成本依然會相對較高,如上圖左邊的示意。

而采用華邦的解決方案(上圖右邊所示),SoC裸片尺寸縮小,成本相應降低,同時通過華邦的DRAM TSV工藝,可以將SoC的信號引至外部,使它們成為同一個封裝芯片。DRAM做TSV的好處是其裸片將會變得很薄,尺寸變得更小。

SoC裸片置上也可以帶來更好的散熱效果,滿足現在AI高算力的需求。總之進行3D堆疊以及CUBEDRAM裸片堆疊可以帶來高帶寬、低功耗和優秀的散熱表現。

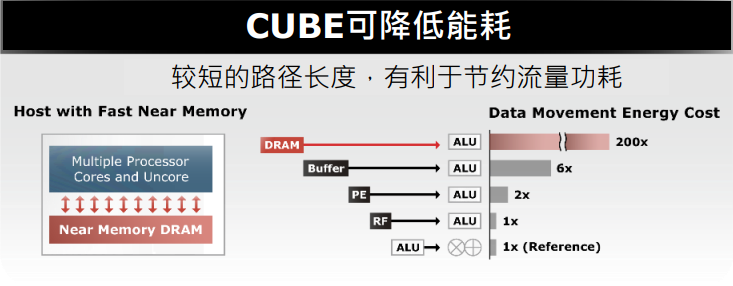

華邦的CUBE還可以降低功耗。曾一峻解析,當SoC裸片和DRAM裸片堆疊的時候,相比于傳統的引線鍵合(WireBonding),微鍵合(MicroBonding)可以將1000微米的線長縮短至40微米,僅有傳統長度的2.5%。在未來的混合鍵合(HybridBonding)封裝工藝下,線長甚至可以縮短至1微米。從芯片內部來看,信號所經過的傳輸距離更短,因此功耗可相應地降低。此外,采用混合鍵合工藝,兩顆堆疊的芯片可以被看作同一顆芯片,因此內部傳輸信號和SIP表現會更優秀。

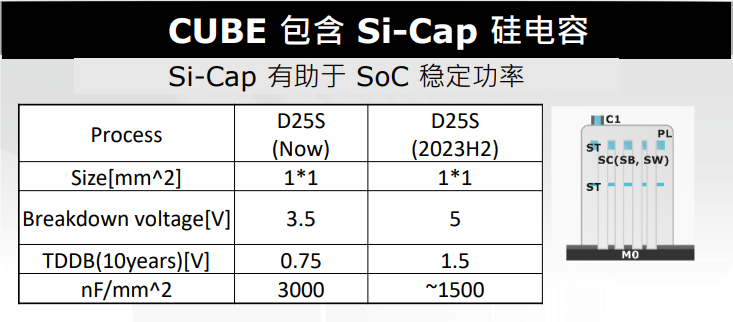

曾一峻進一步指出,DRAM裸片中都會包含電容,華邦的CUBE芯片提供硅電容(Si-Cap)。硅電容的好處在于可以降低電源波動帶來的影響。例如,如果先進制程的SoC的核心電壓只有0.75V-1V左右,并且運行過程中電源產生一些波動,除了會影響到功耗,還會影響信號的穩定性,而硅電容容量提高的情況下,SoC借助硅電容就可以獲得穩定的電壓。

下圖是華邦當前硅電容規格和制程的進展,今年下半年會帶來更優規格的硅電容。

通過上面表格的參數,可以看到盡管電容縮小到了一半,但是運行經時擊穿電壓(TDDB)被提高一倍至1.5V。1.5V目前是大部分先進制程芯片的核心電壓。此外擊穿電壓也是目前先進制程所需的5V,因此1500nF/(mm2)其實是可以符合目前先進制程芯片的電容需求。

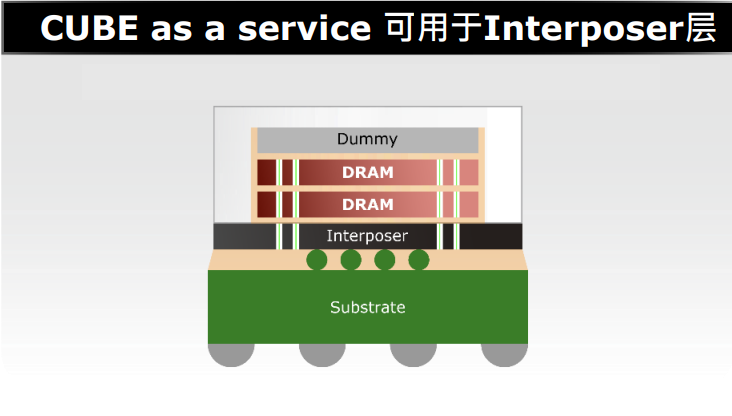

華邦還提供中介層中介層(Interposer),目前正在進行內部技術演進的是華邦的DRAM堆疊與中介層(Interposer)的架構,以這樣的架構開發DRAM的目的是可以驗證華邦的TSV。

至此,華邦電子成立了3DCaaS平臺,可以向客戶提供包括DRAM、中介層、硅電容在內的整體解決方案。這也是華邦加入UCIe后帶來的貢獻之一。“無論是TSV、還是WOW(WaferonWafer),華邦都已經達成了與業內相關企業的合作,構建了合作伙伴生態。在COW(ChiponWafer)方面,華邦將提供TSV的DRAM裸片,并且會幫助SoC客戶通過適合的合作伙伴進行后續封測。COW還包含了2.5D、Fan-Out以及3D堆疊工藝,其中2.5D和3D堆疊所用到的硅中介層華邦都可以提供,并且華邦的硅電容還能使芯片的SI/PI減小,使能耗表現更好。甚至華邦的Si-Bridge還能讓硅中介層的裸片尺寸更小。”曾一峻說道。

可作為L4級緩存用于邊緣計算

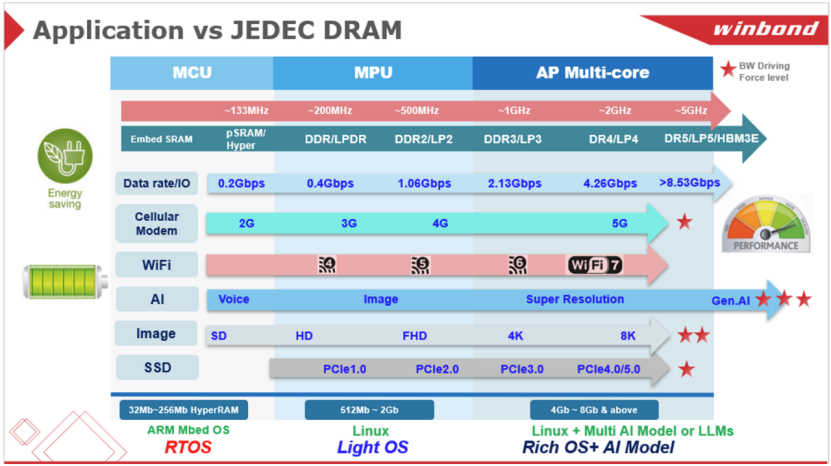

華邦的CUBE解決方案主要面向低功耗、高帶寬,以及中低容量的內存需求,適合于邊緣計算和生成式AI等應用。

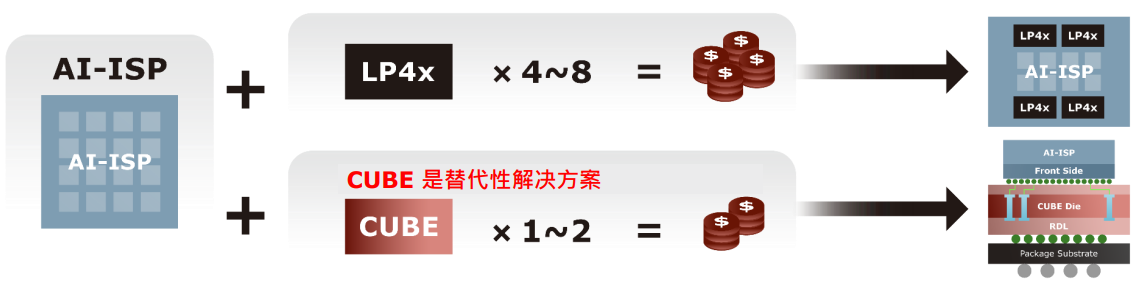

例如在AI-ISP架構中,如下圖所示,灰色部分屬于神經網絡處理器(NPU),如果AI-ISP要實現大算力,需要很大的帶寬,或者是SPRAM。但是在AI-ISP上使用SPRAM的成本非常高,不太可行。如果使用LPDDR4就需要4-8顆,無論是合封還是外置,成本同樣相當高昂。此外,還有可能會用到傳輸速度為4266Mhz的高速LPDDR4,而這樣的產品需要依賴7nm或12nm的先進制程工藝生產。

華邦的CUBE解決方案可以允許客戶使用成熟制程(例如28、22nm)的SoC,獲得類似的高速帶寬。華邦的CUBE解決方案可以通過多個I/O(256或者512個)結合28nm SoC提供的500MHz的運行頻率,以此實現更高帶寬,帶寬最高可增至256GB/s。不僅如此,華邦在未來可能會和客戶探討64GB/s帶寬的合作,I/O數可以減少,裸片的尺寸也會進一步縮小。

隨著CPU高速運算需求對制程的要求越來越高,我們可以看到16nm、7nm、5nm到3nm的CPU,SRAM占比(如下圖中紅色部分所示)并不會同比例縮小,因此當需要實現AI運算或者進行高速運算的情況下,就需要把L3的緩存SRAM容量加大,即便可以使用堆疊的方式達到幾百MB,也會導致高昂的成本。

華邦的方案是把L3緩存縮小,轉而使用L4緩存的CUBE解決方案。當然,L4緩存之所以被稱作L4,首先是因為它的延遲(Latency)會比L3的稍長。曾一峻表示,為了克服這個問題,可以采用多BANK的方式(multibankper channel),來獲得更好的存取效率。第二個方式是將重寫(rewrite) IO分開,這是一個比較類SRAM的方式,縮短運行時間。換句話說,是以某些比較特殊的架構進行產品修正,我們會針對客戶的一些特殊需求和應用場景進行定制化調配,縮短L4緩存的延遲。

同時,AI模型在某些情況下還是需要外置一定容量的內存,例如在某些邊緣計算的場景下會需要8-12GB的LPDDR4或者是LPDDR5,因此也可以外掛高容量的工作內存(Working Memory)。綜上所述,CUBE可以允許使用成熟制程,以降低SoC成本、減小芯片功耗以及獲得高帶寬這三大主要訴求。

據透露,目前華邦就CUBE解決方案已經和幾家客戶展開了項目洽談,具體的合作內容也還處在進行時,包括了邊緣計算和生成式AI這兩個應用方向。依照目前的進展,或許明年會有一些官方的合作新聞發布。

曾一峻認為,CUBE解決方案在邊緣計算服務器領域將有很大的機會。相對于大模型的訓練,在邊緣服務器上可以把模型縮小,但是它一樣需要具備很高帶寬的內存(通過堆疊DRAM),但不需要很高的容量。無論是監控(surveillance)或5G的邊緣計算服務器,或是中小企業內部部署的數據中心服務器(on-premise data server center),都有可能會運用到華邦的CUBE解決方案。

華邦電子DRAM路線

華邦目前擁有兩座12寸晶圓廠,一個是位于臺中的Fab6工廠;另外,從去年的下半年開始,華邦在高雄新建的第二座廠已經正式量產,目前的投片量達到了1萬片/月左右。后續高雄廠規劃的產能會逐漸爬坡到1.4萬片至2萬片/月。

高雄廠主要生產先進制程的DRAM,臺中廠的中小容量DRAM制程會維持在65nm、46nm以及38nm、25nm,以成熟制程為主。目前高雄廠已在量產的25nm產品包括2GB和4GB兩種產品,已經開始大批量交付。20nm產品在今年中也會進入量產階段,下一步會向19nm制程演進。

華邦DDR3主要有1Gb、2Gb、4Gb以及8Gb四種容量,同時需要強調的是,華邦會持續進行DDR3的生產和支持。華邦的DDR4規劃是在今年中,20nm的制程就緒以后在高雄廠生產。量產時間規劃在2024年初。后續DDR3產品在2025年會演進至16nm。

在業界很多大廠停產DDR3之時,華邦表示未來會持續生產DDR3,據OMDIA的報告DDR3產品將持續存在到2027、2028年。特別是在車用、工業用的場景,DDR3是更加成熟且尺寸、成本更有優勢的一代產品。

存儲市場預期

我們看到,存儲行業經過從去年下半年開始到今年上半后的調整,主要是大廠削減產能、減少資本支出,延遲新廠建設計劃等,以期讓存儲行情企穩。對此,華邦電子大陸區產品營銷處處長朱迪表示,雖然今年上半年大環境還是處于調庫存的狀態,但是需求已經逐漸回暖。在消費類的應用上,客戶的下單力道慢慢在恢復。同時也有一些客戶也在觀望庫存調整以及價格下跌是否已經到達階段性低谷,開始來跟各家內存廠商洽談準備下一些長期的訂單。

因此,朱迪認為,今年上半年應該還是底部階段,但是市況會逐漸改善。尤其是國內出臺了一些相應的刺激經濟的措施,包括數字經濟發展、AI產業的推動等,因此對于下半年的存儲市場比較樂觀。

朱迪表示,另一個維度看,汽車和工業應用是華邦耕耘較好的領域,占到去年營收的29%。這也是為什么大環境雖然如此不好,去年華邦的營收表現還算不錯的原因。這一類客戶更看重于品質的穩定性和交付的保證。華邦作為一個擁有自有工廠的IDM,同時又更聚焦于這些中小容量DDR3及以下的產品,贏得客戶的信任和認可。另外,在消費類、網通類產品,它的DDR3以及往DDR4演進的速度會比預想的快一些。主要原因是主芯片廠商要追求更高的帶寬,以及市場價格的走向影響。

“利基型存儲市場的特點是整個市場的盤子會比較小,大概占整個存儲的10%不到。所以它的供需相對而言是比較平衡和穩定的。因此這一市場受到波動的影響相對較小。謹慎樂觀看待今年下半年存儲行業的復蘇。”朱迪說道。

-

DRAM

+關注

關注

41文章

2394瀏覽量

189149 -

華邦電子

+關注

關注

0文章

83瀏覽量

17188 -

3D封裝

+關注

關注

9文章

149瀏覽量

28307

發布評論請先 登錄

端側AI“堆疊DRAM”技術,這些國內廠商發力!

華為在MWC 2026正式發布核心網AN L4目標解決方案CORESpirit

Kioxia研發核心技術,助力高密度低功耗3D DRAM的實際應用

華邦電子推出先進 16nm 制程 8Gb DDR4 DRAM 專為工業與嵌入式應用而生

NVIDIA與Uber合作推進全球L4級自動駕駛移動出行網絡

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

iTOF技術,多樣化的3D視覺應用

行深智能推出基于地平線征程6M的L4級自動駕駛解決方案

智啟存儲未來,華邦電子攜三大產品矩陣亮相2025慕尼黑上海電子展

用3D堆疊技術打造DRAM成為L4級緩存,華邦電子CUBE解決方案助力邊緣AI

用3D堆疊技術打造DRAM成為L4級緩存,華邦電子CUBE解決方案助力邊緣AI

評論