摩爾定律極限將至

隨著摩爾定律的飛速發展,芯片制程早已大步邁入了 10nm 以下,一路發展至 7nm、5nm,并觸達了現階段業界普遍認為的物理極限——3nm。在進入 10nm 的大關后,工藝迭代的速度已經放緩,先進工藝的高昂成本問題也令制造商和終端消費者感到頭疼。

除了面臨先進工藝的成本挑戰,在摩爾定律逼近極限的“后摩爾時代”,半導體行業也無法再繼續通過微縮晶體管來提升芯片性能,行業亟需新的技術路線來滿足對芯片性能日益增長的需求,而這也正是 Chiplet 和先進封裝的“用武”之處。

接下來,我們將通過闡述定義來進一步揭開 Chiplet 和先進封裝的奧秘,以內存為例,為您解讀后摩爾時代的芯片發展趨勢。

Chiplet、UCIe 與異構集成

Chiplet 一般指預制好的、具有特定功能的、可用來組合集成的晶片,也叫芯粒,其技術重點在于將不同的芯片連接在一起并進行封裝。在這個過程中,芯片之間的連接由于異構性、互操作性以及數據完整度等問題面臨著諸多挑戰。

因此,2022 年 3 月 ,英特爾、AMD、Arm、高通、三星、臺積電等科技巨頭聯合成立了 UCIe 產業聯盟,共同推出了開放的行業互聯標準,使芯片制造商能夠輕松地將不同類型的芯片集成到同一芯片系統中。

作為知名的內存供應商,華邦電子也在前不久加入了 UCIe 產業聯盟,與聯盟伙伴共同助力高性能 Chiplet 接口標準的推廣與普及。

如今大家爭相探討的異構集成,全稱為異構異質集成,包含了異構與異質雙重含義。其中,制造商將如 3nm、5nm、7nm 甚至 28nm 和 45nm 等不同工藝制程、不同功能、不同制造商的 Chiplet 集成到一起,被稱作異構集成。而為了設計出小尺寸、低成本、設計靈活、系統性能出色的芯片產品,制造商還會將諸如硅、氮化鎵、碳化硅、磷化銦等不同材質的 Chiplet 集成在一起,這被稱作異質集成。

UCIe 標準的建立為異構芯片提供了高帶寬、低延遲、高電源效率和高性價比的封裝內連接,從而滿足整個計算系統的需求。

Chiplet 與先進封裝

現階段,業內對先進封裝的共識是 2.5D/3D 以及 WLCSP 晶圓級封裝,它們可在單位體積內集成更多的功能單元,以內存為例,先進封裝可大幅增加內存容量。同時,這些功能單元的互連更短、密度更高,進一步提升合封后的芯片性能。

Chiplet 與先進封裝是兩個不同的概念,但在某種程度上它們卻緊密相連——目前,行業內大多數的 Chiplet 是通過先進封裝技術將不同工藝制造的芯片進行集成的。然而在采用 2.5D/3D 這樣的垂直堆疊方式集成 Chiplet 芯片時,將面臨幾大關鍵挑戰:

封裝技術

隨著業界對小型化的需求愈演愈烈,芯片必須保證在更小的封裝空間內對更小尺寸的 Chiplet 芯片進行封裝,因此對封裝技術的要求極高;

連接設計

芯片堆疊的順序、走線方式都會影響合封芯片的性能,因此需要最佳的設計方式來降低整體風險;

熱管理

將芯片堆疊在一起后,散熱問題更為嚴峻,高溫會影響芯片的性能與壽命,因此需要采取更尖端的散熱技術來避免高溫導致的性能下降甚至是封裝失效;

另一方面,合封后的系統級芯片性能與集成在其中的 Chiplet 芯片性能息息相關。因此必須采用具備如下特質的裸片才能保證最終的芯片性能。

高度可靠

盡管在單個 Chiplet 芯片良率高達 98% 的情況下,合封后的產品良率也會大幅下降,此外還可能會與其他芯片相互干擾,但提升裸片(die)的可靠性仍舊可在某種程度上提升合封芯片的可靠性;

散熱合理

合封后,每個裸片與外界進行熱傳遞的面積急劇縮小,發熱量會進一步提高,因此必須盡可能降低裸片本身的散熱,才能將合封芯片的發熱控制在合理范圍內;

高溫穩定

合封芯片的發熱遠高于單一裸片的發熱量,為此,裸片需要具備較好的高溫下穩定性,才能保證芯片性能在溫度升高的環境中不受損;

更低功耗

系統級芯片的功耗受 Chiplet 芯片的功耗影響極大,為滿足用得低功耗需求,需要進一步降低裸片的自身功耗。

華邦的 KGD 和先進封裝

KGD 產品

作為業界知名的 KGD 供應商,華邦早在2008 年就已開始向客戶提供諸多優質 KGD 產品,包括DDR、LPDDR、HYPERRAM、NOR Flash等,并可根據客戶的不同需求靈活定制,進一步幫助客戶提升成本和空間效益。

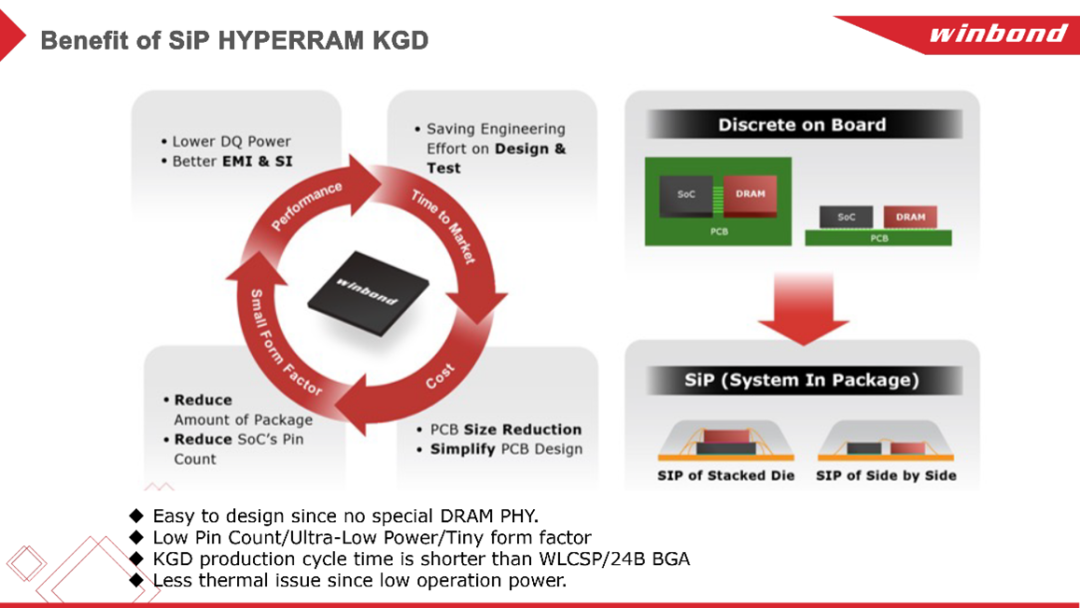

其中,憑借獨到的性能優勢,HYPERRAM 3.0 KGD 一經推出就席卷市場并備受好評。HYPERRAM KGD 的引腳更少、體積更小、設計更為簡潔,因此能夠更輕松地與客戶產品合封,同時得益于 HYPERRAM 的超低功耗,還可顯著降低合封后的發熱風險。

先進封裝

在深耕 KGD 產品的同時,華邦還致力于先進封裝技術的革新,采用TSV(Through Silicon Via)硅通孔技術進一步提升 DRAM 的性能與容量。目前華邦已經推出了全新的3D TSV DRAM(又名 CUBE) KGD 產品,兼具高帶寬與低功耗,能夠確保 2.5D/3D 多芯片封裝的能效,為客戶帶來優質的定制化內存解決方案。

此外華邦的 3DCaaS 一站式服務平臺,在為客戶提供優質 KGD 產品外,還將與合作伙伴共同為客戶帶來諸多工藝上的支持與產品技術咨詢,例如針對多芯片優化的 2.5D、3D 后段工藝和 Silicon-Cap、interposer 技術等附加服務。

隨著新能源汽車、5G、可穿戴設備等領域的不斷發展,對芯片性能的需求也越來越高。然而隨著后摩爾時代的到來,采用先進封裝技術的 Chiplet 則成為了芯片微縮化進程的“續命良藥”。除 UCIe 產業聯盟外,眾多頭部制造商也在圍繞 3D 封裝建立全新的生態聯盟,從封裝角度為 Chiplet 的發展保駕護航。華邦也將竭誠發揮自身在 KGD 產品和先進封裝領域的技術優勢,為業界提供優質的定制化內存解決方案,讓芯片在“長高”的路上越走越遠。

審核編輯 :李倩

-

芯片

+關注

關注

463文章

53949瀏覽量

464911 -

摩爾定律

+關注

關注

4文章

640瀏覽量

80811 -

封裝技術

+關注

關注

12文章

599瀏覽量

69264 -

chiplet

+關注

關注

6文章

493瀏覽量

13574 -

先進封裝

+關注

關注

2文章

530瀏覽量

1010

原文標題:Chiplet和先進封裝——后摩爾時代芯片演進的全新道路

文章出處:【微信號:Winbond華邦電子,微信公眾號:Winbond華邦電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

先進封裝時代,芯片測試面臨哪些新挑戰?

攜手伏達半導體:RedPKG解決方案助力封裝自主,加速產品創新

Chiplet封裝設計中的信號與電源完整性挑戰

Chiplet與先進封裝全生態首秀即將登場!匯聚產業鏈核心力量共探生態協同新路徑!

華大九天推出芯粒(Chiplet)與2.5D/3D先進封裝版圖設計解決方案Empyrean Storm

先進封裝轉接板的典型結構和分類

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

后摩爾時代:芯片不是越來越涼,而是越來越燙

Chiplet和先進封裝——后摩爾時代芯片演進的全新道路

Chiplet和先進封裝——后摩爾時代芯片演進的全新道路

評論