Chiplet仿真面臨的挑戰

Chiplet使系統擴展超越了摩爾定律的限制。然而,進一步的縮放給硅前驗證帶來了巨大的挑戰。24日,芯啟源EDA研發副總裁Mike Shei,工程及新產品副總裁Mike Li作了主題為"Incubating Chiplet - Challenges and Solution of New Emulators"的主旨演講,并將討論主題帶入次日的"Next Great Breakthrough in Chiplets"專家研討會。

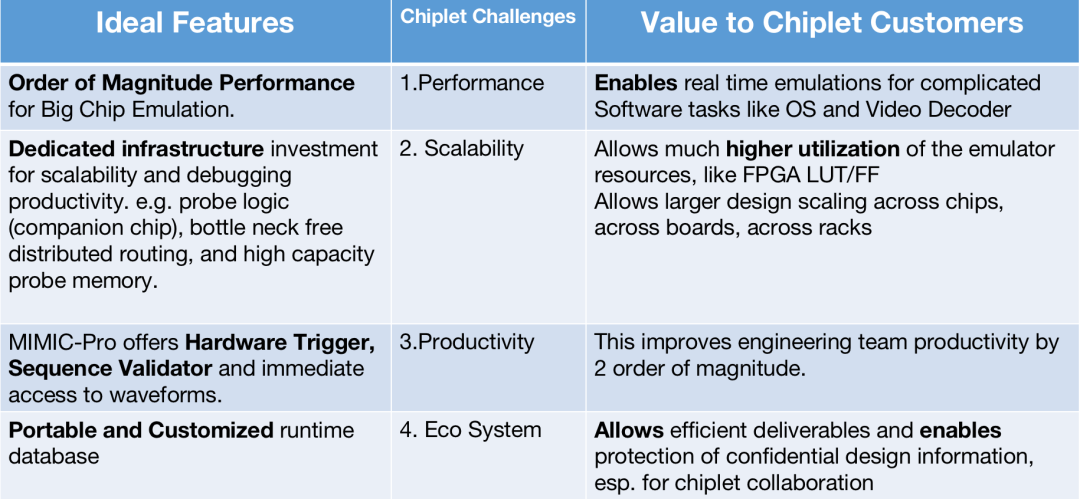

挑戰 1 - 性能和功能

傳統仿真器因集中式routing and clocking,隨著設計規模增加,性能呈指數級下降,Chiplet技術在增加系統復雜性的同時加劇了這一挑戰;

客戶實時操作系統、人工智能、視頻解碼仿真中,為提高性能,不得不放棄仿真器提供的調試功能。

挑戰 2 - 超大設計規模

小chiplet組成了大芯片系統,總設計規模高達500億個晶體管,對仿真加速器的可擴展規模及FPGA利用率提出了更高要求;

速度為10s, 100s of Tbps的多種chiplet接口。

挑戰 3 -工程效率

合理的編譯時間和運行時間,與軟件IDE處于同一數量級;

全局可見性和可控性,內置專用邏輯分析儀,觸發器,斷言,以精確定位波形,用于跨團隊調試;

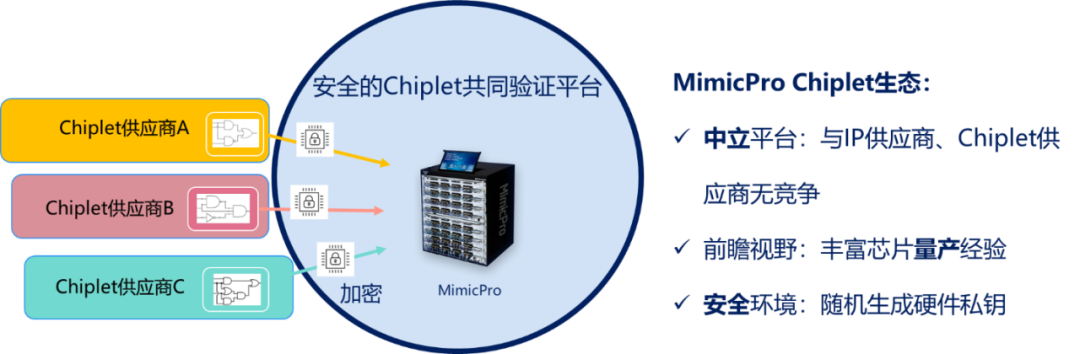

挑戰 4 -多個ChipletVendor的生態系統

虛擬集成來自多個供應商的異構chiplet設計,并在一個開放和安全的平臺上驗證它們。

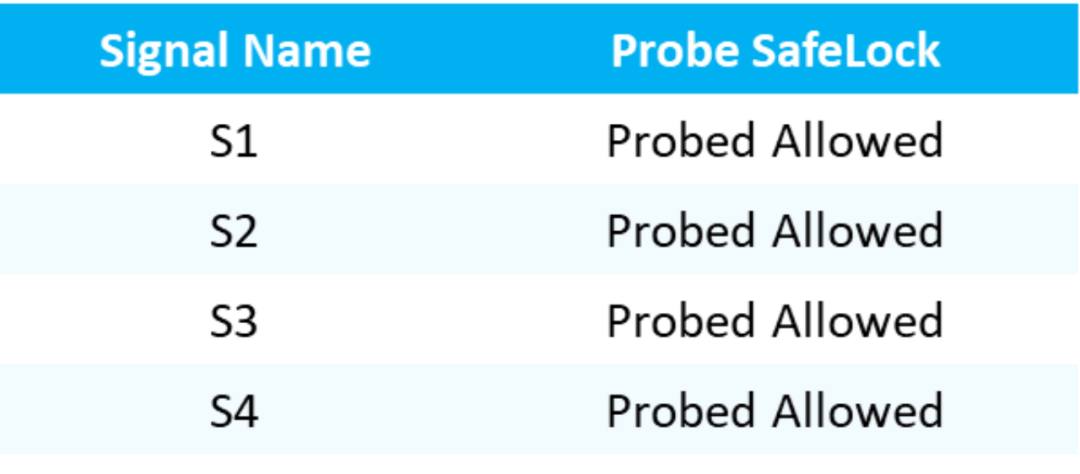

每個chiplet設計都需要有便攜性,且可定義需探測的信號。

芯啟源Chiplet集成平臺-MimicPro系列解決方案 01

應對 1 :

MimicPro分布式routing and clocking設計

MimicPro的分布式路由和多用戶時鐘在跨FPGA設計中可以保持較高運行頻率;

Chiplet級別的預編譯提高了編譯效率及運行頻率。

02

應對 2 :

MimicPro高度可擴展架構

分布式routing,無系統瓶頸,性能更高;

光纖端口可實現M32 系統之間的跨機柜高速互聯;

控制邏輯不消耗FPGA資源,大規模設計中實際FPGA利用率70%+。

03

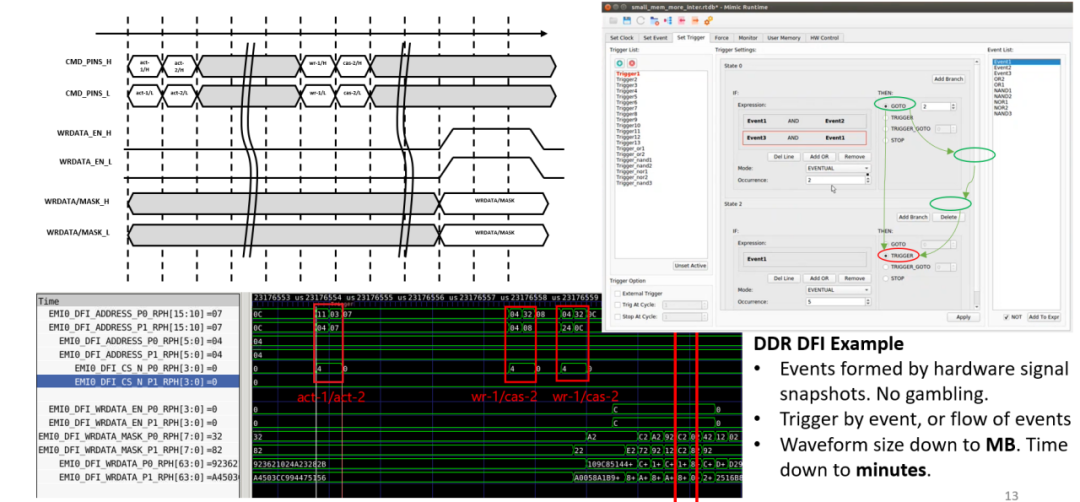

應對 3 :

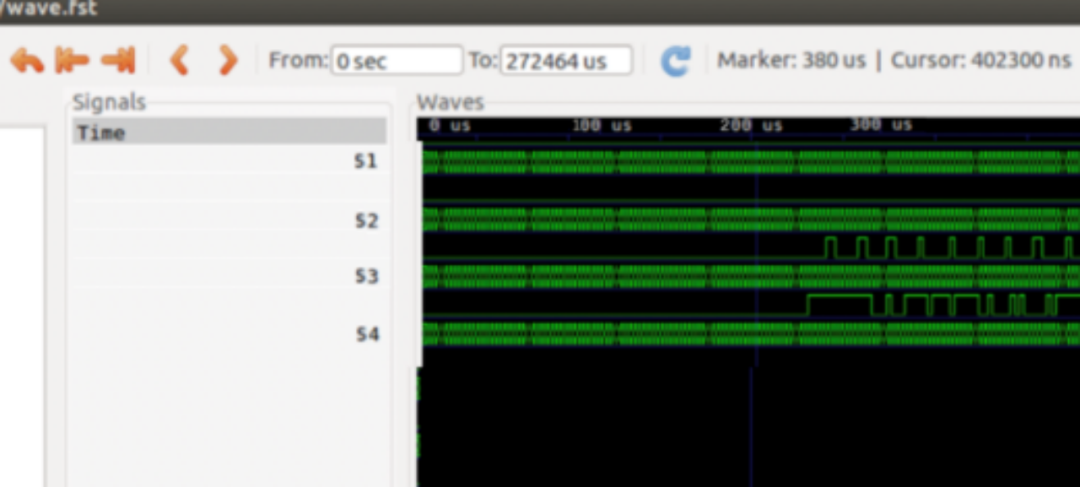

MimicPro豐富的調試功能

提供真正的HW Trigger-精確定位問題的數量級較小的波形,波形文件SizeMB vs GB;每張Solo卡搭配16GB DDR,豐富的調試/探針功能帶來高的工程效率;

多周期序列捕獲-能夠捕捉精確的快照,以評估事件的動態流;

從序列驗證到斷言加速-完全加速的DV環境。

04

應對 4 :

MimicPro提供中立安全的驗證平臺

RTDB包括bit stream & signaling,硬件配置,探針等信息;

RunTime信息可以修改,重新映射,刪除/過濾,以確保定義的調試范圍;

信號披露程度完全由chiplet供應商定義。

審核編輯:劉清

-

仿真器

+關注

關注

14文章

1050瀏覽量

87037 -

eda

+關注

關注

72文章

3108瀏覽量

182486 -

視頻解碼

+關注

關注

1文章

52瀏覽量

18766 -

chiplet

+關注

關注

6文章

493瀏覽量

13574

原文標題:Chiplet Summit|Chiplet時代芯啟源的探索之路(一)

文章出處:【微信號:corigine,微信公眾號:芯啟源】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

先進封裝時代,芯片測試面臨哪些新挑戰?

多Chiplet異構集成的先進互連技術

芯片可靠性面臨哪些挑戰

躍昉科技受邀出席第四屆HiPi Chiplet論壇

攻堅農業仿真挑戰:Robotec農業機器人仿真平臺

Chiplet封裝設計中的信號與電源完整性挑戰

解構Chiplet,區分炒作與現實

開發無線通信系統所面臨的設計挑戰

Actran聲學仿真解決方案:工業級聲學預測與優化的專業技術平臺

Chiplet與先進封裝設計中EDA工具面臨的挑戰

Chiplet仿真面臨的挑戰

Chiplet仿真面臨的挑戰

評論