異構集成取決于可靠的 TSV、微凸塊、過孔、線路和混合鍵合——以及消化所有選項的時間。

隨著摩爾定律的放緩,小芯片和異構集成 (HI) 提供了一種令人信服的方式來繼續改進性能、功耗、面積和成本 (PPAC),但是選擇連接這些設備的最佳方式以使它們以一致且可預測的方式運行是隨著選項數量的不斷增加,這成為一個挑戰。

更多的可能性也帶來更多潛在的互動。因此,雖然 AI、5G、高性能計算、移動和可穿戴設備中的下一代應用都受益于不同設備在緊湊封裝中的各種組合,但僅對不斷增加的互連選擇進行分類是一項挑戰。但有利的一面是,該行業不再受一套規則的束縛,定制和優化系統的可能性正在呈爆炸式增長。

Promex工程副總裁 Chip Greely 說:“異構集成的美妙之處在于它現在并不總是適用于電氣。” “你也可以將機電設備放入你的包裝中。對于我們的一些產品領域——例如,醫用相機——我們將機械和電氣功能整合在一個很小的空間內。如果你想擁有一個穩健的制造過程,你就會試圖讓你的接口盡可能容忍任何未對準或放置精度的任何變化,包括機械接口。”

三星、英特爾、臺積電和許多其他設備制造商正專注于優化各種架構中的芯片到芯片和芯片到封裝互連,無論是使用微凸塊、混合鍵合和橋接的垂直構建,還是使用扇出重新分布的水平構建層。決定如何以及在何處形成互連正在成為系統集成的重要組成部分。

封裝選項的數量正在增加,因為許多新設計都是針對特定應用高度定制的。因此,它們的構建和連接方式通常取決于需要處理的數據量和類型、需要處理的位置以及可用功率。例證:特斯拉的 D1 Dojo 芯片,這是一塊 500 億晶體管芯片,用于在特斯拉數據中心內訓練 AI 模型。特斯拉低壓電子產品副總裁皮特·班農 (Pete Bannon) 在最近的一次演講中表示,這里的重點是海量數據吞吐量,使用具有內置靈活性的高度并行計算。

特斯拉的設備基于臺積電的集成扇出 (InFO) 技術,在陣列中包含 25 個 D1 小芯片。Bannon 表示,該設備可以達到 9 petaflops,使用 576 通道的 I/O 環以每秒 36 TB 的速度移動。它還包括 3 個窄 RDL 層和 3 個厚 RDL 層。

與此同時,臺積電的路線圖要求采用可將電阻降低 40% 的新型低電阻互連。臺積電高級副總裁 Yuh Jier Mii 表示,該方案不是通過大馬士革制造,而是通過帶氣隙而不是電介質的減法金屬反應離子蝕刻制造,可以將電容降低 20% 至 30%,并最終用 2D 互連材料取代銅互連。研發。Mii 在最近的一次演示中表示:“隨著電阻率降低,未來有可能通過增強的互連性能進行擴展。”

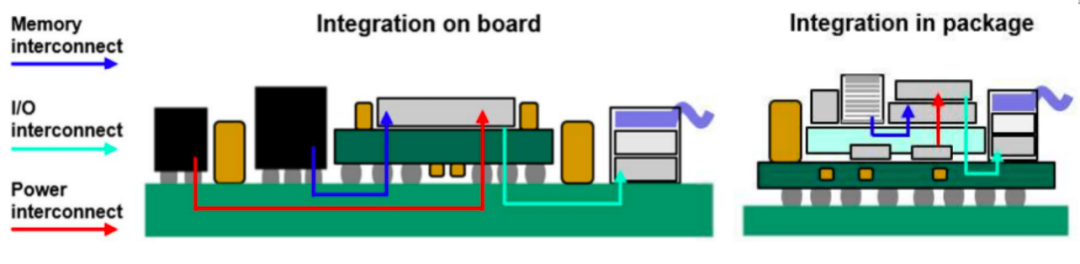

從板上芯片到異構集成的重新配置和互連路徑。來源:臺積電/IEDM

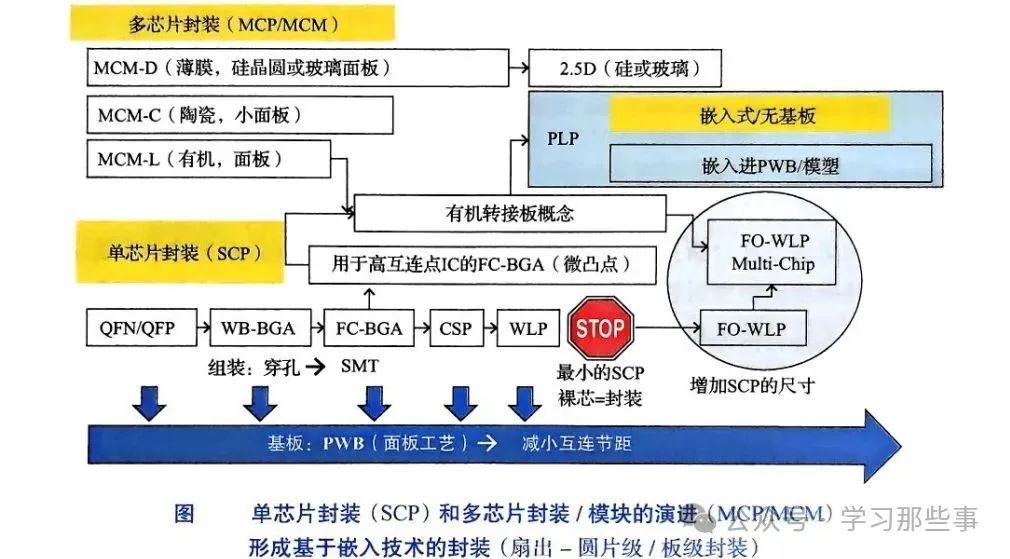

異質集成的路線圖正在通過混合鍵合、更多地使用硅橋、二氧化硅和尺寸越來越大的聚合物中介層轉向更多的芯片堆疊,為了滿足不同的最終用途,體系結構和封裝類型不斷增加。

不同的架構,優先級

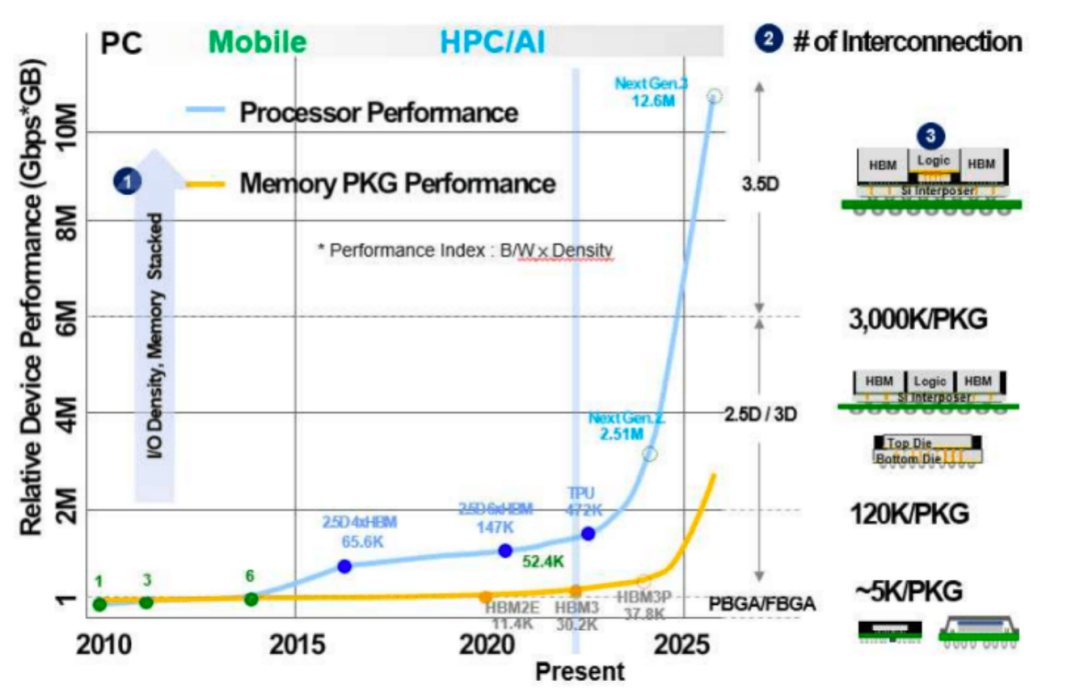

“先進封裝架構有望導致 I/O 互連呈指數級增長,”三星電子公司副總裁 Seung Wook Yoon 說。Yoon 在 IEDM上詳細介紹了該公司用于小芯片集成的先進封裝 FAB 解決方案 (APFS),重點介紹了先進封裝流程中的四個關鍵工藝——薄晶圓切割、混合鍵合、薄晶圓剝離(零應力)和垂直互連. “對于小芯片技術,晶圓厚度和凸點間距是關鍵參數。目前,最先進的 HBM 封裝的晶圓厚度小于 40μm,并將超過 16 個裸片堆疊到一個封裝中。”

三星有四種不同的封裝配置:2.5D RDL (R-Cube)、2.5D 硅中介層 (I-Cube)、3D-IC 堆疊、采用混合鍵合的 X-Cube 微凸塊和混合中介層 (H-Cube)。

高帶寬內存和 AI/高性能計算中不斷增加的互連數量。來源:三星/IEDM

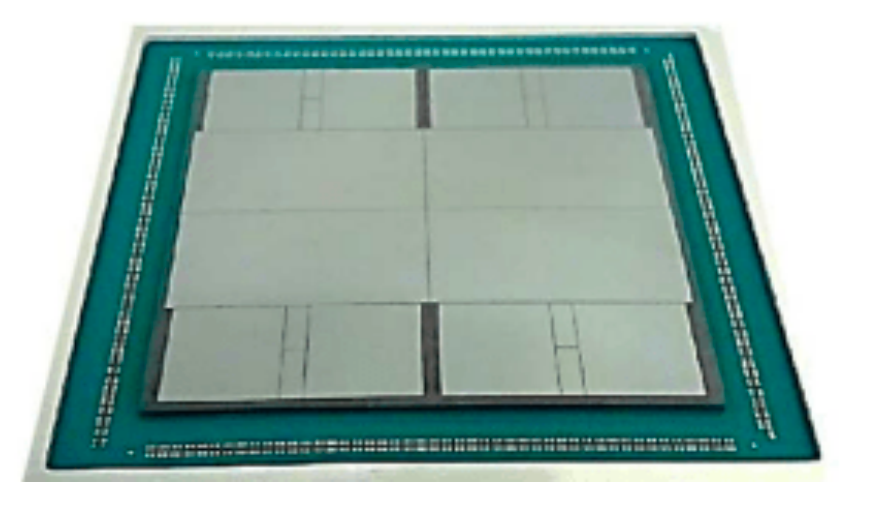

不斷增加的電氣、機械和熱問題也在推動 HI 工藝解決方案的發展。例如,臺積電展示了它如何解決由 4 個 SoC 和 8 個 HBM 在 78 x 72mm 基板上的 50 x 54 mm 有機中介層上組成的系統中的噪聲問題。在此設計中,用于芯片間連接的微凸塊的最小凸塊間距為 35μm。有機中介層(50 x 54 毫米或 3.3X 光罩尺寸)包含大約 53,000 條再分布層線。

約 53,000 條細間距 2um RDL 線形成總長 140 米,將 4 個 SOC 和 8 個 HBM 與層壓基板 (CoWoS-R) 上的有機中介層連接起來。來源:臺積電/IEDM

臺積電在其中介層電介質的 C4 凸點側集成了一個分立式去耦電容器,非常靠近 SoC 器件,以確保快速抑制電源域噪聲。這反過來又增強了 HBM 在高數據速率下的信號完整性。

熱問題雖然對半導體行業來說并不新鮮,但當更多的計算和電源管理設備彼此靠近放置時,熱問題會變得更加嚴重。Greely 指出了內存和電源管理 IC 等組合,它們通常必須在一個封裝內隔離。“電源管理就像一個老式的暖手器,而內存不喜歡超過 85°C,更不用說 100°C。”

中介層,無論是基于硅還是基于聚合物的薄膜,都有助于互連并充當異質芯片堆棧的應力消除緩沖器。壓力管理以及芯片移位最小化是晶圓廠開始從架構規劃和工藝方面著手解決的持續性問題。

ASE 在 IEDM 上展示了其三個垂直集成扇出封裝線的詳細信息。“對于 2.5D 和 3D,我們看到了密度和帶寬的增加。但我們也看到成本增加,這導致我們開發和引入了 ViPak 平臺,” ASE工程和技術營銷高級總監 Lihong Cao 說。“通過使用硅橋,L/S 芯片到芯片互連可以擴展到 0.8μm,甚至 0.65μm。所以在這個過程中,你最后放上管芯,但將橋接管芯放在載體上并使用銅柱連接。并且有兩個成型步驟。首先是保護橋模。所以我不使用 RDL 進行互連,連接是通過橋接裸片,你可以使用 65nm 工藝設計橋接裸片,然后最后貼上芯片。”

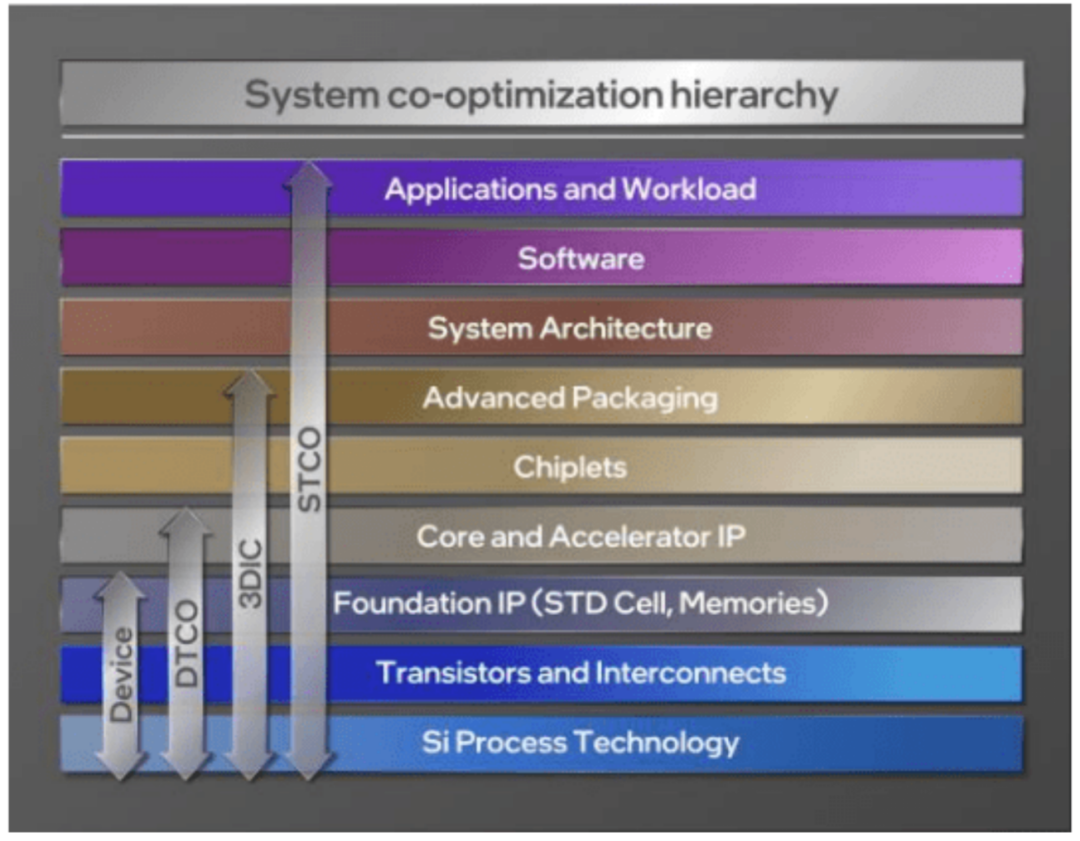

異構系統本身就是系統或子系統。他們需要系統技術協同優化 (STCO),這是 IEDM 慶祝晶體管發明 75 周年并展望下一個 75 年的主題。英特爾技術開發總經理 Ann Kelleher 表示:“慶祝晶體管的最佳方式是期待我們如何確保在未來 75 年內帶來盡可能多的創新。” “基于系統的技術協同優化 (STCO) 是摩爾定律的下一步發展。”

STCO 將設計技術協同優化提升到系統級,為一個或多個制造流程優化設計工具。根據 Kelleher 的說法,下一階段“就是我所說的從工作量開始工作。” 這包括系統和軟件的所有方面,直至整個制造過程,同時優化系統設計、軟件、設備、互連、晶體管等。

STCO 從工作負載開始,考慮晶圓廠和封裝制造和設計以及軟件和系統架構的所有方面。來源:英特爾/IEDM

在工藝技術方面,Kelleher 指出晶體管將在 2023 年轉變為環柵 FET,在 2025 年轉變為高 NA EUV,下一代互連金屬、鐵電材料,以及光學互連的最終結合。

混合鍵合

混合鍵合它同時鍵合了銅對銅焊盤和電介質對電介質場,提供了終極的垂直連接。相對于銅微凸塊,混合鍵合可將信號延遲降至接近零,同時使凸塊密度提高 1,000 倍。微凸點間距目前在 35μm 以上。對于混合鍵合,正在評估小于 20μm 的間距。

“我們正在與客戶就幾個有趣的混合綁定用例進行交流,包括高帶寬邊緣 AI 設備和 RF 組件。根據應用的不同,應用混合鍵合的好處可以是更高的性能和/或更強大的功能,在外形尺寸限制內,” UMC技術開發總監 Tony Lin 說。

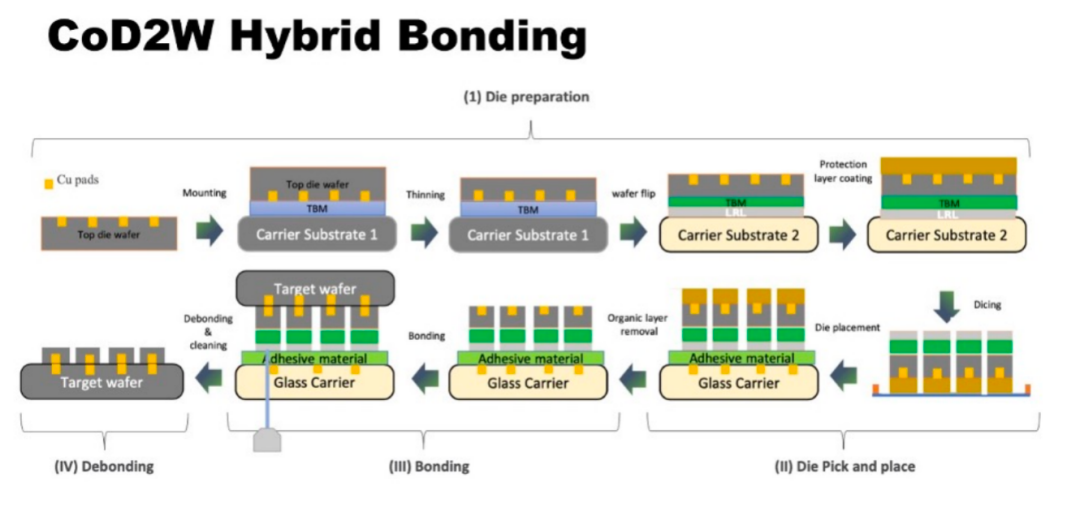

清潔界面和精確對準是具有生產價值的混合鍵合工藝的關鍵要素。晶圓對晶圓鍵合和芯片對晶圓鍵合工藝均可用。W2W 更成熟,但它需要相同尺寸的芯片,幾乎沒有靈活性。芯片到晶圓的流程更加復雜,并且容易受到芯片放置對齊不準確的影響。提高貼裝精度的一種方法是同時對多個裸片執行共用 D2W 鍵合。也有多種脫粘方法,重點是最大限度地減少基板應力、降低成本和提高產量。

例如,熱方法成本低,但會引入壓力,并且產量低。Brewer Science副主任 Alvin Lee 表示,化學方法可以在室溫下進行,但通量仍然很低。激光剝離提供更快的吞吐量和低應力,但設備成本高。下一代光子剝離使用高強度光從玻璃上快速剝離晶圓,以更適中的工具成本引入很小的應力,Lee 指出。共用D2W 混合鍵合是扇出封裝的使能技術。

芯片到晶圓混合鍵合的工藝流程提供了比單獨拾取和放置更高的吞吐量和卓越的對準精度。來源:Brewer Science

混合鍵合的早期采用者的額外好處之一可能是他們能夠實現相當于技術節點轉換的性能提升。“我們的客戶繼續需要在他們的 IC 設計中實現更快的性能、更高的電源效率和更低的成本,這在過去是通過縮小晶體管來實現的,”UMC 的 Lin 說。“隨著跟上摩爾定律變得更具挑戰性和成本更高,混合鍵合可以提供我們客戶尋求的性能改進,使其成為技術節點遷移的靈活替代解決方案。”

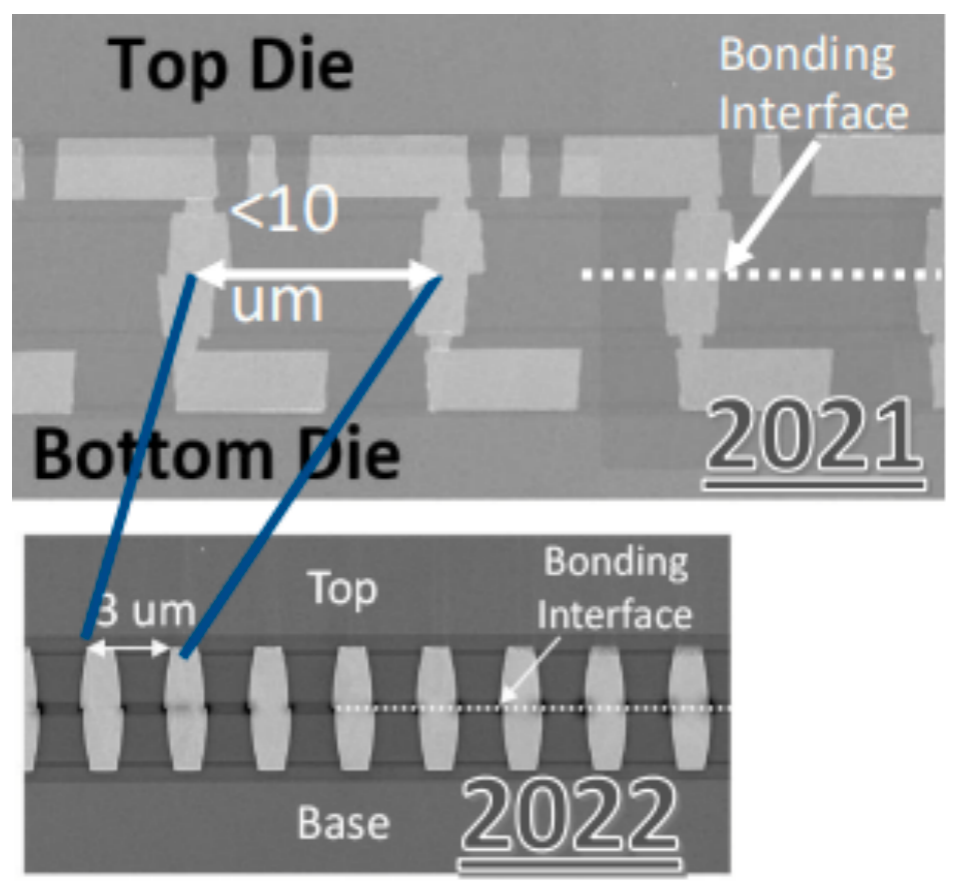

英特爾透露了其在混合鍵合方面的研發進展,從 2021 年的 10μm 間距銅-銅鍵合擴展到上個月的 3μm 間距鍵合。一些專門針對混合鍵合優化的新工藝模塊包括調整 PECVD 氧化物沉積工藝以沉積厚 (20μm) 的低應力薄膜,改進氧化物 CMP 漿料以加快拋光速度,以及創建高縱橫比蝕刻和填充工藝對于通過電介質過孔。

2021 年演示了間距為 10μm 的混合銅-銅鍵合,2022 年演示了間距為 3μm 的混合銅-銅鍵合,密度增加了 1,000 倍。來源:英特爾

但這些過程也有一些問題需要解決,這需要時間。例如,芯片移位可能是先進封裝和異構集成的一個重要問題。Greely 說:“也許您的互連焊盤尺寸過大,這樣您就可以為任何芯片移位做出妥協。” “當你放下 RDL 層時,注冊將是關鍵。”

插入結構

插入結構本身不是分立元件。它是芯片(或芯片)和下面的層壓基板之間的中間結構。盡管業界經常提到硅中介層,但構成硅中介層的材料都是電介質,即二氧化硅。基于聚合物的中介層比硅中介層便宜得多,但它們在某些應用中缺乏可靠性。

臺積電探索了有機中介層在電氣性能、翹曲控制、良率和可靠性方面的優勢。“傳輸損耗是線路長度的函數。對于固定的每比特能量功耗設計預算,需要縮短互連長度以實現高帶寬,”臺積電后端技術服務部總監 Shin-Puu Jeng 說。

該代工廠一直致力于提高其堆疊技術的可靠性。“當你進入高速時,CoWoS-R 的優勢更大,因為 RC 的優勢在高頻下衰減得更慢,”Jeng 說。CoWoS-R 中的有機中介層由聚合物中的銅線組成(介電常數 = 3.3)。“非常密集的垂直連接可實現低阻抗電力傳輸網絡。銅/氧化物模擬眼圖,氧化物中較薄的銅,聚合物中的銅,表明聚合物中銅的線長具有更大的靈活性。在 CPU 到 HBM 互連的情況下,長 RDL 互連(L/S = 2μm/2μm)變厚(4μm)以減少高速數據傳輸的負載,同時也改善 IR 壓降用于供電網絡。與薄或厚 TSV 相比,聚合物通孔的插入損耗更低。RC 延遲會影響功耗。電力傳輸具有水平和垂直傳輸組件。非常密集的垂直連接提供低阻抗 PDN。去耦電容器對于抑制電源噪聲和實現穩定的電壓供應很重要。”

建立橋梁

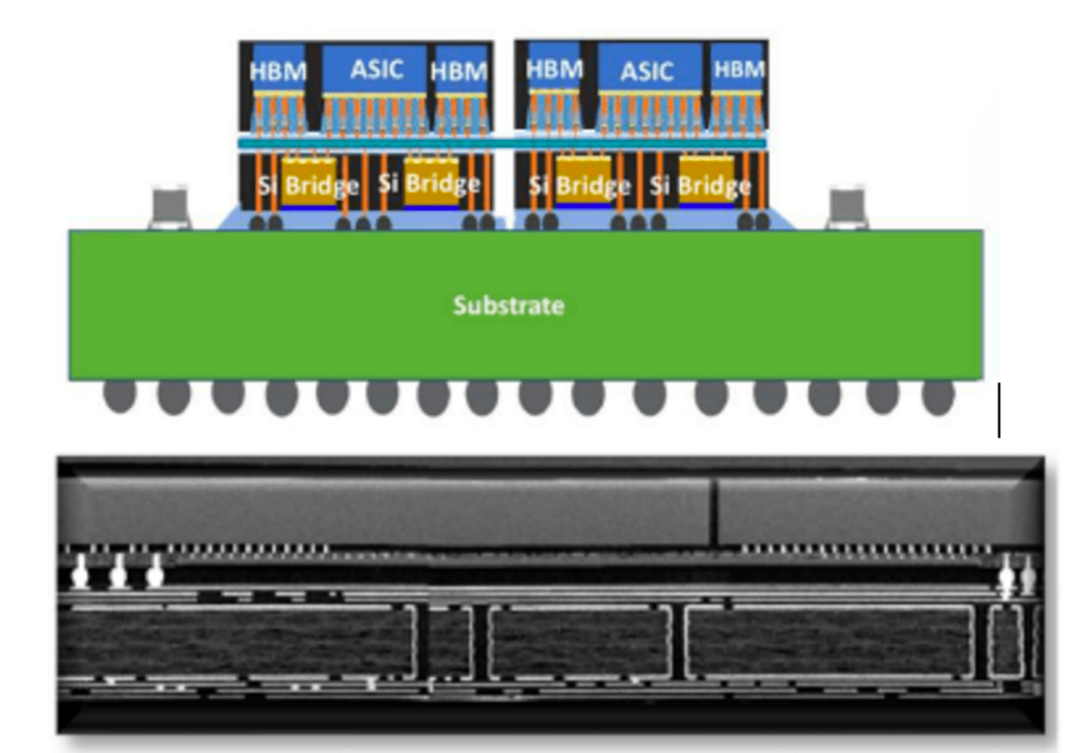

英特爾和臺積電一直在使用專有的硅橋技術來互連高帶寬內存模塊和 CPU/GPU。ASE 最近推出了一個帶有嵌入式橋的封裝平臺,能夠以 0.8 μm 的線和間距 (FoCoS-B) 連接小芯片到小芯片。

“由于固有的扇出 RDL 工藝限制,FOCoS-CF 和 FOCoS-CL解決方案在制造具有高層數(>6 層)和細線/間距(L /S = 1μm/1μm),適用于需要高密度 die-to-die 連接、高輸入/輸出計數和高速信號傳輸的應用,”ASE 的 Cao 說。FOCoS-B 為多個橋接芯片集成提供了多種選擇。在一個示例中,8 個硅橋芯片嵌入到兩個相同的扇出 RDL 結構中,具有 2 個 ASIC 和 8 個 HBM2e 模塊。它們使用兩個相同的扇出模塊進行安裝,這些模塊組裝在 MCM 中的一個倒裝芯片 BGA 基板上。FO 模塊均為 47 x 31mm,封裝體尺寸為 78 x 70mm。

基板橋上的扇出芯片 (FOCoS-B) 原理圖(上圖)和橫截面圖(下圖)實現了比 RDL 更小的芯片到芯片連接 (0.8μm)。來源:ASE/IEDM

Cao 解釋說,ASE 工程師通常還比較了 2.5D 與芯片在后和芯片在前的 FOCoS 方法的插入損耗、翹曲和可靠性。由于消除了硅中介層并減少了寄生電容和串擾,兩種 FOCoS 方法都展示了優于 2.5D Si TSV 的電氣性能。封裝級翹曲,主要由芯片和基板以及扇出模塊之間的 CTE(熱膨脹系數)不匹配引起,顯示出更好的翹曲控制,并且所有封裝都在組裝前通過了開路/短路和功能測試,以及可靠性壓力測試 JEDEC 條件。

但這仍然不簡單。“當我設計 BGA 基板時,銅平衡被敲打到我身上,以確保我們制作出良好的直板基板,”Promex 的 Greely 說。“現在,銅平衡是單個封裝級別的問題,我將 7、10、12 個不同的器件放入不同的溫度下,將它們貼附到基板上,我得到 12 到 14 微米從一個溫度到另一個溫度的翹曲變化。如果我有一個 50 毫米的基板,它有 250 微米的偏轉,在室溫下是凹面的,而在 300 度時則相反,現在它是凸面的。我正在嘗試將一塊漂亮的 25 微米背景硅放在那個東西上,并希望它在冷卻回室溫后保持一體。這可能是一個極端的例子,但這些都是嚴峻的挑戰。”

熱管理

在封裝中,超過 90% 的熱量通過封裝從芯片頂部散發到散熱器,通常是帶垂直鰭片的陽極氧化鋁基散熱器。具有高導熱性的熱界面材料(TIM)放置在芯片和封裝之間以幫助傳遞熱量。用于 CPU 的下一代 TIM 包括金屬板合金(如銦和錫)和銀燒結錫,它們分別傳導 60W/mK 和 50W/mK。

工程師和材料供應商繼續探索替代 TIM。Amkor Technology的高級機械工程師 Nathan Whitchurch 說:“過去稀有的材料正變得越來越稀有”. “因此,對于燒結銀,您最終會在蓋子和管芯之間形成導熱性非常高的銀合金基體。另一種是較軟的 TIM——銦基類型的東西。幾年前,我們經常談論相變材料。這似乎已經消失,因為人們意識到可靠性和優勢并不存在。石墨墊之類的東西具有難以克服的工程挑戰。單一方向上的石墨具有高導熱性,但將其裝入封裝中是一項艱巨的挑戰。所以這就是我們看到隨著時間的推移,更奇特的材料變得不那么奇特的地方。”

結論

高級封裝中的小芯片通過焊料、微凸塊、RDL 和混合鍵合進行電氣互連。所有這些連接都需要在模塊的使用壽命內保持可靠。隨著封裝類型的激增和壓力更低的新工藝的出現,工程師們發現異構集成提供的靈活性可能值得所有挑戰。

關于小芯片和異構集成的討論通常不會提及該行業采用這種新范式的時間有多早。“UCIe 是一個非常好的開放標準,”ASE 首席執行官 Bill Chen 說。“有些人跑得比標準還快。但隨后會有用戶的反饋。” 然后,該反饋循環將更深入地了解未來需要什么。此外,供應商-客戶生態系統將了解哪種類型的異構集成、組裝技術、流程、設計工具等最有效。這將是一個過程。

三星的 Yoon 表示:“半導體才剛剛開始其小芯片和異構的旅程,因為設備縮放變得如此困難和昂貴,而且 PPAC 正在隨著每個先進節點而縮小。” “小芯片設計標準將變得更加普遍,將這些設備組合在一起的更可預測的方式將接管。但所有這一切都需要數年時間,需要收集大數據、合作伙伴之間的協作以及跨價值鏈實驗來確定什么是有效的。”

審核編輯 :李倩

-

芯片

+關注

關注

463文章

54010瀏覽量

466077 -

晶圓

+關注

關注

53文章

5410瀏覽量

132293 -

異構

+關注

關注

0文章

47瀏覽量

13544

原文標題:巨頭云集的異構集成

文章出處:【微信號:ICViews,微信公眾號:半導體產業縱橫】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

疆鴻智能EtherCAT轉DeviceNet網關:制藥產線異構集成的關鍵樞紐

多Chiplet異構集成的先進互連技術

西門子Innovator3D IC異構集成平臺解決方案

疆鴻智能MODBUS TCP與PROFIBUS在核電廠的異構集成解決方案

Chiplet與異構集成的先進基板技術

【2025九峰山論壇】破局摩爾定律:異質異構集成如何撬動新賽道?

【飛凌T527N開發板試用】異構RISC-V核心使用體驗

2025中國工博會集成電路展區陣容揭曉!行業巨頭齊聚,共繪“芯”藍圖

基于硅基異構集成的BGA互連可靠性研究

基于板級封裝的異構集成詳解

米爾瑞芯微多核異構低功耗RK3506核心板重磅發布

AI時代,封裝材料如何助力實現更優的異構集成?

上揚軟件助力12英寸異構堆疊芯片企業建設MES系統項目

最新議程出爐! | 2025異質異構集成封裝產業大會(HIPC 2025)

巨頭云集的異構集成

巨頭云集的異構集成

評論