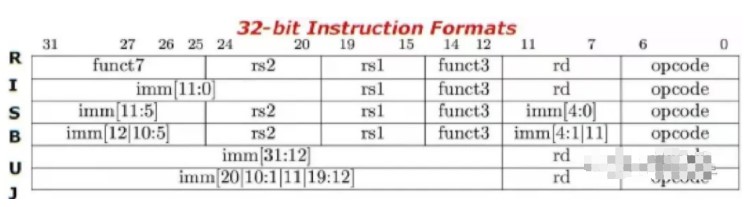

我們來回顧一下上期內容:我們定義了兩種指令,第一種是立即數指令,其指令規則是:xxxxxxxxxxxx(立即數)xxxxx(源寄存器序號)xxx(運算規則)xxxxx(目標寄存器序號)1(立即數標志位)。第二種指令是寄存器指令,其指令規則是:0000000xxxxx(源寄存器序號1)xxxxx(源寄存器序號2)xxx(運算規則)xxxxx(目標寄存器序號)0(立即數標志位)。不過呢,這些指令只是我們的一廂情愿,現實中實際的指令集是怎么實現的?

RISC-V指令格式

我們這次來講講RISC-V指令集,看看他們的指令集是如何設計的。

RISC-V指令集項目在2010年始于伯克利大學,是一個新穎先進的指令集。我們曾在前幾章中多次提到過這個指令集,不過也就是順嘴一題,這次我們具體看看究竟什么是RISC-V指令集。

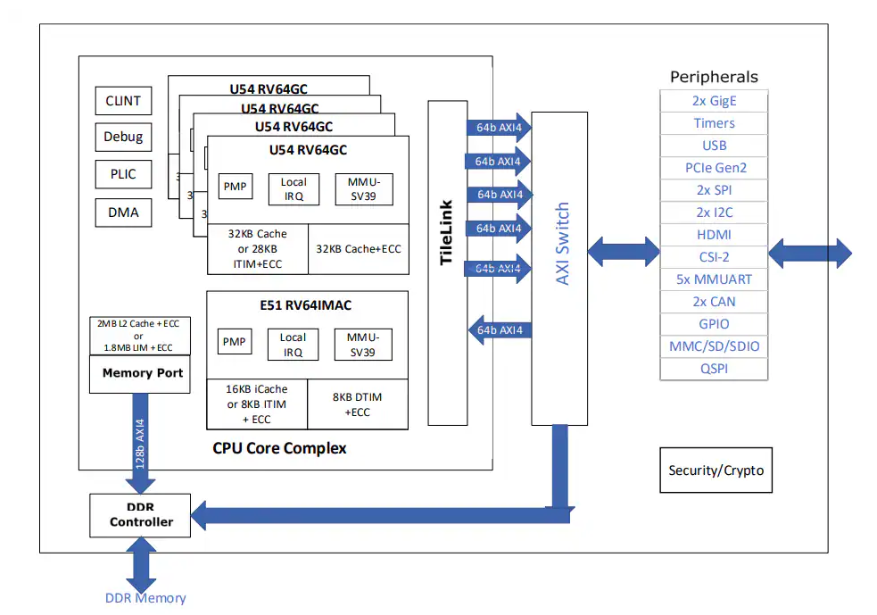

首先RISC-V指令集由幾部分組成。最主要的部分是最基礎32位的RV32I,這部分是最基礎的指令集,是兼容RISC-V程序的必要部分。其次是16位的RVC,作為壓縮指令,可以極大節省程序占用內存的空間。再者是32位的RV32M,用以支持乘除法指令。此外還有RV32F、RV32A等等。為什么要分成這么多部分呢?因為我們設計的CPU大多不會對這些指令全部兼容,而是選擇有目的的部分兼容。比如,設計一個低功耗的單片機CPU,我們就用不到乘除法等指令,我們可以選擇只兼容RV32I,既簡單又高效。當然這些指令還有64位版本,用以支持更高位數的計算。

RISC-V指令集規定了CPU中有32個寄存器。有疑問嗎?你可能覺得指令集不就是指令的集合嘛,為什么還規定我們的硬件設計?不要忘了,32個寄存器意味著寄存器序號一共是5位,而這是由指令集決定的。順便一說X86指令集中僅規定有8個寄存器。其中,00000即第一個寄存器本質并不是寄存器而是硬件連線0,始終代表數字0。這個設計是有意義的,可以借此寫出許多騷操作的指令。

我們先講最基礎的RV32I指令集。作為最基礎的指令集,其包括幾種指令類型。分別是數字運算指令(包括寄存器指令和立即數指令)、pc跳轉指令、分支指令和內存讀寫指令。我們上次定義的指令集屬于數字運算指令,二者類型相同但內容并不完全一致。現在我來說說RV32I中的數字運算指令,你們可以和上次定義的指令集比比有何不同?這些差別能帶來好處還是壞處?

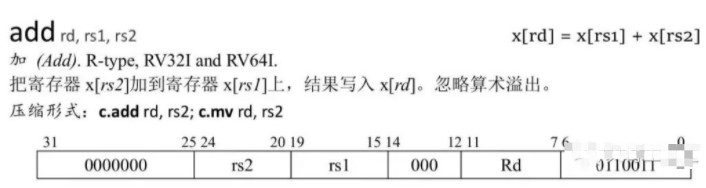

add指令釋義

首先是運算指令。RV32I一共定義了10種運算,分別是加法、減法、有符號比較、無符號比較、與、或、非、異或、邏輯左移、邏輯右移和算數右移。而這些運算分為寄存器指令和立即數指令。立即數指令中是無需減法指令的,因為我們曾經說過,減法可以通過對其中一個加數取反加一再與另一個加數求和實現,所以立即數可以直接在立即數上做文章,不需要減法指令。那我們是否需要十種運算電路來分別對應這十種計算指令呢?不用,我們只需要八種。少的那兩種分別是減法和移位。減法完全可以復用加法電路,左移完全可以復用右移電路。什么是復用?為什么要復用?復用就是重復利用原有的電路,減少設置新的電路。這樣可以節省芯片面積,節約生產成本,降低發熱功耗。那么如何復用呢?不同的電路有不同的復用方法,以減法復用加法為例,使用加法電路前,將其中一個數取反加一便可成為減法電路。

綜上所述,我們仍需要3位數字表示這八種運算邏輯,它們分別是000到111,這三位數字被稱為funct3(3位功能數字)。不過加法和移位運算中需要額外的一位數字用以區分加減和左右。這一位數字在哪呢?我們先講立即數移位指令,立即數一般是12位數字,但在移位運算中用不到這么多位數,一般只有5位。那么在這五位數之前會有7個空位,第二個空位便是這位數字所在。立即數加法指令不需要這一位數字,原因剛才有指出。寄存器指令中,同樣會存在7位空位,第二位空位是這位數字所在。

然后我們講一下另一類指令,內存讀寫指令。不過我們在此之前需要指出一件事,我們現在有兩種指令類型了,分別是運算指令和內存讀寫指令,我們怎么區分呢?RV32I設置了另一種功能數字,funct7(7位功能數字),為什么會有七位呢?因為指令類型很多,funct7不單起到區分RV32I指令類型的作用,同時還區分所有RISC-V的所有指令,甚至還包括16位和64位指令,所以funct7會有7位數字。回到內存讀寫指令上來,讀和寫可以被看成兩種類型,需要一位數字區分,這位數字在funct7中。讀和寫都需要地址,否則不知道讀哪或是寫哪。

同時讀指令還需要知道取到的內容放到哪,而寫指令需要知道寫什么內容。先說地址,地址是由某一寄存器中的數字加上七位立即數得到,這樣正好組成之前說的12位數字。讀指令放到哪呢?放到目標寄存器嘛。寫指令的內容從哪來呢?來源寄存器嘛。這不就和之前的指令樣式對應起來了嗎?所以這兩種指令樣式區別其實不大。只不過執行內容有所區別。

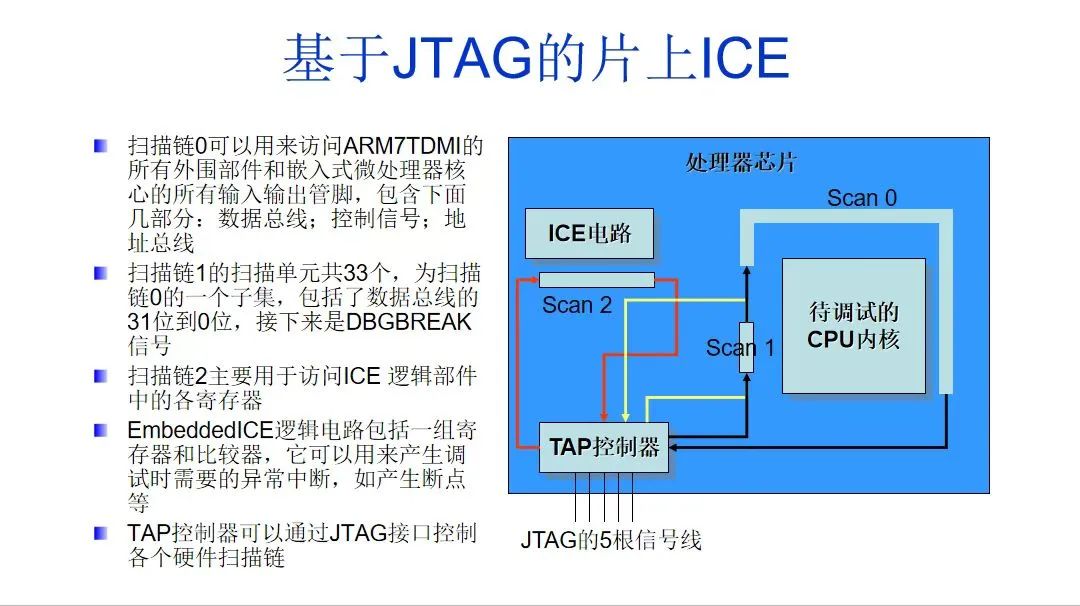

我們現在剛剛簡單講完兩種指令類型,是不是很多人就已經迷失自我了?難道所有這些指令規則只能通過繁瑣的文字來講述嗎?這里就要提到指令集圖卡了。

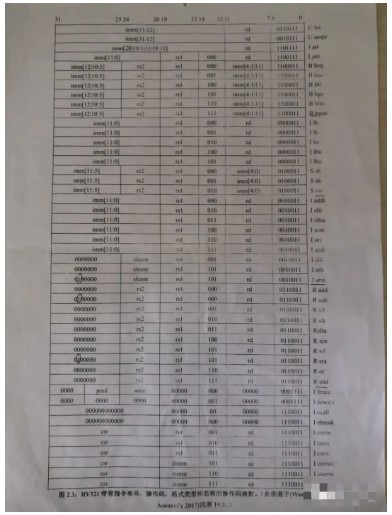

RV32I指令集圖卡

上圖就是實拍RV32I指令集圖卡,每一行都代表著一條指令,你所要做的便是填入對應的寄存器序號和立即數即可。其中rs1和rs2分別是來源寄存器1和2,rd是目標寄存器,imm是立即數。有的指令可能只需要一個來源寄存器甚至一個都不要,有的指令可能不需要目標寄存器,有的指令可能需要12位立即數,有的則可能要20位立即數。這些在指令集圖卡中都體現出來了。看到右邊英文中,我手寫的幾道黑橫線了嗎?夾在里面的指令是我們在前文中所講的指令類型,可以再根據這張圖對前文進行理解,會容易得多哦。

舉個例子,比如加法指令,看到最右側有兩個add,分別是I addi和R add,區別在于一個是立即數加法,一個是寄存器加法。對應到靠右邊的方框中是不是可以看到7位數字,這就是funct7,中間有3位數字000,這就是funct3。寄存器指令中的最左側7位數字是空著的為0000000,而立即數指令中最左側則是12位的立即數。再看R add下面的R sub,與R add唯一的區別是不是左邊第二位數字變成了1?這就是之前所說的復用所需的那一位數字。現在是不是能完全和之前所說的聯系起來了?也沒那么難對吧?

剩下的下次再來吧?還是你們剩下的都能自己看懂了?可以找公眾號回復一下,我想看看。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5615瀏覽量

130316 -

減法電路

+關注

關注

0文章

15瀏覽量

8307 -

指令集

+關注

關注

0文章

229瀏覽量

24423 -

RISC-V

+關注

關注

49文章

2931瀏覽量

53431

發布評論請先 登錄

中移芯昇亮相“芯動未來”沙龍:深度解析XVA架構,共筑DSP算力新格局

新思科技STING助力破局RISC-V架構驗證復雜度

新思科技ARC-V處理器驅動RISC-V市場無限機遇

高通收購Ventana Micro Systems,深化RISC-V CPU技術專長

RISC-V指令集手冊中F指令部分

提高RISC-V在Drystone測試中得分的方法

RISC-V B擴展介紹及實現

明晚開播 |開源芯片系列講座第29期:RISC-V AI芯片的創新和應用

PIC64GX1000 RISC-V MPU:一款面向嵌入式計算的高性能64位多核處理器

明晚開播 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

RISC-V芯片出貨超百億顆!四大廠商重磅產品來襲,加速邊緣AI終端落地

芯華章RISC-V敏捷驗證方案再升級

直播預約 |開源芯片系列講座第28期:高性能RISC-V微處理器芯片

【好書推薦】RT-Thread第18本相關書籍!RISC-V嵌入式系統設計 | 技術集結

進迭時空同構融合技術加速大模型AI應用創新

RISC-V指令集是如何設計的

RISC-V指令集是如何設計的

評論