前言:

都知道FPGA的啟動方式有很多種,比如JTAG、SPI,BPI,SeletMAP,Serial等等吧,又分為主從即Master和Slave(時鐘由FPGA的管腳發出,專用的CCLK信號為主,否則為從,有的配置有輔助時鐘EMCCLK,它由外部的晶振提供,從FPGA的EMCCLK輸入,經過專用的邏輯,再從CCLK管腳輸出給想用的器件,),那么問題來了,配置失敗怎么辦呢??????????????看DONE管腳呀,你已經失敗了 ,一般情況下DONE管腳是低電平,另尋途徑了 只有。。。。。。

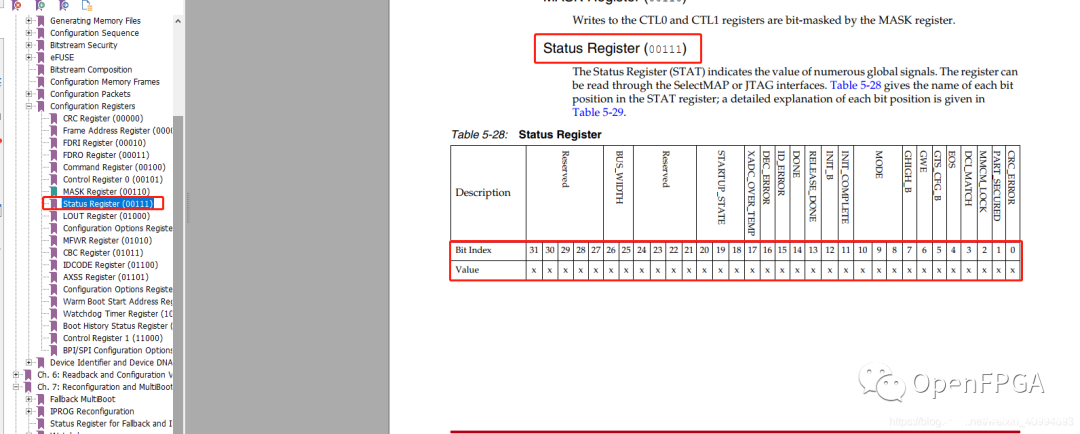

只有一個辦法,廠家已經給你想好了 看狀態寄存器(相應手冊的),它可以很快的輔助你找到配置失敗的原因,不管你是哪個系列的或者使用的是ISE也好,Vivado也罷,Xilinx FPGA的狀態字,在它的所有系列器件當中,關于狀態位的定義基本保持一直,但是也有一些細微的差別,建議看相應系列的數據手冊,比如我所要調試的時V-7,我查看Ug470

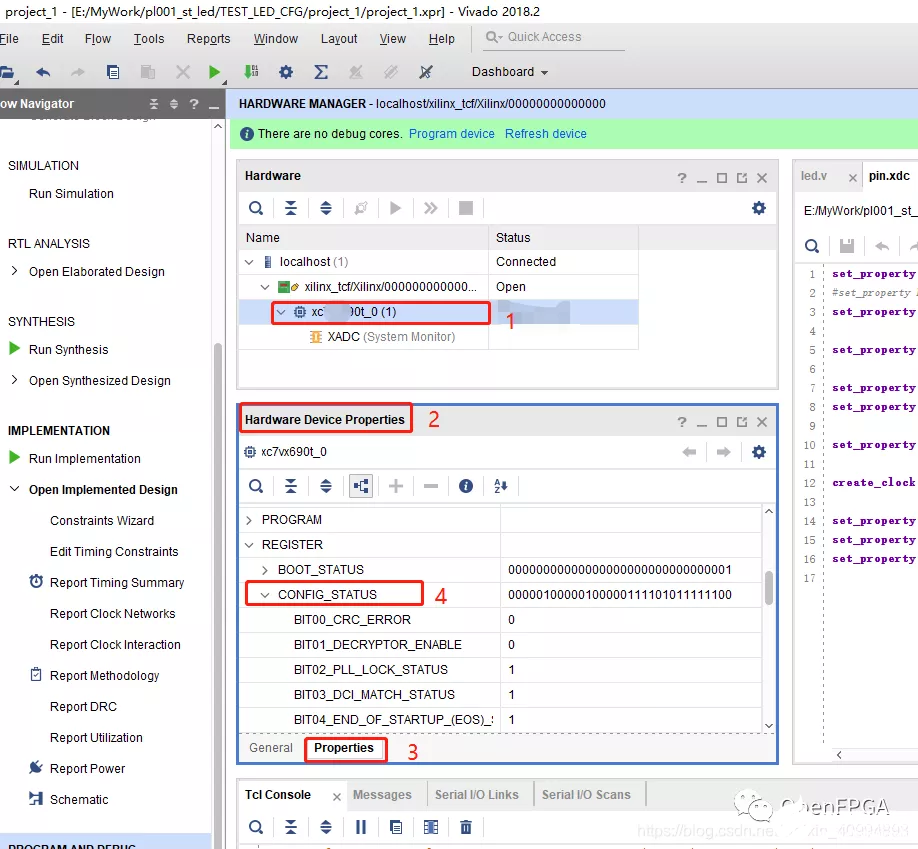

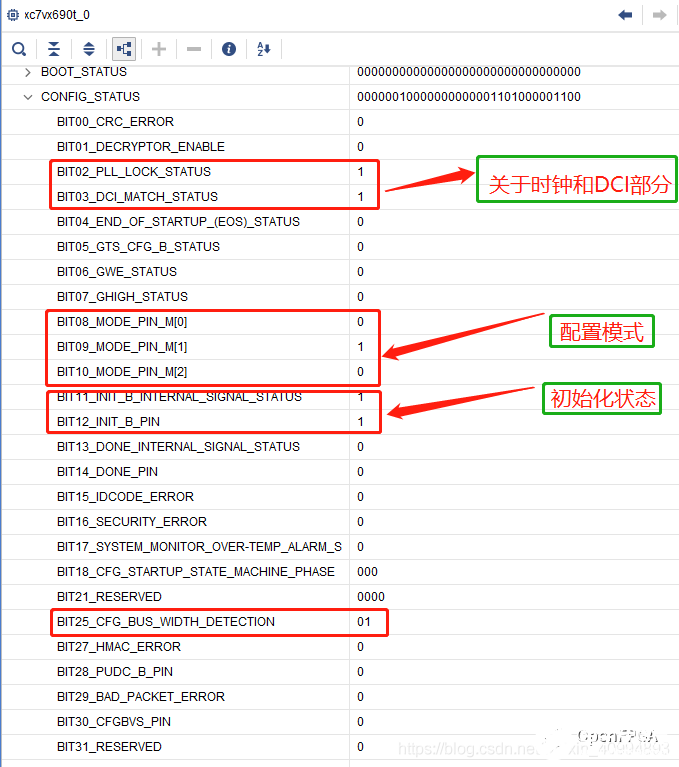

每一位的解釋已經很清楚了 ,那么我們怎么讀出這些狀態字呢,首先我們拿出一塊FPGA,連接好下載線和板子,板子上電,打開JTAG,Hardware Manager 窗口顯示如下:

將鼠標選中1(我們的器件),擦看2處,點擊3處,查看4處,我們來展開配置狀態的寄存器,同時對照上面的對每一位的解釋大概說一下把,

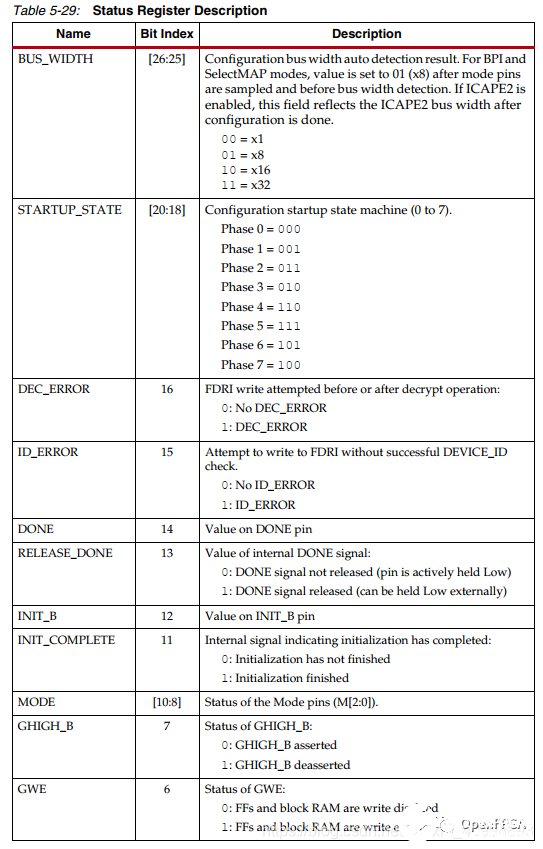

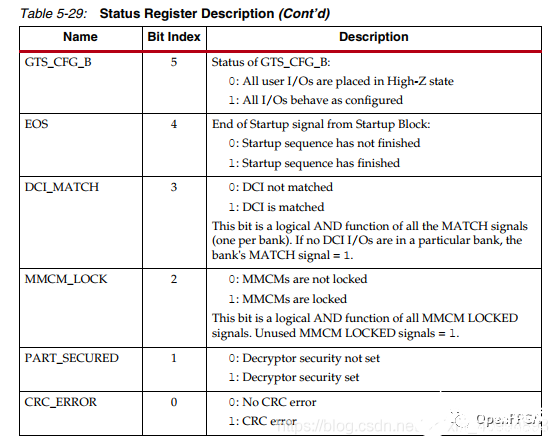

只有BIT02 PLL_LOCK, BIT03 DCI_MATCH, BIT11 INIT_B_INTERNAL, BIT12 INIT_B_PIN(即初始化狀態和時鐘及DCI部分)的值必須是1;

BIT08-10 MODE PINS(配置模式),BIT21 SECURITY_STATUS, BIT25-26 BUS_WIDTH,BIT28 PUDC_B根據FPGA和板子具體的設定,可以為1或者0,其他都必須是0。

這樣大概就能夠判斷你的板子的狀態了,如果出現其他的值,那么可以能你的配置電路出現了問題,還有其他的出現的比較典型的值,下次再給大家討論吧。

編輯:lyn

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636268 -

Vivado

+關注

關注

19文章

857瀏覽量

71106 -

狀態寄存器

+關注

關注

0文章

39瀏覽量

7403

發布評論請先 登錄

Atmel AT17LV系列FPGA配置EEPROM的全面解析

深入解析FSA8049音頻插孔檢測與配置開關

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

【ALINX 教程】FPGA Multiboot 功能實現——基于 ALINX Artix US+ AXAU25 開發板

電能質量在線監測裝置精度等級校準失敗后,有哪些補救措施?

一文詳解xilinx 7系列FPGA配置技巧

如果在配置位中啟用了看門狗(WDT)功能,是否會影響ISP升級過程呢?

變壓器過負荷如何處理,五個應對措施讓你輕松應對

寬溫啟動失敗?聚徽揭秘防爆顯示屏-40℃低溫啟動的加熱膜配置技術

【經驗分享】玩轉FPGA串口通信:從“幻覺調試”到代碼解析

如何應對步進電機的各種干攏問題

Linux內核編譯失敗?移動硬盤和虛擬機的那些事兒

芯片流片失敗都有哪些原因

如果FPGA配置失敗的應對措施解析

如果FPGA配置失敗的應對措施解析

評論