很多開發者第一次接觸 FPGA,都會有同樣的疑問:FPGA 是硬件,不是軟件,怎么寫程序?答案就是用硬件描述語言(HDL),最常用的就是Verilog和VHDL。今天,我們就帶你入門,搞清楚 FPGA 編程的基礎概念和實踐方法。

一、FPGA 與 MCU/MPU 的區別 MCU/MPU:順序執行程序,CPU 負責所有邏輯 FPGA:可編程邏輯陣列,邏輯電路可按需求重新配置,實現并行處理 換句話說,FPGA 上的“程序”其實就是邏輯電路的設計。

理解這一點,你就明白為什么 HDL 與傳統 C 語言有本質不同。

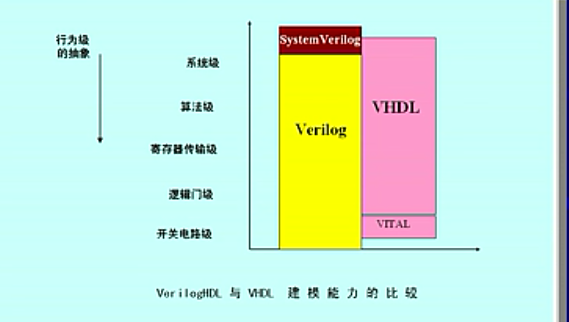

二、Verilog 基礎 Verilog 是一種硬件描述語言,語法上有點像 C,但它描述的是硬件電路。

1. 模塊(module) 模塊是 Verilog 的基本單元,相當于一個功能塊。 module led_blink ( input clk , output reg led ); reg [ 23 : 0 ] counter ; always @( posedge clk ) begin counter <= ?counter? + 1 ; if ( counter? == 24 _000_000 ) begin ? ? ? ? ? ? led? <= ~ led ; ? ? ? ? ? ? counter? <= 0 ; end end endmodule module:定義模塊 input/output:模塊接口 always:時序邏輯塊,觸發條件通常為時鐘上升沿?

2. 數據類型 wire:連線,用于組合邏輯 reg:寄存器,用于時序邏輯 parameter:常量參數

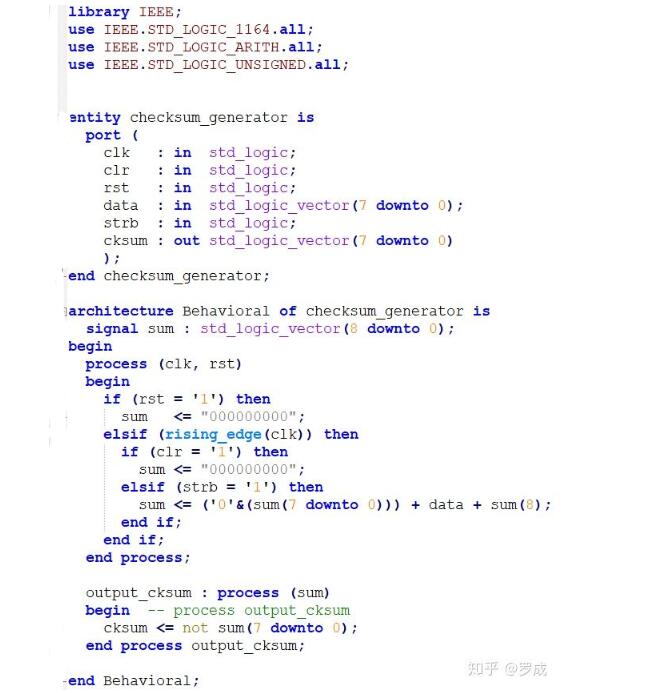

三、VHDL 基礎 VHDL 更像 Ada 或 Pascal,語法更嚴格,但功能同樣強大。

library IEEE ; use IEEE . STD_LOGIC_1164 . ALL ; entity led_blink is Port ( clk : in STD_LOGIC ; led : out STD_LOGIC ); end led_blink ; architecture Behavioral of led_blink is signal counter : integer := 0 ; begin process ( clk ) begin if rising_edge ( clk ) then counter <= ?counter? + 1 ; if ?counter? = 24 _000_000? then ? ? ? ? ? ? ? ? led? <= not ?led ; ? ? ? ? ? ? ? ? counter? <= 0 ; end if ; end if ; end ?process ; end Behavioral ; entity:模塊接口 architecture:模塊內部實現 process:時序邏輯塊?

四、組合邏輯與時序邏輯

組合邏輯:輸出只依賴當前輸入 用assign(Verilog)或with/select(VHDL)實現

示例:加法器、邏輯門 時序邏輯:輸出依賴時鐘和寄存器狀態 用always@(posedge clk)(Verilog)或process(clk)(VHDL)實現 示例:計數器、狀態機

五、FPGA 開發流程簡述 設計 HDL 代碼 編寫 Verilog 或 VHDL 模塊 仿真驗證 用 ModelSim、Vivado Simulator 等工具驗證功能 綜合(Synthesis) 將 HDL 轉化為門級電路 布局布線(Place & Route) 將邏輯映射到 FPGA 物理資源 下載配置 用 JTAG 或 USB 將比特流寫入 FPGA 硬件驗證 測試實際硬件功能是否符合預期

六、小技巧與入門建議 從小模塊開始 LED 燈閃爍、按鍵檢測都是經典練手項目 學會仿真 先在仿真環境跑通邏輯,再上板避免燒 FPGA 注意時鐘域與延遲 時序問題是新手常踩坑點 利用現成 IP 核 Vivado、Quartus 提供豐富 IP,可加快開發

七、結語

FPGA 編程不只是寫代碼,而是設計硬件。

掌握 Verilog 或 VHDL,你就能把自己的想法直接變成電路,讓設備按你的邏輯“動起來”。 入門可以先從簡單 LED 閃爍、按鍵檢測開始,逐步深入到 UART、SPI、PWM 等外設控制,最終掌握復雜的信號處理和嵌入式系統設計。

-

FPGA

+關注

關注

1660文章

22408瀏覽量

636206 -

Verilog

+關注

關注

30文章

1374瀏覽量

114520 -

vhdl

+關注

關注

30文章

822瀏覽量

131680

發布評論請先 登錄

【招聘】verilog vhdl FPGA

Verilog vhdl fpga

FPGA編程是用VHDL還是verilog HDL好用?謝謝了!

關于VHDL和verilog的幾點疑問

FPGA實戰演練邏輯篇4:Verilog與VHDL

有關FPGA開發語言VHDL和Verilog的疑惑

勇敢的芯伴你玩轉Altera FPGA連載4:Verilog與VHDL

Verilog HDL與VHDL及FPGA的比較分析

FPGA視頻教程之學習FPGA選擇verilog還是vhdl詳細資料說明

vhdl轉換為verilog_VHDL和Verilog誰更勝一籌

FPGA編程語言的入門教程

Verilog與VHDL的比較 Verilog HDL編程技巧

為什么我選擇VHDL入門

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

評論