Atmel AT17LV系列FPGA配置EEPROM的全面解析

在FPGA設(shè)計領(lǐng)域,配置存儲器的選擇至關(guān)重要。Atmel的AT17LV系列FPGA配置EEPROM為FPGA提供了一種簡單易用且經(jīng)濟高效的配置解決方案。下面我們就來詳細(xì)了解一下這個系列的產(chǎn)品。

文件下載:AT17LV010-10PU.pdf

一、產(chǎn)品概述

AT17LV系列包括AT17LV65、AT17LV128、AT17LV256、AT17LV512、AT17LV010、AT17LV002和AT17LV040等型號。不過需要注意的是,AT17LV65和AT17LV128不推薦用于新設(shè)計,已被AT17LV256取代。

這些EEPROM專門設(shè)計用于存儲現(xiàn)場可編程門陣列(FPGA)的配置程序,支持3.3V和5.0V的工作電壓應(yīng)用,采用簡單的串行訪問程序來配置一個或多個FPGA設(shè)備。

產(chǎn)品特性

- 多種存儲容量:提供從65,536 x 1-bit到4,194,304 x 1-bit等多種存儲容量選擇,滿足不同F(xiàn)PGA的配置需求。

- 寬電壓支持:支持3.3V和5.0V的工作電壓,增強了產(chǎn)品的通用性。

- 系統(tǒng)內(nèi)可編程(ISP):可通過2線總線進行系統(tǒng)內(nèi)編程,方便快捷。

- 低功耗:采用非常低功耗的CMOS EEPROM工藝,并且具有低功耗待機模式,降低了系統(tǒng)的整體功耗。

- 高可靠性:具有100,000次的寫入周期耐力,工業(yè)級部件在85°C下的數(shù)據(jù)保留時間可達90年。

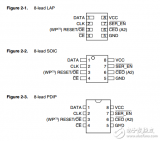

- 多種封裝形式:提供6mm x 6mm x 1mm 8-lead LAP、8-lead PDIP、8-lead SOIC、20-lead PLCC、20-lead SOIC和44-lead TQFP等多種封裝選項,方便不同應(yīng)用場景的使用。

二、引腳配置與描述

引腳描述

| Pin | 描述 |

|---|---|

| DATA | 配置的三態(tài)數(shù)據(jù)輸出。編程時為開漏雙向引腳。 |

| CLK | 時鐘輸入。用于在讀取和編程時遞增內(nèi)部地址和位計數(shù)器。 |

| WP1 | 寫保護(1)。用于在編程期間保護部分內(nèi)存。默認(rèn)情況下,由于內(nèi)部下拉電阻而禁用。在FPGA加載操作期間不使用此輸入引腳。僅在AT17LV512/010/002設(shè)備上可用。 |

| RESET/OE | 當(dāng)SER_EN為高時,為復(fù)位(低電平有效)/輸出使能(高電平有效)。RESET/OE上的低電平會同時復(fù)位地址和位計數(shù)器。高電平(CE為低)會使能數(shù)據(jù)輸出驅(qū)動器。此輸入的邏輯極性可編程為RESET/OE或RESET/OE。對于大多數(shù)應(yīng)用,RESET應(yīng)編程為低電平有效。 |

| WP | 僅在編程期間(SER_EN為低)的寫保護輸入(CE為低時)。當(dāng)WP為低時,整個內(nèi)存可以寫入。當(dāng)WP使能(高)時,內(nèi)存的最低塊不能寫入。僅在AT17LV65、AT17LV128和AT17LV256上可用。 |

| WP2 | 寫保護(2)。用于在編程期間保護部分內(nèi)存。默認(rèn)情況下,由于內(nèi)部下拉電阻而禁用。在FPGA加載操作期間不使用此輸入引腳。僅在AT17LV512/010上可用。 |

| CE | 芯片使能輸入(低電平有效)。低電平(OE為高)允許CLK遞增地址計數(shù)器并使能數(shù)據(jù)輸出驅(qū)動器。CE上的高電平會禁用地址和位計數(shù)器,并使設(shè)備進入低功耗待機模式。請注意,在兩線串行編程模式(SER_EN為低)下,此引腳不會使能/禁用設(shè)備。 |

| GND | 接地。建議在VCC和GND之間使用0.2μF的去耦電容。 |

| CEO | 芯片使能輸出(低電平有效)。當(dāng)?shù)刂酚嫈?shù)器達到其最大值時,此輸出變?yōu)榈碗娖健T贏T17LV設(shè)備的菊花鏈中,一個設(shè)備的CEO引腳必須連接到鏈中下一個設(shè)備的CE輸入。只要CE為低且OE為高,它將保持低電平。然后它將跟隨CE,直到OE變?yōu)榈碗娖剑淮撕螅珻EO將保持高電平,直到再次讀取整個EEPROM。AT17LV65不具備此CEO功能。 |

| A2 | 設(shè)備選擇輸入,A2。用于在編程期間(即SER_EN為低時)使能(或選擇)設(shè)備。A2有一個內(nèi)部下拉電阻。 |

| READY | 開漏復(fù)位狀態(tài)指示器。在加電復(fù)位期間驅(qū)動為低電平,加電完成后釋放。使用此引腳時,建議使用4.7kΩ上拉電阻。 |

| SER_EN | 在FPGA加載操作期間必須保持高電平。將SER_EN拉低可啟用兩線串行編程模式。對于非ISP應(yīng)用,SER_EN應(yīng)連接到VCC。 |

| VCC | 電源。3.3V(±10%)和5.0V(±10%)電源引腳。 |

引腳配置

不同型號的AT17LV設(shè)備在不同封裝下的引腳配置有所不同,具體可參考文檔中的表格。例如,8-lead LAP封裝的AT17LV65/128/256和AT17LV512/010/002/040的引腳配置就存在差異。

三、工作模式

FPGA主串行模式

在主模式下,F(xiàn)PGA會自動從外部存儲器加載配置程序。AT17LV串行配置EEPROM設(shè)計為與主串行模式兼容。大多數(shù)FPGA設(shè)備可以直接控制整個配置過程,并從配置EEPROM中檢索數(shù)據(jù),無需外部智能控制器。

配置控制

- AT17LV配置器的DATA輸出驅(qū)動FPGA設(shè)備的DIN。

- 主FPGA的CCLK輸出驅(qū)動AT17LV配置器的CLK輸入。

- 任何AT17LV配置器的CEO輸出驅(qū)動級聯(lián)EEPROM鏈中下一個配置器的CE輸入。

- SER_EN必須連接到VCC(ISP期間除外)。

- READY引腳可作為設(shè)備復(fù)位狀態(tài)的開漏指示器,在設(shè)備加電復(fù)位周期內(nèi)驅(qū)動為低電平,周期完成后釋放(三態(tài))。

級聯(lián)配置

對于多個FPGA以菊花鏈方式配置或需要更大配置內(nèi)存的FPGA,級聯(lián)配置器可提供額外的內(nèi)存。當(dāng)?shù)谝粋€配置器的最后一位被讀取后,時鐘信號會使該配置器的CEO輸出為低電平,并禁用其DATA線驅(qū)動器。第二個配置器識別到其CE輸入上的低電平后,會使能其DATA輸出。配置完成后,如果每個配置器的RESET/OE被驅(qū)動到其有效(低)電平,則所有級聯(lián)配置器的地址計數(shù)器將被復(fù)位。

復(fù)位極性編程

AT17LV配置器允許用戶將復(fù)位極性編程為RESET/OE或RESET/OE,這一特性得到了行業(yè)標(biāo)準(zhǔn)編程器算法的支持。

編程模式

將SER_EN拉低可進入編程模式。在此模式下,芯片可通過2線串行總線進行編程,編程僅在VCC電源下進行,芯片內(nèi)部會生成編程超電壓。

待機模式

當(dāng)CE被置為高電平時,AT17LV配置器進入低功耗待機模式。在該模式下,AT17LV65、AT17LV128或AT17LV256配置器在3.3V時的電流消耗小于50μA,AT17LV512/010為100μA,AT17LV002/040為200μA。輸出無論OE輸入狀態(tài)如何,都保持高阻抗?fàn)顟B(tài)。

四、電氣規(guī)格

絕對最大額定值

- 工作溫度:-40°C至+85°C

- 存儲溫度:-65°C至+150°C

- 任何引腳相對于地的電壓:-0.1V至VCC + 0.5V

- 電源電壓(VCC):-0.5V至+7.0V

- 最大焊接溫度(10s @ 1/16 in.):260°C

- ESD(RZAP = 1.5K,CZAP = 100pF):2000V

工作條件

| 描述 | 3.3V | 5.0V | 單位 | ||

|---|---|---|---|---|---|

| 最小 | 最大 | 最小 | 最大 | ||

| VCC(工業(yè)級,相對于GND的電源電壓,-40°C至+85°C) | 3.0 | 3.6 | 4.5 | 5.5 | V |

DC特性

不同型號的AT17LV設(shè)備在3.3V和5.0V電源下的DC特性有所不同,包括高電平輸入電壓、低電平輸入電壓、高電平輸出電壓、低電平輸出電壓、電源電流等參數(shù)。

AC特性

在不同電源電壓下,AT17LV設(shè)備的AC特性也有所差異,如OE到數(shù)據(jù)延遲、CE到數(shù)據(jù)延遲、CLK到數(shù)據(jù)延遲等。同時,在級聯(lián)配置時,還有相應(yīng)的AC特性參數(shù)。

熱阻系數(shù)

不同封裝類型的AT17LV設(shè)備具有不同的熱阻系數(shù),這對于散熱設(shè)計非常重要。

五、訂購信息

訂購代碼細(xì)節(jié)

訂購代碼包含了產(chǎn)品的多個信息,如產(chǎn)品系列、設(shè)備密度、封裝選項、特殊引腳配置等。例如,AT17LV256A - 10PU,其中“17LV”表示FPGA EEPROM配置存儲器產(chǎn)品系列,“256”表示設(shè)備密度為256 kilobit,“P”表示8P3(8-lead PDIP)封裝。

具體訂購信息

文檔中提供了不同存儲容量的AT17LV設(shè)備的具體訂購代碼、引腳鍍層、封裝、電壓和工作范圍等信息,方便用戶根據(jù)需求進行選擇。

六、封裝信息

AT17LV系列提供多種封裝形式,每種封裝都有詳細(xì)的尺寸和公差信息,包括8CN4(LAP)、8P3(PDIP)、8S1(SOIC)、20J(PLCC)、20S2(SOIC)和44A(TQFP)等。這些封裝信息對于PCB設(shè)計和布局非常重要。

七、總結(jié)

Atmel的AT17LV系列FPGA配置EEPROM以其豐富的特性、多種封裝選項和良好的電氣性能,為FPGA設(shè)計提供了可靠的配置解決方案。在實際應(yīng)用中,工程師需要根據(jù)具體的FPGA需求、系統(tǒng)電壓、存儲容量等因素來選擇合適的型號和封裝。同時,在設(shè)計過程中,要嚴(yán)格遵循電氣規(guī)格和引腳配置要求,以確保系統(tǒng)的穩(wěn)定性和可靠性。你在使用AT17LV系列產(chǎn)品時遇到過哪些問題呢?歡迎在評論區(qū)分享你的經(jīng)驗和見解。

-

EEPROM

+關(guān)注

關(guān)注

9文章

1143瀏覽量

86209 -

FPGA配置

+關(guān)注

關(guān)注

0文章

4瀏覽量

6294

發(fā)布評論請先 登錄

FPGA芯片配置方式及常見配置方法

有嵌入式EEPROM的FPGA系列嗎?

AT17A系列FPGA配置EEPROM替代Altera EP

FPGA配置EEPROM存儲器at17lv010

FPGA芯片配置分類及配置方式

FPGA數(shù)據(jù)配置模式解析

玩轉(zhuǎn)EEPROM——全面指南

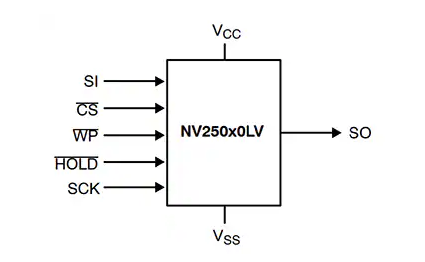

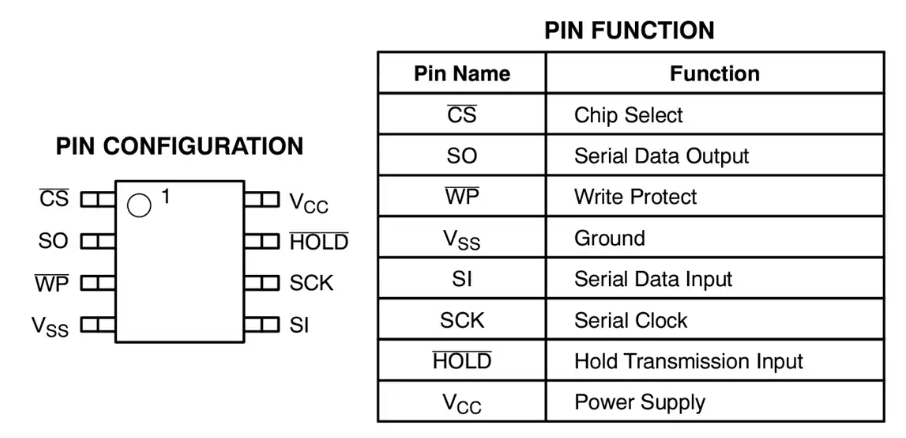

基于onsemi NV250x0LV系列EEPROM數(shù)據(jù)手冊的技術(shù)解析與應(yīng)用指南

探索onsemi EEPROM:NV25080LV系列的卓越性能與應(yīng)用指南

Atmel AT17LV系列FPGA配置EEPROM的全面解析

Atmel AT17LV系列FPGA配置EEPROM的全面解析

評論