3D NAND閃存高密度技術(shù)正變得越來越激進(jìn)。3D NAND閃存密度和容量的提高主要通過增加垂直方向上堆疊的存儲(chǔ)器單元的數(shù)量來實(shí)現(xiàn)。通過這種三維堆疊技術(shù)和多值存儲(chǔ)技術(shù)(用于在一個(gè)存儲(chǔ)單元中存儲(chǔ)多個(gè)比特位的技術(shù)),實(shí)現(xiàn)了具有極大存儲(chǔ)容量的硅芯片。

目前,最先進(jìn)的3D NAND閃存可在單個(gè)硅片上容納高達(dá)1Tbit或1.33Tbit的數(shù)據(jù)。

譬如,英特爾(Intel)和美光科技(Micron)的開發(fā)聯(lián)盟和三星電子各自將制造技術(shù)與64層堆棧和QLC(四層單元)技術(shù)相結(jié)合,該技術(shù)將4位數(shù)據(jù)存儲(chǔ)在一個(gè)存儲(chǔ)單元中。因此,實(shí)現(xiàn)了1Tbit存儲(chǔ)容量。

東芝存儲(chǔ)和西部數(shù)據(jù)公司(Western Digital)通過將QLC技術(shù)與制造技術(shù)相結(jié)合,堆疊了96層,開發(fā)出具有1.33 Tbit的高容量硅芯片。1.33 Tbit是目前世界上最大的半導(dǎo)體存儲(chǔ)器存儲(chǔ)容量。

還開發(fā)了128層堆疊的3D NAND閃存。2019年6月,SK海力士將128層制造技術(shù)與TLC(三層單元)技術(shù)相結(jié)合,將3位數(shù)據(jù)存儲(chǔ)在一個(gè)存儲(chǔ)單元中,從而實(shí)現(xiàn)每個(gè)硅片的3D存儲(chǔ)容量。采用TLC堆疊方式使得3D閃存具有更高的存儲(chǔ)容量。

在過去的20年中,內(nèi)存容量增加了1,000倍

回顧過去,傳統(tǒng)的2D NAND閃存主要通過小型化將其存儲(chǔ)容量擴(kuò)展到128Gbit。MLC技術(shù)和TLC技術(shù)用于多級(jí)存儲(chǔ)。

3D NAND閃存技術(shù)的實(shí)際應(yīng)用始于128Gbit,256Gbit或更高的存儲(chǔ)容量成為3D NAND技術(shù)的主導(dǎo)地位。多級(jí)存儲(chǔ)系統(tǒng)已通過TLC技術(shù)和QLC技術(shù)投入實(shí)際應(yīng)用。

自2001年以來,NAND閃存的存儲(chǔ)密度(每硅片存儲(chǔ)容量)一直以每年1.41倍的速度增長。這相當(dāng)于三年內(nèi)存儲(chǔ)容量增加了四倍。令人驚訝的是,這種高速度持續(xù)了19年。

然而,現(xiàn)在人們都在關(guān)注3D NAND閃存的未來,半導(dǎo)體存儲(chǔ)研發(fā)界已經(jīng)聽說過。主要有兩個(gè)問題。

一個(gè)是堆疊層數(shù)量的增加來提高容量,這種方式將在不久的未來減緩或達(dá)到極限。另一個(gè)是多級(jí)存儲(chǔ)技術(shù)將通過QLC方法達(dá)到極限,并且每個(gè)存儲(chǔ)器單元的位數(shù)不能增加。

三星正式提到超過300個(gè)3D NAND閃存

然而,8月6日,主要的NAND供應(yīng)商宣布了一系列路線圖和技術(shù)來克服這些問題。

存儲(chǔ)制造商三星電子于6月6日宣布,它將開始批量生產(chǎn)配備256Gbit 3D NAND閃存的SSD,在單個(gè)堆棧中有136層內(nèi)存通孔。136層內(nèi)存通孔是有史以來最大的層數(shù)。除了源極線和偽字線之外,存儲(chǔ)器單元串中的字線層的數(shù)量似乎是110到120。

值得一提的是,通過堆疊三個(gè)136層的單個(gè)堆疊,可以堆疊超過300個(gè)存儲(chǔ)器單元。三星表達(dá)如此樂觀的看法是很不尋常的。

300層的開發(fā)日期尚未公布,但研究已經(jīng)開始。

堆疊字線數(shù)量的路線圖

東芝內(nèi)存已經(jīng)提到了過去通過存儲(chǔ)器通孔技術(shù)堆疊字線數(shù)量的可能性。2017年5月,IMW表示可以用200層實(shí)現(xiàn)2Tbit/die。截至2017年5月,3D NAND閃存技術(shù)字線堆棧的最大數(shù)量為64。

然而,在2018年8月,閃存行業(yè)盛會(huì)“閃存峰會(huì)(FMS)”中,SK海力士表示200層級(jí)是一個(gè)傳遞點(diǎn),最終可以實(shí)現(xiàn)500層級(jí)。

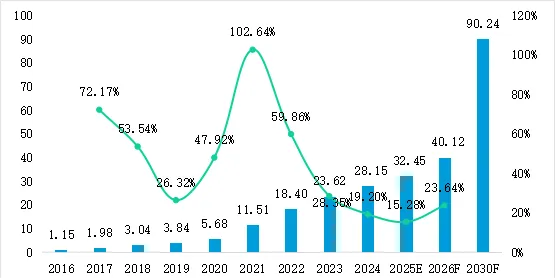

2019年8月6日,SK海力士在FMS國際閃存會(huì)議上公布了其閃存路線圖,預(yù)計(jì)2020年推出176層的閃存,2025年500層,2030年800+層。800層原則上是可以實(shí)現(xiàn)8Tbit/die的層數(shù)。單個(gè)裸片就是1TB。

圖1:SK海力士NAND產(chǎn)品發(fā)展路線圖

多級(jí)存儲(chǔ)器最終達(dá)到5bit/cell

在當(dāng)天的FMS會(huì)上,讓人驚訝的是,東芝存儲(chǔ)也宣布了兩項(xiàng)基本技術(shù)來提高3D NAND閃存的存儲(chǔ)密度。

圖2:通過東芝存儲(chǔ)的QLC(4位/單元)技術(shù)分配閾值電壓。

一種是多值存儲(chǔ)技術(shù)。該公司宣布將開發(fā)“PLC技術(shù)”,將5位數(shù)據(jù)存儲(chǔ)在一個(gè)存儲(chǔ)單元中。這聽起來是一個(gè)令在場聽眾超級(jí)震驚的消息。

圖3:東芝存儲(chǔ)公司推出的PLC(5位/單元)技術(shù)的閾值電壓分布。

傳統(tǒng)的多級(jí)存儲(chǔ)系統(tǒng)通常是QLC(四級(jí)單元)技術(shù),其將4位數(shù)據(jù)存儲(chǔ)在一個(gè)存儲(chǔ)器單元中。在QLC技術(shù)中,在一個(gè)存儲(chǔ)器單元中寫入15級(jí)的閾值電壓。相鄰閾值電壓之間的差異很小并且調(diào)整非常困難。因此,QLC技術(shù)被認(rèn)為是多級(jí)存儲(chǔ)的限制。

然而,東芝存儲(chǔ)已經(jīng)打破了這種信念。他們已經(jīng)展示了當(dāng)在一個(gè)存儲(chǔ)器單元中寫入31個(gè)閾值電壓時(shí)的實(shí)驗(yàn)結(jié)果。東芝聯(lián)合開發(fā)合作伙伴Western Digital也展示了一個(gè)包含5位/單元的多級(jí)內(nèi)存。順便說一句,將QLC更改為PLC會(huì)使內(nèi)存密度增加25%。

圖4:Western Digital的多級(jí)存儲(chǔ)方法解釋幻燈片。

雙倍內(nèi)存密度的終極方法

另一種技術(shù)是通過將存儲(chǔ)器單元的字線分成兩半來將每個(gè)存儲(chǔ)器通孔的存儲(chǔ)器單元數(shù)量加倍。盡管很難制造,但存在原則上存儲(chǔ)密度加倍的優(yōu)勢。

東芝存儲(chǔ)展示了電荷陷阱(CT)單元和浮柵(FG)單元的橫截面觀察圖像,其中字線被分成兩半。

圖5:通過將存儲(chǔ)器單元字線分成兩半來將存儲(chǔ)器密度加倍。左邊是概念。右邊是原型單元結(jié)構(gòu)和橫截面觀察圖像。

3D NAND閃存主要供應(yīng)商開發(fā)的意愿似乎根本沒有削弱。毫無疑問,超高層,多值存儲(chǔ)和存儲(chǔ)器單元?jiǎng)澐质菢O其困難的技術(shù)。不過,可以說這個(gè)行業(yè)別無選擇,只能去做。

-

存儲(chǔ)

+關(guān)注

關(guān)注

13文章

4868瀏覽量

90218 -

內(nèi)存

+關(guān)注

關(guān)注

9文章

3223瀏覽量

76468 -

3D NAND閃存

+關(guān)注

關(guān)注

0文章

5瀏覽量

4848

發(fā)布評(píng)論請先 登錄

簡單認(rèn)識(shí)3D SOI集成電路技術(shù)

探索TLE493D-P3XX-MS2GO 3D 2Go套件:開啟3D磁傳感器評(píng)估之旅

半導(dǎo)體“HBM和3D Stacked Memory”技術(shù)的詳解

技術(shù)資訊 I 圖文詳解 Allegro X PCB Designer 中的 3D 模型映射

玩轉(zhuǎn) KiCad 3D模型的使用

iTOF技術(shù),多樣化的3D視覺應(yīng)用

索尼與VAST達(dá)成3D業(yè)務(wù)合作

如何提高3D成像設(shè)備的部署和設(shè)計(jì)優(yōu)勢

3D打印能用哪些材質(zhì)?

SK海力士321層4D NAND的誕生

【Milk-V Duo S 開發(fā)板免費(fèi)體驗(yàn)】3- 嘗試免費(fèi)3D打印了開發(fā)板外殼

3D視覺引領(lǐng)工業(yè)變革

英倫科技10.1英寸裸眼3D數(shù)碼相框升級(jí)了,玩轉(zhuǎn)AI文生圖太cool了!

賦能個(gè)性化表達(dá)!eSUN易生3D打印材料在時(shí)尚設(shè)計(jì)領(lǐng)域的應(yīng)用

3D NAND開發(fā)競爭加劇 “5bit/cell”技術(shù)也出現(xiàn)了

3D NAND開發(fā)競爭加劇 “5bit/cell”技術(shù)也出現(xiàn)了

評(píng)論