在工藝節(jié)點進入了28nm之后,因為受限于硅材料本身的特性,晶圓廠和芯片廠如果還想通過晶體管微縮,將芯片性能按照之前的步伐提升,這是基本不可能的,為此各大廠商現(xiàn)在都開始探索從封裝上入手去提升性能,臺積電是當(dāng)中的一個先驅(qū)。

首先,打入眾多客戶內(nèi)部的臺積電Bumping服務(wù)是臺積電封裝業(yè)務(wù)的一個基本以來。據(jù)介紹,超過90%的7nm客戶都選擇了臺積電的bumping服務(wù)。

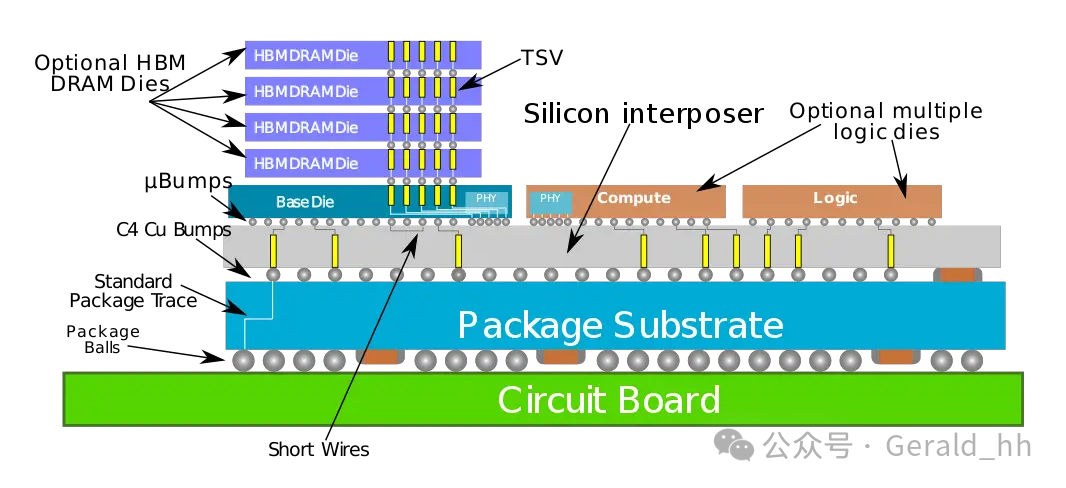

其次就是Cowos業(yè)務(wù)。八年前。在臺積電2011 年第三季法說會上,臺積電創(chuàng)始人張忠謀毫無預(yù)兆擲出重磅炸彈──臺積電要進軍封裝領(lǐng)域。他們推出的第一個先進封裝產(chǎn)品是CoWoS(Chip on Wafer on Substrate)。意思就是將邏輯芯片和DRAM 放在硅中介層(interposer)上,然后封裝在基板上。

據(jù)介紹,自推出以來,臺積電COWOS封裝技術(shù)獲得了超過50個客戶的選用,公司在這個封裝技術(shù)上也獲得了業(yè)界最高的良率。在他們看來,COWOS將會在未來越來越重要,市場需求也會逐漸提升,臺積電也會從各個角度來優(yōu)化,簡化客戶COWOS設(shè)計流程,加快產(chǎn)品的上市速度。

這個封裝技術(shù)也能為創(chuàng)新提供各種各樣的支持。

除了bumping 和COWOS之外,InFO(Integrated Fan-Out)也是臺積電封裝武器庫里的另一個殺手锏。所謂InFO,就是整合型扇出技術(shù)。這是一項非穿孔技術(shù),是專為如移動及消費性產(chǎn)品等對成本敏感的應(yīng)用開發(fā)出來的封裝技術(shù)。

據(jù)介紹,這種技術(shù)分為三類:一種是InFO_oS(Integrated Fan-Out on substrate),另一種是InFO_mS( Integrated Fan-Out memory on substrate),還有一種是InFO_POP.

此外,臺積電還推出了另類的InFO工藝SoW(System on Wafer)。

臺積電方面表示,這兩個封裝技術(shù)將會在公司的先進封裝布局中扮演重要角色,也能夠為AI、服務(wù)器、網(wǎng)絡(luò)、AI推理和移動等芯片提供全方位的支持。

根據(jù)臺積電的劃分,以上幾種屬于他們的后段3D封裝。為了進一步推動芯片性能的提升,臺積電也推出了前道3D封裝工藝SOIC(system-on-integrated-chips)和全新的多晶圓堆疊(WoW,Wafer-on- Wafer)。

臺積電方面進一步表示,通過后段3D封裝的后果是獲得了一個可以直接使用的芯片,而使用前道封裝獲得了則只是一個異構(gòu)芯片,還需要我們進行封裝才能獲得可用的芯片。

所謂SoIC是一種創(chuàng)新的多芯片堆棧技術(shù),能對10納米以下的制程進行晶圓級的接合技術(shù)。該技術(shù)沒有突起的鍵合結(jié)構(gòu),因此有更佳運作的性能。

具有革命性意義的工藝技術(shù)Wafer-on-Wafer (WoW,堆疊晶圓),就像是3D NAND閃存多層堆疊一樣,將兩層Die以鏡像方式垂直堆疊起來,有望用于生產(chǎn)顯卡GPU,創(chuàng)造出晶體管規(guī)模更大的GPU。據(jù)介紹,WoW技術(shù)通過10μm的硅穿孔方式連接上下兩塊die,這樣一來可以在垂直方向上堆疊更多die,也意味著die之間的延遲通信極大地減少,引入更多的核心。

-

臺積電

+關(guān)注

關(guān)注

44文章

5803瀏覽量

176387 -

CoWoS

+關(guān)注

關(guān)注

0文章

169瀏覽量

11507

原文標(biāo)題:傳感器專業(yè)微信群,趕緊加入吧!

文章出處:【微信號:WW_CGQJS,微信公眾號:傳感器技術(shù)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

高通MWC2026全棧出擊:從5G-A到AI原生6G布局,硬核產(chǎn)品震撼亮相

【深度報告】CoWoS封裝的中階層是關(guān)鍵——SiC材料

先進封裝市場迎來EMIB與CoWoS的格局之爭

CoWoS產(chǎn)能狂飆的背后:異質(zhì)集成芯片的“最終測試”新范式

臺積電CoWoS技術(shù)的基本原理

絲桿模組從結(jié)構(gòu)到應(yīng)用,有哪些核心類型?

HBM技術(shù)在CowoS封裝中的應(yīng)用

TP-LINK技術(shù)解析:從路由器巨頭到Wi-Fi 7布局

CoWoP能否挑戰(zhàn)CoWoS的霸主地位

從InFO-MS到InFO_SoW的先進封裝技術(shù)

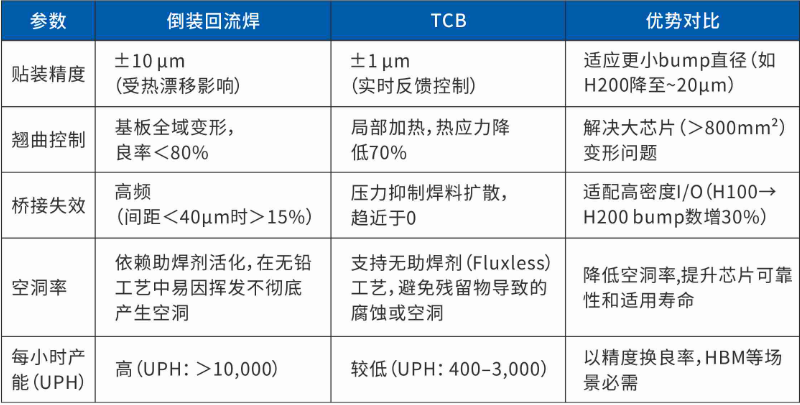

普萊信成立TCB實驗室,提供CoWoS、HBM、CPO、oDSP等從打樣到量產(chǎn)的支持

HarmonyOS NEXT應(yīng)用元服務(wù)布局合理使用布局組件

從選型到布局:MDDTVS二極管在ESD防護中的工程實戰(zhàn)指南

TSMC:從COWOS到WOW的布局

TSMC:從COWOS到WOW的布局

評論