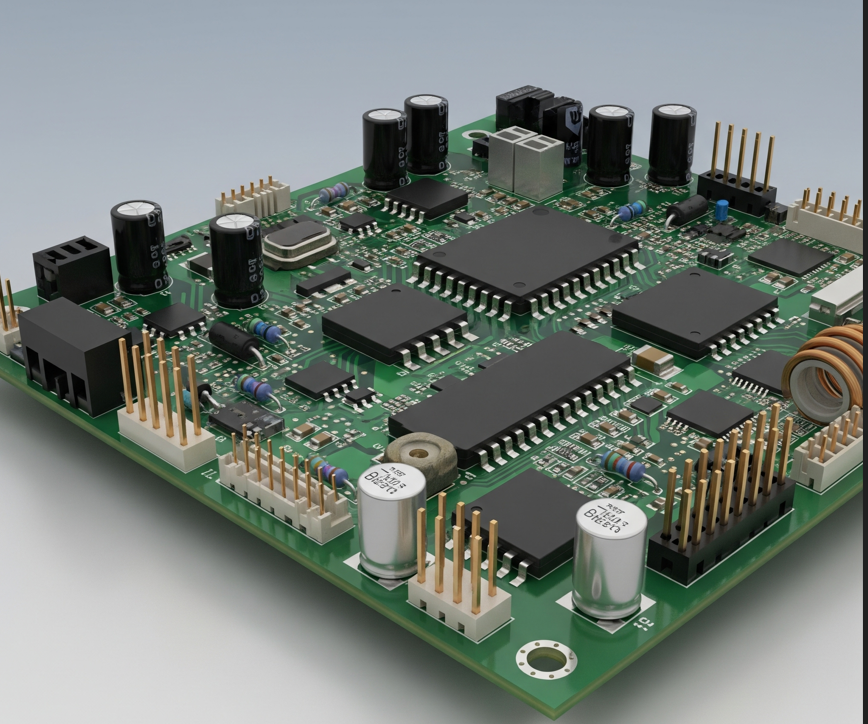

最新的電子產(chǎn)品通常需要三個獨(dú)立的設(shè)計(jì)流程 - 芯片,封裝和PCB - 這些產(chǎn)品在單個封裝中使用越來越復(fù)雜的片上系統(tǒng)(SoC)和多個芯片。今天,這三個過程通常使用點(diǎn)工具執(zhí)行,這些點(diǎn)工具需要耗時(shí)且容易出錯的手動過程來鏈接這三個過程。但是,通過考慮每個設(shè)計(jì)決策的系統(tǒng)級影響,集成的3D芯片/封裝/電路板協(xié)同設(shè)計(jì)環(huán)境能夠以比過去更大的程度全面優(yōu)化封裝,電路板和IC設(shè)計(jì)。設(shè)計(jì)人員可以通過引腳分配和I/O布局優(yōu)化可路由性,以最大限度地減少封裝,芯片和電路板之間的層數(shù)。新方法可以在更短的時(shí)間內(nèi)將更多功能性,更高性能和更便宜的產(chǎn)品推向市場。

限制傳統(tǒng)的設(shè)計(jì)方法

傳統(tǒng)的系統(tǒng)設(shè)計(jì)依賴于在獨(dú)立環(huán)境中處理IC,封裝和PCB的工具。這些流程缺乏系統(tǒng)級規(guī)劃,可視化,設(shè)計(jì)和分析。規(guī)劃中使用的設(shè)計(jì)數(shù)據(jù)庫不能與用于審查和分析的數(shù)據(jù)庫互操作,因此很難保證在規(guī)劃期間做出的決策能夠貫穿最終產(chǎn)品。在傳統(tǒng)的2D組件專用設(shè)計(jì)工具中,協(xié)同設(shè)計(jì)具有挑戰(zhàn)性,因?yàn)樵O(shè)計(jì)人員通常只能看到自己的組件。用于在這些環(huán)境之間交換數(shù)據(jù)的文件交換格式通常是過時(shí)的和缺陷的,缺少有用的設(shè)計(jì)數(shù)據(jù)或者是專有的并且沒有廣泛支持。傳統(tǒng)流程中不存在工具來集成系統(tǒng)的所有組件并維護(hù)電氣和機(jī)械數(shù)據(jù)庫信息,從而提供可實(shí)現(xiàn)的協(xié)同設(shè)計(jì)環(huán)境。

過去這種方法是可以接受的,因?yàn)榇蠖鄶?shù)復(fù)雜的系統(tǒng)都有大的外形(服務(wù)器,PC塔,大型機(jī)械),封裝和基板成本在整個系統(tǒng)成本中可以忽略不計(jì)。隨著功能的增加,成本的限制以及當(dāng)今產(chǎn)品(便攜式設(shè)備,可穿戴設(shè)備和汽車)的外形尺寸的減小,組件需要彼此緊密協(xié)調(diào),以便針對小尺寸和最小層數(shù)基板優(yōu)化引腳分配。/p>

由于缺乏工具集成,但設(shè)計(jì)要求不斷增加,公司已恢復(fù)使用電子表格和通用辦公生產(chǎn)力工具來執(zhí)行規(guī)劃和可行性研究以及定義工具界面和數(shù)據(jù)傳輸?shù)茸兺ǚ椒ā_@些文件通常是內(nèi)部開發(fā)的,必須在內(nèi)部進(jìn)行維護(hù)并手動操作以與流程中的工具進(jìn)行交互。由于EDA工具的限制性文件輸入格式,它們受到所提供信息的限制。它們會遇到諸如無法與最終設(shè)計(jì)輸出數(shù)據(jù)自動關(guān)聯(lián)的設(shè)計(jì)規(guī)劃數(shù)據(jù)以及僅限于簡單信息(如基本網(wǎng)絡(luò)和位置信息)的引腳分配數(shù)據(jù)等問題。由于缺乏中央設(shè)計(jì)環(huán)境以及對系統(tǒng)數(shù)據(jù)使用手動反饋機(jī)制,引腳,I/O,布局布線的元件間優(yōu)化是不可行的。

PCB產(chǎn)品設(shè)計(jì)供應(yīng)商已開始介紹利用傳統(tǒng)數(shù)據(jù)庫來降低開發(fā)成本的工具來應(yīng)對這些挑戰(zhàn)。然而,由于傳統(tǒng)數(shù)據(jù)庫結(jié)構(gòu)所施加的不靈活性,這些新工具僅限于2D環(huán)境或一個封裝和一個PCB。需要在2D和3D視圖之間來回切換需要在傳統(tǒng)2D設(shè)計(jì)數(shù)據(jù)庫和較新的3D查看器數(shù)據(jù)庫之間進(jìn)行文件轉(zhuǎn)換,這會減慢設(shè)計(jì)過程,增加翻譯準(zhǔn)確度的不確定性并限制設(shè)計(jì)洞察力。

隨著產(chǎn)品外形尺寸的縮小,需要使用機(jī)械設(shè)計(jì)的外殼檢查ECAD設(shè)計(jì)尺寸,并考慮外殼進(jìn)行多物理分析。隨著外殼越來越多地從正交移動到更緊湊,更復(fù)雜的彎曲形狀,需要3D視圖,因?yàn)?D視圖過于嚴(yán)格并且不能準(zhǔn)確地表示系統(tǒng)。傳統(tǒng)流程將ECAD和MCAD設(shè)計(jì)分開,幾乎沒有交叉流分析的機(jī)會。 MCAD流程中的電子行業(yè)特定設(shè)計(jì)自動化由于其通用性而難以實(shí)現(xiàn)。

系統(tǒng)級3D協(xié)同設(shè)計(jì)的出現(xiàn)

新一代系統(tǒng)級3D協(xié)同設(shè)計(jì)工具通過提供集成的系統(tǒng)設(shè)計(jì)環(huán)境來應(yīng)對這些挑戰(zhàn)系統(tǒng)級以及PCB,IC和機(jī)械外殼的規(guī)劃和最終設(shè)計(jì)。這些數(shù)據(jù)庫被放在一個視圖中,因此每個參與項(xiàng)目的人都可以在完整產(chǎn)品的上下文中看到他們的謎題。工程師可以在單個用戶界面中進(jìn)行系統(tǒng)級設(shè)計(jì),完整封裝設(shè)計(jì),完整PCB設(shè)計(jì),插入器設(shè)計(jì),并優(yōu)化ICL設(shè)計(jì)的RDL(再分布層)布線和裸片放置。可以根據(jù)最終的ECAD外形尺寸(PCB,封裝和IC)尺寸檢查機(jī)械外殼設(shè)計(jì),以確保安裝和間隙。集成的制造設(shè)計(jì)工具使得可以在布局期間驗(yàn)證設(shè)計(jì)到供應(yīng)商技術(shù)特定的制造和裝配制造檢查。可以自動生成文檔以進(jìn)行簽核和制造。與多物理分析工具集成的按鈕確保設(shè)計(jì)數(shù)據(jù)的高效快速傳輸,實(shí)現(xiàn)快速周轉(zhuǎn)。

Co - 使用RDL和封裝扇出逃生路由設(shè)計(jì)IC和封裝

這種集成的協(xié)同設(shè)計(jì)環(huán)境允許在離散或有限的2D工具中無法使用獨(dú)特的設(shè)計(jì)方法。例如,工程師可以在單一設(shè)計(jì)視圖中考慮IC側(cè)的RDL和PCB側(cè)的逃逸路徑,對不同數(shù)量的封裝層進(jìn)行可行性研究。能夠?qū)π酒头庋b進(jìn)行系統(tǒng)級協(xié)同設(shè)計(jì),可以優(yōu)化凸點(diǎn)和焊球布局,I/O布局和引腳分配,從而降低芯片,封裝和PCB層數(shù),即使在具有布線復(fù)雜性的非傳統(tǒng)結(jié)構(gòu)中也是如此在垂直方向上,如PoP,SiP,芯片級封裝和3DIC/3D封裝。芯片RDL和封裝逃逸的自動布線允許快速尋路可行性,改善完成時(shí)間并允許用戶優(yōu)化裸片放置。其優(yōu)勢包括減少RDL,插入器/基板和封裝層數(shù)量,同時(shí)優(yōu)化信號性能并縮短出帶時(shí)間。

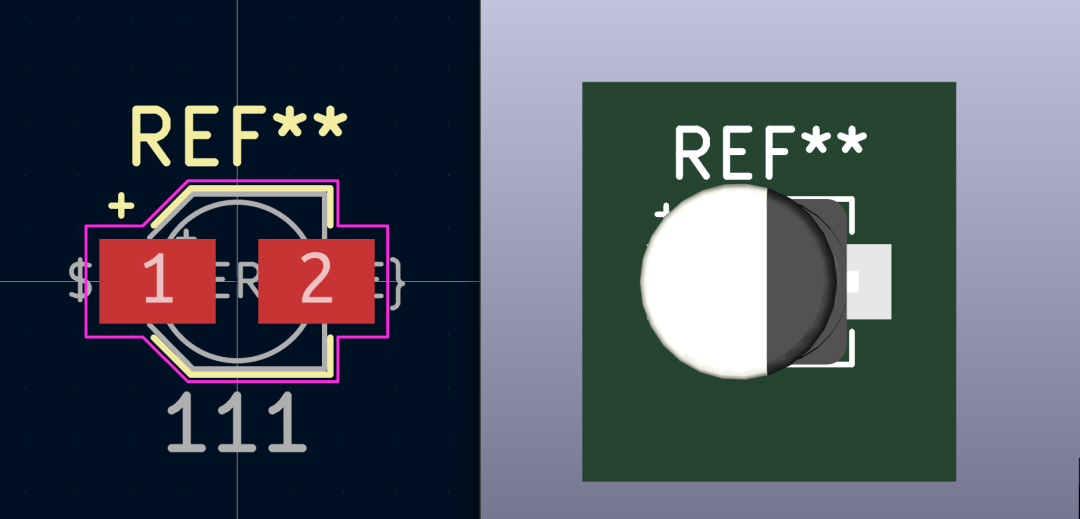

PCB設(shè)計(jì)(頂部)和封裝設(shè)計(jì)(底部)之間的實(shí)時(shí)交換,以提高可布線性和性能

查看IC,封裝和PCB同時(shí)在一個視圖中幫助工程師優(yōu)化引腳分配并避免連接錯誤,從而縮短設(shè)計(jì)時(shí)間。如果設(shè)計(jì)人員需要執(zhí)行封裝/IC凸點(diǎn)分配,他或她可以在PCB級別查看對鼠巢的影響。或者,如果設(shè)計(jì)人員必須在電路板級進(jìn)行自動或交互式引腳交換以提高PCB布線性,他或她可以觀察封裝和IC級別的潛在影響。引腳交換操作在封裝和PCB數(shù)據(jù)庫之間自動傳遞,無需CSV或其他中性文件來傳達(dá)更改。該工具還允許多個工程師在單個基板上工作,同時(shí)保護(hù)其他工程師的編輯。如果設(shè)計(jì)人員需要在鎖定的包裝設(shè)計(jì)中進(jìn)行引腳交換,他或她可以發(fā)送通知,其他工程師可以接受或拒絕作為ECO。

智能PoP和SiP設(shè)計(jì)

使用該技術(shù),可以將多個IC導(dǎo)入?yún)f(xié)同設(shè)計(jì)環(huán)境并連接在一起。 3D,多設(shè)計(jì)環(huán)境更智能地管理復(fù)雜包(如PoP和SiP)的路由相互依賴性。這種新方法通過實(shí)時(shí)3D設(shè)計(jì)為SiP提供重點(diǎn)設(shè)計(jì)規(guī)則檢查,并支持堆疊LSI的復(fù)雜鍵合線放置。工程師可以使用共同設(shè)計(jì)環(huán)境來確保鍵合線在任何角度滿足間距要求,并且3D鍵合線輪廓符合制造規(guī)范。

使用TSV管理復(fù)雜的2.5/3D IC設(shè)計(jì)

這種新方法極大地改善了基于TSV的設(shè)計(jì)(如3DIC)的布局規(guī)劃和布線堆疊芯片和硅中介層。工程師可以導(dǎo)入現(xiàn)有數(shù)據(jù)庫(來自O(shè)penAccess,GDS或LEF/DEF文件)或使用設(shè)計(jì)環(huán)境生成TSV。可以使用導(dǎo)入或手動生成的制造和設(shè)計(jì)規(guī)則來執(zhí)行自動或手動路由。預(yù)放置的TSV可以自動布線,而未放置的TSV可以放置和布線。 3D環(huán)境支持大型數(shù)據(jù)集,并允許設(shè)計(jì)人員查看復(fù)雜的轉(zhuǎn)義和路由結(jié)構(gòu)

通過集成信號和電源完整性分析驗(yàn)證信號性能

隨著系統(tǒng)任何級別的變化,設(shè)計(jì)人員可以從信號完整性,電源完整性或散熱角度查看效果。多學(xué)科,多物理分析可以使用Keysight Technologies,ANSYS,AWR,CST和Synopsys等解決方案提供商提供的一流解決方案。協(xié)同設(shè)計(jì)環(huán)境可在整個系統(tǒng)中實(shí)現(xiàn)信號可追溯性。可以檢查和分析信號路徑,因?yàn)樗鼈兛缭皆O(shè)計(jì)和組件邊界,從驅(qū)動器到系統(tǒng)互連到接收器。智能和集成的基于原理圖或布局的仿真環(huán)境支持多種設(shè)計(jì)流程。

結(jié)論

芯片/封裝/電路板協(xié)同設(shè)計(jì)提供了統(tǒng)一的設(shè)計(jì)方法,使設(shè)計(jì)人員能夠考慮每個設(shè)計(jì)決策的系統(tǒng)級影響,從而降低設(shè)計(jì)成本,提高性能,減少不確定性并加快進(jìn)度。設(shè)計(jì)人員可以同時(shí)考慮IC/封裝/PCB問題,以設(shè)計(jì)具有最佳信號性能的良好集成產(chǎn)品,同時(shí)減少RDL,插入器/基板和封裝層數(shù)量,從而降低成本和出帶時(shí)間。

-

PCB打樣

+關(guān)注

關(guān)注

17文章

2981瀏覽量

23601 -

華強(qiáng)PCB

+關(guān)注

關(guān)注

8文章

1831瀏覽量

29264 -

華強(qiáng)pcb線路板打樣

+關(guān)注

關(guān)注

5文章

14629瀏覽量

44647

發(fā)布評論請先 登錄

3D打印機(jī)散熱風(fēng)扇:熱管理核心與選型優(yōu)化指南

2D、2.5D與3D封裝技術(shù)的區(qū)別與應(yīng)用解析

淺談2D封裝,2.5D封裝,3D封裝各有什么區(qū)別?

技術(shù)資訊 I 多板系統(tǒng) 3D 建模,提升設(shè)計(jì)精度和性能

技術(shù)資訊 I 圖文詳解 Allegro X PCB Designer 中的 3D 模型映射

【海翔科技】玻璃晶圓 TTV 厚度對 3D 集成封裝可靠性的影響評估

Socionext推出3D芯片堆疊與5.5D封裝技術(shù)

玩轉(zhuǎn) KiCad 3D模型的使用

3D封裝的優(yōu)勢、結(jié)構(gòu)類型與特點(diǎn)

華大九天推出芯粒(Chiplet)與2.5D/3D先進(jìn)封裝版圖設(shè)計(jì)解決方案Empyrean Storm

文件嵌入詳解(一):在PCB封裝庫中嵌入3D模型

3D封裝與系統(tǒng)級封裝的背景體系解析介紹

3D芯片/封裝/ PCB協(xié)同設(shè)計(jì)優(yōu)化系統(tǒng)怎樣操作

3D芯片/封裝/ PCB協(xié)同設(shè)計(jì)優(yōu)化系統(tǒng)怎樣操作

評論