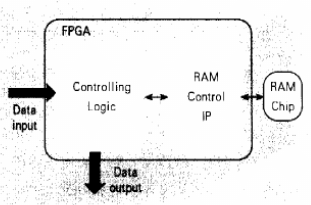

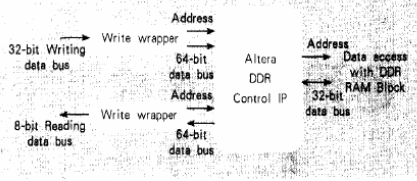

1. 背景 這篇文章主要介紹了DDR3IP核的寫實現。 2. 寫命令和數據總線介紹 DDR3 SDRAM控制器IP核主要預留了兩組總線,一組可以直接綁定到DDR3 SDRAM芯片端口,一組是留給

2020-12-31 11:17:02 6783

6783

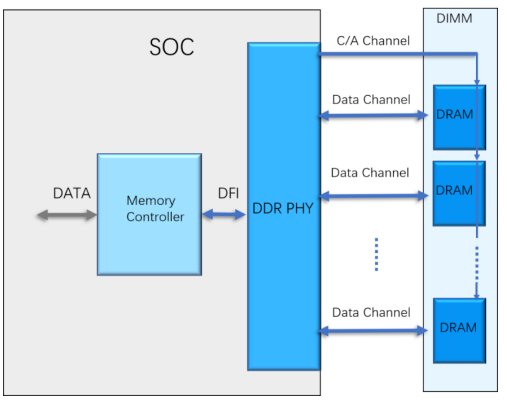

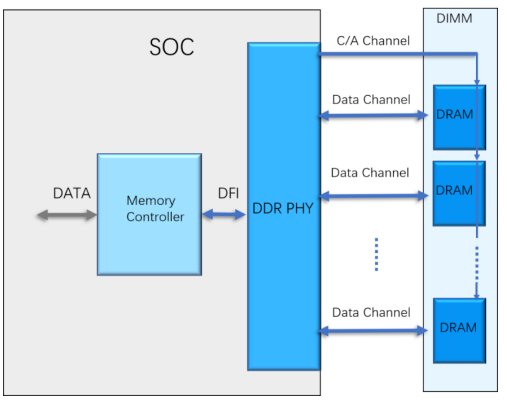

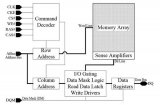

DDR PHY是DRAM和內存控制器通信的橋梁,它負責把內存控制器發過來的數據轉換成符合DDR協議的信號,并發送到DRAM。

2021-04-20 11:37:25 5307

5307

DDR內存控制器是一個高度集成的組件,支持多種DDR內存類型(DDR2、DDR3、DDR3L、LPDDR2),并通過精心設計的架構來優化內存訪問效率。

2025-03-05 13:47:40 3578

3578

完全可以用靠近輸入輸出引腳處的邏輯資源來實現DDR觸發器,而且最后的結果表明,這種實現方式可以滿足時序要求。 從圖4中也可以看到,控制器內部有兩個時鐘,clk和clk_90,兩者之間的相位差為90°。圖中

2018-12-18 10:17:15

交叉存取來提高帶寬。一個易于使用和可預測的存儲器控制器,如:ECP3 DDR3存儲器控制器,在用戶基于其對數據處理的基本算法的了解的情況下來分配存儲器緩沖區時,可以最小的硬件和軟件開銷來實現最大的帶寬

2019-05-24 05:00:34

小,256Kb-16Mb 5.集成度低,單位容量價格高 6.靜態功耗低,運行功耗大 DRAM 1.速度較慢 2.需要刷新來保持數據 3.需要MCU帶外部存儲控制器 4.容量大,16Mb-4Gb 5.集成度高,單位容量價格低 6.運行功耗低

2020-12-10 15:49:11

圍設備。外圍設備連接的引腳連接到微型計算機功能,稱為輸入/輸出端口(I/O端口)。端口是微型計算機和外圍設備連接的端子。如果您想從微型計算機打開/關閉LED,您可以通過執行程序中的端口控制來實現。端口

2021-09-10 09:14:16

6655時鐘PLL配置與DDR3的配置1 時鐘概述PLL與PLL控制器的邏輯組成和處理流程如圖1所示。PLL控制器能夠通過PLLDIV1到PLLDIV16這些分頻器靈活便利的配置和修改內部的時鐘信號

2018-01-24 21:27:10

4的JEDEC標準DDR4接口的變體,它包含了對完整系統支持所需的獨特功能。本文將幫助工程師了解Xilinx FPGA控制器的Everspin STT-DDR4設計指南

2021-01-15 06:08:20

你好任何人都可以指導我,Xilinx ISE中的DDR控制器是否有任何IP實現。如果沒有如何實現DDR控制器以上來自于谷歌翻譯以下為原文Hi can any one guide me

2019-02-27 12:13:51

/ p作為輸入時鐘連接到CLKGENERATOR,DDR控制器在Phy側運行800Mhz,在控制器運行200Mhz.Slave AXI總線寬度為AXI.DDRis 512bits。卡皮爾古普塔project_6.srcs.rar 6322 KB

2019-09-10 07:58:12

Rambus DRAM與CTM時鐘同步輸出數據。如果時鐘與數據信號的布線長度等相同,則時鐘與數據具有相同的延遲時間到達DRAM控制器,所以DRAM控制器可以與時鐘同步接受數據。 另一方面

2008-12-04 10:16:36

本文和設計代碼由FPGA愛好者小梅哥編寫,未經作者許可,本文僅允許網絡論壇復制轉載,且轉載時請標明原作者。Altera DDR2控制器使用IP的方式實現,一般很少自己寫控制器代碼。ddr

2020-02-25 18:33:00

為什么XMC庫不使用控制器的端口輸出寄存器TESTBOARD_150PC_OUT ?

程序庫僅使用端口輸出修改寄存器 Pn_OMR 來設置或清除數字輸出。

2024-03-06 06:17:41

我是一名labview FPGA程序員,使用的是NI 7975 fpga模塊,它具有kintex 7 fpga。該模塊具有外部DDR3 DRAM 0f 2GB以及kintex 7 fpga資源。數據應該從芯片到芯片之間會有多少延遲?這是DDR3 DRAM雙端口(同時讀寫操作可能??)???

2020-05-20 14:42:11

這是我自己寫ddr2控制器的寫操作,但為什么寫的地址不按順序寫,有誰做過嗎?

2017-03-20 16:36:20

我可以使用mig生成ddr控制器(xc6vlx130t)嗎?mig向導只支持ddr2和ddr3!

2020-06-12 07:32:48

請求。物理層接口前端連接至內存控制器模塊,后端連接外部存儲設備,其主要功能是捕獲DDR3發出的數據,產生DDR3所需要的控制指令信號,并通過輸入輸出緩存發送所有DDR3的控制信號、地址信號以及數據信號

2018-08-02 09:34:58

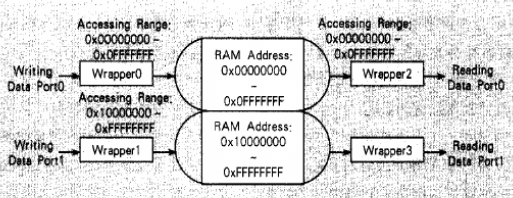

作者:吳連慧,周建江,夏偉杰摘要:為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器

2018-08-02 11:23:24

的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR3讀寫操作。DDR3用戶接口仲裁控制模塊將中斷請求分成多個子請求,實現視頻中斷和圖形中斷的并行

2024-06-26 18:13:42

DDR控制協議

DDR3讀寫控制器主要用于生成片外存儲器DDR3 SDRAM進行讀寫操作所需要的時序,繼而實現對片外存儲器的讀寫訪問。由攝像頭采集得到的圖像數據通常數據量較大,使用片內存儲資源

2025-10-21 14:30:16

如何實現雙路輸出控制器的設計?

2022-02-11 07:57:24

DDR3存儲器控制器面臨的挑戰有哪些?如何用一個特定的FPGA系列LatticeECP3實現DDR3存儲器控制器。

2021-04-30 07:26:55

你好使用Xilinx的任何一個端口MIG DDR2 SDRAM控制器都是我遇到了問題我有vhdl頂級系統,其中我實例化ddr2控制器我的ddr2包裝器與testcase一起工作正常(由MIG提供

2019-08-19 10:47:06

你好如何在不使用DDR內存控制器的情況下設計FPGA BRAM(或任何其他內存模塊_SD,DDR以外的本地等)大容量存儲單元?當我通過示例設計“VC707_bist”替換DRAM控制器和BRAM

2019-04-04 15:10:55

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

嗨,我已經搜索了很多關于配置PS DRAM控制器(DDRC)板參數的信息,鏈接如下,http://www.xilinx.com/support/answers/46778.htm, 我想知道如何獲得包裝長度?謝謝!

2019-11-07 08:43:39

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq

2021-01-07 16:02:09

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

嵌入式控制器的輸入端口設計分析,不看肯定后悔

2021-05-31 06:19:13

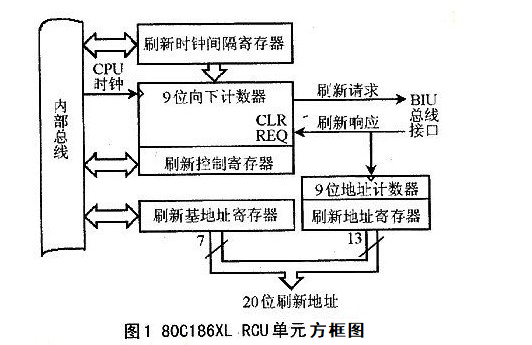

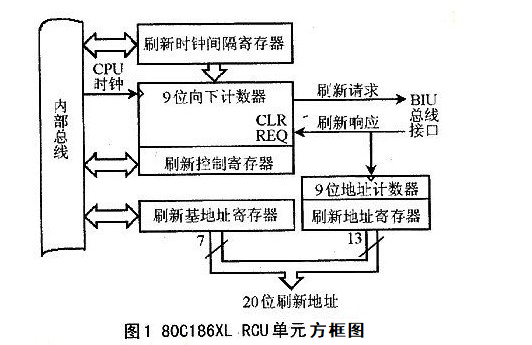

摘要:介紹怎樣在嵌入式CPU 80C186XL DRAM刷新控制單元的基礎上,利用CPLD技術和80C196XL的時序特征設計一個低價格、功能完整的DRAM控制器的方法,并采用VHDL語言編程實現

2011-02-24 09:33:15

學單片機的都必須清楚微控制器的輸入輸出,點燈是練習輸出,而輸入最基礎的就需要去練習——按鍵。

2021-11-29 07:38:40

大家好,我想設計自己的DDR控制器并在FPGA上驗證它。我將在verilog中實現我剛開始閱讀JESDC79C DDR規格..但我很困惑如何編寫那些初始化序列?請建議如何處理這個設計DDR控制器

2019-04-29 11:59:22

有沒有辦法重置和重新初始化 DDR 控制器?DRAM 類型是 LPDDR4。

我們的目標:我們嘗試為組裝有不同大小 RAM 的電路板系列實施解決方案。

為了獲得可重現的結果,我們尋求在嘗試下一個配置

2023-05-16 09:03:04

本文介紹了怎樣在嵌入式CPU 80C186XL DRAM刷新控制單元的基礎上,利用CPLD技術和80C196XL的時序特征設計一個低價格、功能完整的DRAM控制器的方法,并采用VHDL語言編程實現。

2021-04-28 07:10:38

DDR SDRAM在嵌入式系統中有哪些應用?DDR SDRAM的工作方式有哪幾種?怎樣去設計DDR SDRAM控制器?

2021-04-30 07:04:04

FPGA與DDR2存儲器接口DDR2控制器的設計原理是什么?DDR2控制器的應用有哪些?

2021-04-30 06:28:13

設計實現了一種基于FPGA 的,可用于多數據緩存的、能夠高效利用帶寬的多端口SDRAM 控制器。本文使用狀態機的設計思想,采用Verilog 硬件描述語言設計了時序控制程序。得到的SDR

2009-08-27 09:43:33 23

23 DDR2 SDRAM控制器的設計與實現

本文介紹了&&," -&,+. 的基本特征!并給出了一種&&," -&,+. 控制器的設計方法!詳述了其基本結構和設計思想!并使用+JC:8B 公

2010-02-09 14:57:51 64

64 本文采用Altera 公司的Stratix 系列FPGA 實現了一個三端口非透明型SDRAM 控制器,該控制器面向用戶具有多個端口,通過輪換優先級的設計保證了多個端口平均分配SDRAM的帶寬且不會降

2010-03-03 14:37:14 11

11 本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結構和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 輸入電壓高達38V的汽車級、四輸出控制器-MAX17019

MAX17019是高輸入電壓、4路輸出控制器,用于汽車系統。

2009-01-22 13:12:11 1338

1338 文章對適用DDR2 SDRAM控制器的結構、接口和時序進行了深入研究與分析,總結出一些控制器的關鍵技術特性,然后采用了自頂向下(TOP-IX)WN)的設計方法,用Verilog硬件描述語言實現控制器,

2011-09-01 16:36:29 174

174 ADI,全球領先的高性能信號處理解決方案供應商,最近推出 GPIO(通用輸入/輸出)端口擴展器和鍵盤矩陣控制器 ADP5585和 ADP5589

2011-09-14 14:17:53 2714

2714 本文提出一種新穎的解決方案:利用80C186XL的時序特征,采用CPLD技術,并使用VHDL語言設計實現DRAM控制器。

2012-02-02 11:29:58 1863

1863

帶自測功能的DDR2控制器設計,感興趣的可以看看。

2016-01-04 15:23:32 0

0 基于等價輸入干擾估計器的永磁同步電機控制器的設計與實現,有興趣的同學可以下載學習

2016-04-26 18:16:42 22

22 Xilinx FPGA工程例子源碼:DDR SDRAM控制器參考設計VHDL代碼

2016-06-07 11:44:14 19

19 Xilinx FPGA工程例子源碼:DDR SDRAM控制器verilog代碼

2016-06-07 14:13:43 40

40 基于協議控制器的DDR3訪存控制器的設計及優化_陳勝剛

2017-01-07 19:00:39 16

16 引言 LTC3876 是一款完整的 DDR 電源解決方案,可與 DDR1、DDR2、DDR3 和 DDR4 較低的電壓兼容。該 IC 包括 VDDQ 和 VTT DC/DC 控制器和一個高精度線性

2017-05-10 16:37:39 12

12 DDR 控制器部產品營銷總監 概述 DDR DRAM內存控制器要滿足眾多市場競爭的需求。一款出色的內存控制器必須能夠增加存儲器接口的帶寬,滿足CPU、圖形處理、系統實時DRAM的延遲需求,同時符合

2017-11-18 18:23:12 3509

3509 為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR

2017-11-18 18:51:25 7989

7989

提出一種便于用戶操作并能快速運用到產品的DDR2控制器IP核的FPGA實現,使用戶不需要了解DDR2的原理和操作方式的情況下,依然可以通過IP核控制DDR2。簡單介紹了DDR2的特點和操作原理,并

2017-11-22 07:20:50 5930

5930

DDR SDRAM的接口特性:其輸入輸出引腳與SSTL-Ⅱ電氣特性兼容,內部提供了DDR觸發器、鎖相環等硬件資源。使用這些特性,可以比較容易地設計性能可靠的高速DDR RAM控制器。本文介紹一種采用FPGA與IP來實現DDR RAM控制和驗證的方法。

2017-11-24 16:00:22 4673

4673

DRAM (動態隨機訪問存儲器)對設計人員特別具有吸引力,因為它提供了廣泛的性能,用于各種計算機和嵌入式系統的存儲系統設計中。本文概括闡述了DRAM 的概念,及介紹了SDRAM、DDR SDRAM、DDR2 SDRAM、DDR3 SDRAM、DDR4 SDRAM、LPDDR、GDDR。

2018-06-07 22:10:00 95076

95076 本文透過對于靜態隨機存取內存(SRAM)單元縮減布局面積的研究,提出一種新的 存取技術 ,可望提升動態隨機存取內存( DRAM )單元的訪問速度。 超頻與內存的關聯性 提升供應電壓以及降低環境溫度有助于增加微處理器、芯片組、主存儲器的頻率頻率。

2018-03-28 12:03:00 5022

5022

DDR 同步動態隨機存取存儲器 (Synchronous Dynamic Random Access Memory, SDRAM)控制器使用雙倍數據速率(Dual Data Rate,DDR)版本

2018-05-30 09:29:00 8

8 本文首先介紹的是PID控制器的工作原理,其次介紹的是pid控制器的輸入輸出,最后介紹了PID控制器的參數整定以及PID控制器的控制實現,具體的跟隨小編一起來了解一下。

2018-06-01 09:09:01 31261

31261 Random Access Memory的縮寫,即同步動態隨機存取存儲器。而DDR SDRAM是Double Data Rate SDRAM的縮寫,是雙倍速率同步動態隨機存儲器的意思。

2019-02-04 11:40:00 9513

9513 本應用說明描述了一個參考系統,該系統演示了Microblaze?處理器系統中多通道(MCH)片上外圍總線(OPB)雙數據速率(DDR)同步DRAM(SDRAM)控制器的使用。MCH OPB DDR

2019-09-12 14:14:00 0

0 、PSRAM、MRAM等存儲芯片供應商英尚微電子解析這款比腦力更強大的DDR SDRAM控制器。 任何DRAM控制器背后的智商都是與命令時序和執

2020-07-24 14:25:27 1196

1196 DRAM作為PC必備器件之一,大家自然對DRAM較為熟悉。但是,大家知道DRAM存儲具有哪些分類嗎?大家了解DRAM控制器是如何設計出來的嗎?如果你對DRAM以及本文即將要闡述的內容具有興趣,不妨繼續往下閱讀哦。

2020-10-31 11:51:19 4799

4799

Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上與 Zynq

2021-02-23 06:00:10 15

15 100V 輸入 DC/DC 控制器產生正或負的穩壓輸出

2021-03-19 08:09:16 4

4 隔離式 8 端口 PoE PSE 控制器無需光耦合器以實現最低的解決方案成本

2021-03-20 14:54:07 5

5 四端口和單端口 LTPoE++ PSE 控制器提供高達 90W

2021-03-20 22:50:58 9

9 本應用指南描述了在 Virtex?-4 XC4VLX25 FF668 -10C 器件中實現的 DDR SDRAM 控制器。該實現運用了直接時鐘控制技術來實現數據采集,并采用自動校準電路來調整數據線上的延遲。

2021-03-26 14:42:41 4

4 本文首先分析了DDR SDRAM的基本特征,并提出了相應的解決方案詳細介紹了基于J EDEC DDR SDRAM規范的DDR SDRAM控制器設計方案。該控制器采用Verilog HDL硬件描述語言實現,并集成到高性能SoC中。

2021-03-28 10:57:24 23

23 AN-284:用模擬輸入/輸出端口實現無限采樣保持電路

2021-04-22 16:19:39 12

12 LTC3718:適用于DDR/QDR存儲器終端的低輸入電壓DC/DC控制器產品手冊

2021-05-22 16:14:04 6

6 基于FPGA的DDR3SDRAM控制器設計及實現簡介(arm嵌入式開發平臺PB)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現簡介資料,講解的還不錯,感興趣的可以下載看看…………………………

2021-07-30 09:05:51 7

7 基于FPGA的DDR3SDRAM控制器設計及實現(嵌入式開發式入門)-該文檔為基于FPGA的DDR3SDRAM控制器設計及實現總結文檔,是一份很不錯的參考資料,具有較高參考價值,感興趣的可以下載看看………………

2021-07-30 13:07:09 37

37 的性能更高,并且不額外占用其他的可編程邏輯資源 (PL)。使用它的時候,在硬件設計方面和設計流程上,和之前的軟核控制器(DDR4 IP)也有著很大的不同。今天我們來介紹一下I/O planning方面的設計考慮和實現流程。

2022-07-06 10:42:17 5678

5678 USB音頻輸入/輸出控制器DP108 簡述和特征

2022-10-26 18:01:52 2288

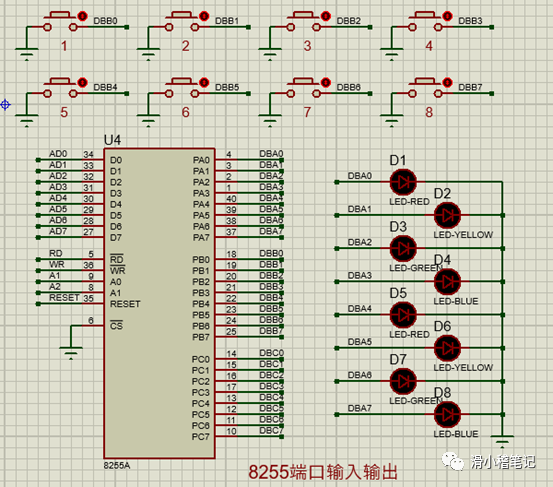

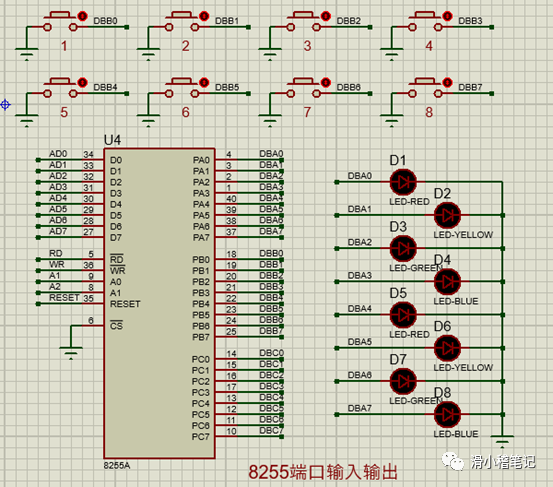

2288 8086的輸入輸出控制是通過8255芯片控制的,用LED代表輸出的數據,按鍵代表輸入的數據,八個LED接在8255的PA端口上,八個按鍵接在PB端口上,通過8086控制8255A進行數字量的輸入與輸出。

2023-03-02 09:56:04 3809

3809

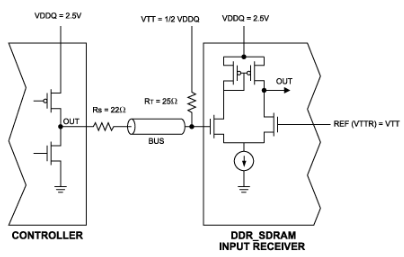

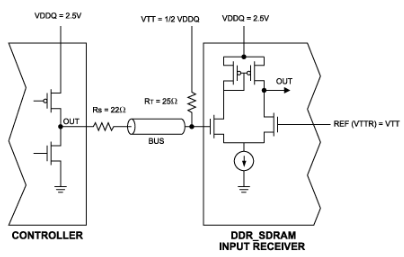

雙倍數據速率(DDR)同步動態隨機存取存儲器(SDRAM)最近越來越受歡迎。DDR 內存需要跟蹤主內存電壓 VDDQ 的主動端接 VTT。本應用筆記提供開關穩壓器方案,利用MAX1957脈寬調制(PWM)降壓控制器為VTT端接提供1/2跟蹤輸出。

2023-03-13 09:35:23 3102

3102

的作用。

編寫程序:編寫控制程序,包括輸入和輸出信號的邏輯關系和運算方法。

連接設備:將需要控制的設備連接到PLC控制器的輸入和輸出端口上。

2023-03-25 09:41:14 1694

1694 電子發燒友網站提供《完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-03-13 10:16:45 1

1 電子發燒友網站提供《完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-04-09 09:49:32 0

0 DDR和LPDDR都是動態隨機存取存儲器(DRAM)的類型,它們在計算機和移動設備中用于臨時存儲數據。

2024-05-12 15:19:00 4796

4796 在工業自動化領域中,PLC(Programmable Logic Controller,可編程邏輯控制器)因其高度的可靠性、靈活性和強大的功能而備受青睞。PLC系統通過其輸入端口接收外部信號,經過

2024-06-19 14:11:05 7327

7327 近日,DRAM(動態隨機存取存儲器)市場傳來重磅消息,由于服務器需求持續強勁及產能排擠效應顯著,多家大廠決定在第三季度對DDR5內存價格進行新一輪調整。據供應鏈最新消息,三星電子與SK海力士這兩大DRAM巨頭已正式發出通知,宣布DDR5內存的單季價格將實現15%以上的顯著上漲。

2024-08-21 15:40:01 1224

1224 TPS51116為 DDR/SSTL-2、DDR2/SSTL-18、DDR3/SSTL-15、DDR3L、LPDDR3 和 DDR4 內存系統提供完整的電源。它將同步降壓控制器與 3A 灌電流/拉

2025-04-29 16:38:02 1034

1034

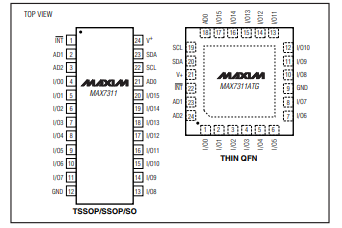

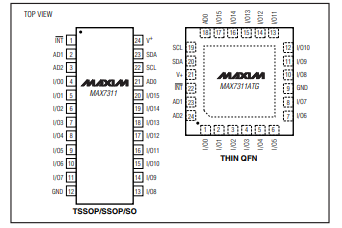

MAX7311 2線接口擴展器為兼容于SMBus?和I2C的應用提供16位并行輸入/輸出(I/O)端口擴展。MAX7311包含輸入端口寄存器、輸出端口寄存器、極性反轉寄存器、配置寄存器、總線延時

2025-05-26 11:33:37 678

678

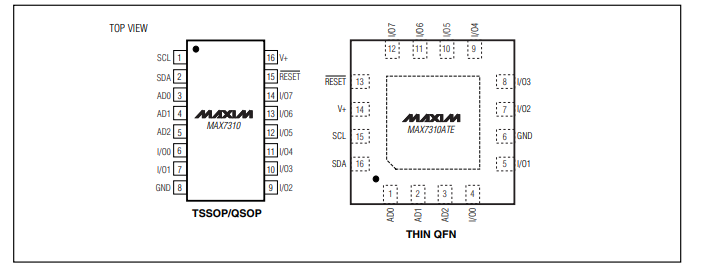

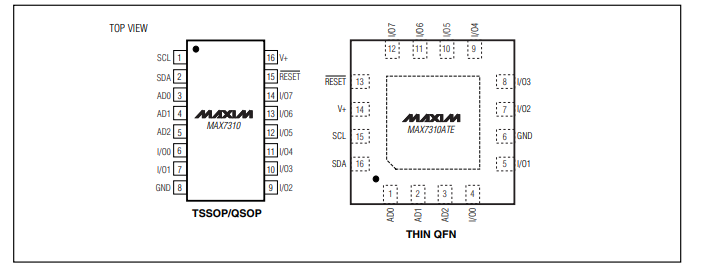

MAX7310為兼容于SMBus?和I2C的應用提供8位并行輸入/輸出端口擴展。MAX7310包含輸入端口寄存器、輸出端口寄存器、極性反轉寄存器、配置寄存器、總線延時寄存器和一個SMBus/I2C

2025-05-26 15:41:31 827

827

在當今高速發展的3C領域(計算機外設、通信及消費電子),對存儲器的性能與功耗提出了更高要求。DRAM動態隨機存取存儲器作為核心存儲部件,其性能表現直接影響設備整體效能。Etron憑借其活緩沖DRAM

2025-12-01 13:42:00 254

254 FPC401四端口控制器:高速網絡時代的端口控制利器 在如今高速發展的網絡通信領域,端口控制的高效性和穩定性顯得尤為重要。德州儀器(TI)推出的FPC401四端口控制器,為SFP+、QSFP+

2025-12-19 09:45:02 143

143

電子發燒友App

電子發燒友App

評論