本文主要是Lattice公司市場總監Shakeel Peera給大家談面對競爭激烈的FPGA市場,Lattice公司將持續優化FPGA成本和功耗。

2012-08-14 14:12:55 1159

1159

iCEstick評估套件加速了使用該器件的解決方案的開發,擁有針對紅外和傳感器功能的硬件特性和參考設計,適用于智能手機、平板電腦、游戲機以及其他有著嚴格的低成本、低功耗和快速上市時間要求的應用

2013-08-29 23:07:06 2027

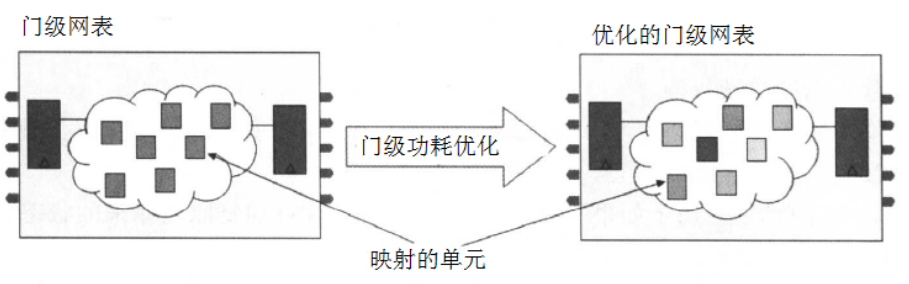

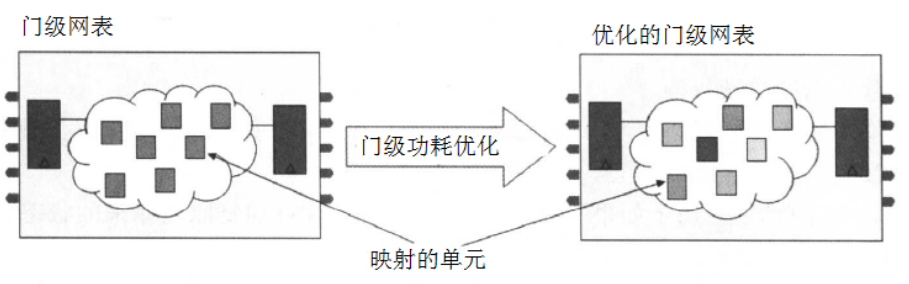

2027 門級電路的功耗優化(Gate Level Power Optimization,簡稱GLPO)是從已經映射的門級網表開始,對設計進行功耗的優化以滿足功耗的約束,同時設計保持其性能,即滿足設計規則和時序的要求。

2020-07-02 16:28:31 6907

6907

技術實現多IP核集成可以顯著減少芯片的研發成本;與方法二相比,改進方法不僅能夠有效整合芯片內部資源,還可以降低系統功耗,提高芯片的整體性能。

2020-09-08 17:58:00 4232

4232

高質量DesignWare接口和模擬IP經過優化,可在人工智能、云計算和移動芯片中實現高性能和低功耗。

2019-06-29 09:49:28 3311

3311 EDGE和3G支持,射頻組件和子系統廠商再也不能將這一重擔推到OEM廠商身上。相反,射頻廠商現在開始承擔這一責任。他們不僅需要減少組件數量并降低射頻子系統的成本,還需要提供問題最少、功能強大的射頻前端子系統來加快上市時間,同時實現與上一代2G子系統相同的效益。原文位置

2019-06-26 08:17:58

充電倉提供完整的電源解決方案。 IP5416 通過一個電感實現升壓功能。其高集成度與豐富功能,使其在應用時僅需極少的外圍器件,并有效減小整體方案的尺寸,降低 BOM 成本。 IP5416 內置一個 5V

2021-07-07 20:00:43

方案的尺寸, 降低 BOM 成本。 IP5502 只需一個電感實現充電與升壓功能。可 以支持低成本電感和電容。 IP5502 的同步升壓系統提供額定 1A 輸出電流, 轉換效率高至 91%。輕載時,可設

2022-05-04 18:29:51

IP6805U是一款無線充電發射端控制SoC 芯片,兼容 WPC Qi v1.2最新標準 ,片內集成全橋驅動電路和 全橋功率 全橋功率 MOS ,電壓 &電流兩路通訊解調模塊 ;方案集成度高

2019-11-29 20:39:50

IP6818 是一款集成 Qi 無線充接收、5V 升壓轉換器、鋰電池充電管理、電池電量指示的多功能電源管理 SoC,為無線充 TWS 藍牙耳機充電倉提供完整的電源解決方案。IP6818 的高集成

2020-10-28 18:43:15

一款新的LXI儀器可以通過PXI節省機架空間、資金和集成時間。本應用說明介紹了三者之間的相互關系,并針對謹慎使用SCPI,避免LAN延遲問題以達到優化執行時間進行了闡述。

2019-10-09 08:29:25

和風能等可再生能源的普及,能源計量設備需提供更精細的功耗數據以優化使用和降低成本。應用包括智能電表、EV充電樁、電源分配單元、智能家電、路燈和樓宇自動化。成本壓力與區域標準(如 ANSI C12、歐盟

2025-08-19 17:18:23

成本優化的太陽能

2019-09-26 08:10:45

■ 愛特梅爾(Atmel)公司 Peter Bishop集成電路應用中的四大挑戰采用的晶體管數目晶體管數目會直接影響到裸片和封裝尺寸、芯片成本及功耗。盡管生產工藝的不斷進步使晶體管的面積越來越小,但

2019-07-25 06:14:54

驅動時序和副邊同步整流器控制特性。利用自適應停滯時間補償可進一步優化能效,從而改善負載范圍內及可編程輕載模式下的效率,同時器件具有低功耗(

2018-09-26 16:04:09

模擬和數字電路于一體。 模擬陣列為工業、醫療和消費者市場上的應用提供靈活、快速的上市時間解決方案。應用實例包括安全感應、識別、感光及電池管理等工業應用,還有血糖儀、血液分析儀和傳感器接口等醫療設備

2018-08-27 16:07:43

成本優化、低功耗、小尺寸

2023-03-24 15:06:22

時間,降低了制造成本。直觀的邏輯合成環境包括先進的優化技術、屢獲殊榮的時序分析和先進的推論技術,適用于與供應商無關的設計中,可加快產品上市時間、消除設計缺陷以及提供極佳的結果質量 (QoR)。 FPGA

2018-09-20 11:11:16

。

驗證和測試:集成IP內核后,需要對整個設計進行驗證和測試,以確保內核的正確性和性能。這可以通過仿真、硬件在環測試或實際硬件測試來完成。

優化和迭代:根據測試結果,可能需要對設計進行優化,如調整內核

2024-04-28 09:41:04

芯片對功耗的苛刻要求源于產品對功耗的要求。集成電路的迅速發展以及人們對消費類電子產品——特別是便攜式(移動)電子產品——的需求日新月異,使得設計者對電池供電的系統已不能只考慮優化速度和面積,而必

2019-11-06 07:57:07

、功耗和容量都已經達到甚至超過此前專用IC或專用標準器件(ASSP)的水平。可編程硬件的可配置特點不僅具備產品差異化和快速上市等傳統優點,同時當批量達不到足以支持開發專用IC成本的時候還可以加快投資回報

2019-08-13 07:48:48

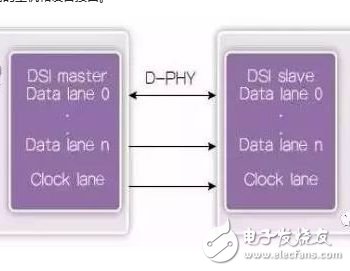

LCD因具有工作電壓低、功耗小、顯示信息量大、壽命長、易集成、方便攜帶和電磁輻射污染小等優點,在顯示技術中異軍突起,被廣泛應用于手機、PDA產品、手持式儀器儀表等便攜式電子產品與設備中。 LCD

2012-08-12 12:28:42

Micronas公司近日宣布推出HAL 28xy系列霍爾效應傳感器,專為對精度、靈敏度及低成本有要求的汽車和機電應用而優化。HAL 28xy是首款集成了微控制器、溫度傳感器、先進的片上補償以及

2018-10-29 15:11:02

通信行業專家的解讀是,設備消耗的能量與數據量或速率有關,單位時間內發出數據包的大小決定了功耗的大小。NB-IoT引入了eDRX省電技術和PSM省電模式,進一步降低功耗,延長了電池使用時間

2016-12-15 18:21:14

引言在工業系統中選擇器件需要考慮多個因素,其中包括:性能、工程變更的成本、上市時間、人員的技能、重用現有IP/程序庫的可能性、現場升級的成本,以及低功耗和低成本。工業市場的近期發展推動了對具有高

2019-06-24 07:29:33

ipad2香港上市時間又“跳票” “又跳票了!”日前,坊間有傳言稱ipad2將于4月25日在香港上市,但至記者截稿時,港行市場上仍不見ipad2蹤影,ipad2香港上市時間的再次“跳票”,也讓深圳

2011-04-27 14:07:12

無論從微觀到宏觀、從延長電池壽命到減少全球變暖的溫室效應等等,各種不同因素都在迅速推動系統設計人員關注節能問題。一項有關設計優先考慮事項的最新調查指出,大部分工程師已把功耗排在首位,或者是將其緊跟在性能、密度和成本之后。在功耗方面,FPGA帶來了獨特的挑戰。為什么要設計優化FPGA功耗?

2019-08-08 07:39:45

變異。需要多重物理IP平臺,包括基于面積/功耗優化庫、為高端性能定制優化庫以及為CPU定制的優化庫。 中芯國際SoC研發中心技術處長吳漢明博士:資金短缺是新工藝研發攔路虎 技術節點的發展方向離不開

2019-05-20 05:00:10

三款經過驗證、已上線的全新低功耗解決方案可方便實現USB Type-C接口設計,并能減少開發時間和風險 低功耗USB Type-C接口充電器和設備的參考設計現已推出 使得消費電子和工業用戶能夠獲益于

2019-06-17 05:00:07

的增加:尺寸、功耗、電路板、元件數和成本。設計工程師如何權衡抵抗有害脈沖和浪涌、設計復雜性以及成本等互相沖突的要求,同時盡可能加快上市以保持競爭力?您可以輕易將一組光耦合器固定到現有接收器上,但這么做

2018-10-26 11:02:30

全球定位系統到音視頻媒體流處理,這些應用都需要實時地執行復雜的算法,很多這些算法都需要遵從定期更新的行業標準。工程師開發這些應用面臨的挑戰是在單位成本、外形尺寸和功耗,以及嚴格的成本和開發時間約束下

2008-09-27 11:42:55

(mapCurrentClockDomain除了不包含clockDomain外無差別):指定IP代碼路徑SpinalHDL集成Verilator仿真器仿真接口,在對帶RTL IP的代碼進行仿真時,需指定

2022-06-22 14:59:25

使用生命周期和保證性能的基礎上,大大精簡了封裝和工序,有效控制了成本。低功耗電路設計在電路設計上易飛揚也做了一系列優化動作:堅持低功耗設計導向,采用低功率電路設計,智能電源設計以及優化的低電壓設計實現低功耗

2021-05-28 14:55:10

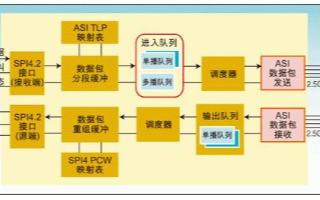

)。OCP簡介基于IP核復用技術的SoC設計使芯片的設計從以硬件為中心轉向以軟件為中心,芯片設計不再是門級的設計,而是IP核和接口及其復用設計。IP核集成到系統所要考慮的問題包括:同步,例如全局執行

2019-06-11 05:00:07

和每立方厘米的能量不斷增長。然而,物聯網應用在成本和空間方面的限制更高,因此,物聯網芯片系統 (SoC) 設計師不能僅依賴更昂貴或更大的電池來延長設備使用時間。本文介紹了設計師如何在低功耗工藝技術上使用Foundation IP(邏輯庫和嵌入式存儲器)來減少物聯網設計的功耗。

2019-07-26 07:01:11

。與星形系統示例類似,利用Virtex-5LXT解決方案,可以提高集成度、縮短上市時間、優化系統特性、降低功耗和成本等。本文結論如今,串行背板技術已成為主流技術。隨著帶寬要求的與日俱增,將有越來越多

2019-04-12 07:00:11

和并行接口IP核,Xilinx還提供了更加完善的IP解決方案,以進一步縮短產品開發周期和上市時間。包括用于優化背板流量的流量管理器和允許板卡之間實現“多對多”連接功能的網狀結構參考設計。此外

2019-04-16 07:00:05

逐漸減少──顯然,借助更快速度以實現摩爾定律的方法不再靈驗!功耗和微架構改良的限制,使單一處理器的發展前景受挫,業界的關注焦點已轉向多處理器或多核芯片架構的開發潛力。

2019-08-02 06:32:24

(ADC)中分別使用分立的芯片。這種分立方案使得許多系統尺寸龐大、成本高昂且功耗高,如此才能獲得所需的通道數量,進而發揮所需的功能。由于制造和校準過程復雜,這些系統通常也需要很長時間才能上市。

2019-09-11 11:52:03

本應用指南介紹了使用 UCC28056 優化過渡模式 PFC 設計以提高效率和待機功耗的設計決策。

2021-06-17 06:52:09

量。通過采用基于40nm的半導體最新制造工藝以及創新方法來優化這些復雜的器件,設計人員能夠在單芯片中集成更多的功能。這不但降低了總功耗,而且還可以降低后續工藝節點每一相應功能的功耗。TPACK便是能夠

2019-07-31 07:13:26

任何地方的人打電話。與此類似,在醫療領域,早期所謂的“便攜式”超聲系統是推車式的,且在功耗較高、成本昂貴。幸運的是,超聲系統近年來也得益于芯片集成和功耗調整技術的突破。

2020-05-19 06:11:27

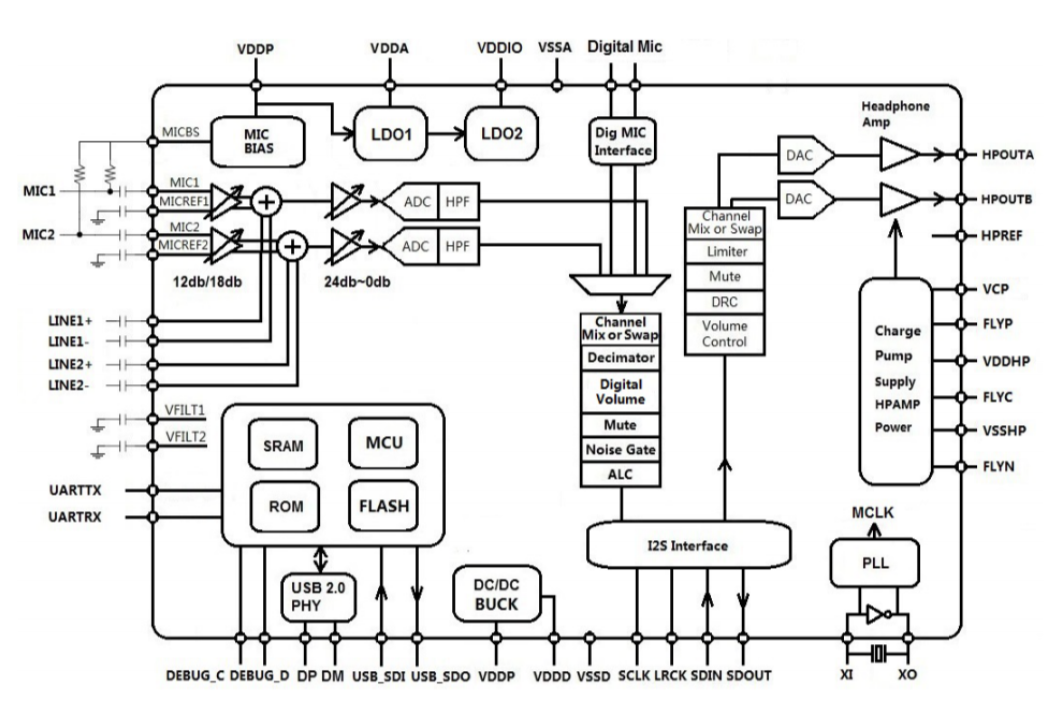

、先進的數字信號處理(DSP)算法,而且需要節省空間和省電。而安森美半導體近期推出的LC823450超低功耗單芯片方案,集成了高分辨率的聲音處理、音頻應用所需的功能,并具有超低功耗、小尺寸、降低成本、加快產品上市等一系列優勢。

2019-10-09 06:16:18

時間,CLKOUT,電源管理,帶有接口的時間戳激活用于PCF2127AT / PCF2129AT TCXO的應用程序。 PCF212xAT是CMOS實時時鐘(RTC)和日歷IC,集成了溫度補償晶體

2020-03-20 07:39:10

到XC5VLX30T器件上,而中繼卡接口結構則可裝入到XC5VLX50T器件上。與星形系統示例類似,利用Virtex-5LXT解決方案,可以提高集成度、縮短上市時間、優化系統特性、降低功耗和成本等

2019-05-05 09:29:30

的SoC 設計使芯片的設計從以硬件為中心轉向以軟件為中心,芯片設計不再是門級的設計,而是IP核和接口及其復用設計。IP核集成到系統所要考慮的問題包括:同步,例如全局執行、數據交換和協議方面的同步操作

2018-12-11 11:07:21

怎么實現基于LFSR優化的BIST低功耗設計?

2021-05-13 06:21:01

為了實現超小的尺寸和更快的上市時間,手機制造商希望采用采用經過驗證和測試的集成無線電模塊,和小尺寸、簡化的RF硬件方案,為其他高端功能節省空間。所以復雜的RF前端模擬、數字和高頻電路需要達到更高

2019-09-26 08:06:32

集成和系統的驗證。本文以現成的無線SoC設計(如GSM手機)中增加一個復雜的無線功能,即Bluetooth功能的實例來說明這一原理。Bluetooth實例充分體現確切地定義了硬件與軟件接口模塊化協議

2012-12-19 10:13:14

描述TIDA-00847 TI 設計展示了一個 4 通道直流輸入二進制模塊的空間和成本優化型架構,該模塊在測量精度和狀態指示方面進行了改進,且僅使用兩個 TI 產品,簡化了系統設計。基于 MCU

2018-10-26 10:14:32

CMOS 集成電路動態功耗的認知也是數字后端必須要掌握的;我們來聊一聊。動態功耗 = Switching Power +Internal PowerSwitching power 是由于芯片內

2022-06-09 18:06:15

P1014-RDB,QorIQ P1014參考設計板,用于具有信任架構的P1014低功耗通信處理器。 P1014 RDB是一款高度集成的參考設計板,可幫助縮短產品上市時間。該參考設計針對低成本網絡應用(有或沒有信任架構),有線和無線接入,工業和智能能源應用

2019-04-18 09:28:52

做到非常簡潔,PCB上僅有一顆主控芯片,所有功能由一顆芯片實現。外圍元件的減少,極大的精簡了生產測試流程,有效降低開發難度和成本,便于產品的快速開發、生產和上市銷售。由于IP6808高度集成的特性

2019-01-28 16:19:04

常用的設計技巧就是在數據傳送的接口建立申請和應答機制。這雖然會造成芯片在時序、面積、功耗等方面的損耗,但對于加快系統芯片的上市速度大大有利。 第三,要注意積累IP和IP集成的經驗。一旦成功地集成

2018-09-04 09:51:06

,為移動電源提供完整的電源解決方案。IP5219 的高集成度與豐富功能,使其在應用時僅需極少的外圍器件,并有效減小整體方案的尺寸,降低 BOM 成本。 IP5219 只需一個電感實現降壓與升壓功能,可以

2021-12-29 18:39:33

一顆主控芯片,所有功能由一顆芯片實現。外圍元件的減少,極大的精簡了生產測試流程,有效降低開發難度和成本,便于產品的快速開發、生產和上市銷售。由于IP6808高度集成的特性,適用于小尺寸和低成本解決方案

2018-07-23 19:48:43

以SCI接口電路為例,介紹基于FPGA器件的接口電路IP核如何去設計?

2021-04-28 06:10:23

的靈活性,以支持算法演進、各類接口和性能;3.功能全面的Lattice sensAI通過合作伙伴生態系統提供模塊化硬件平臺、神經網絡IP核、軟件工具、參考設計和定制化解決方案;Lattice sensAI

2018-05-23 15:31:04

于設計出符合要求的軟 IP 核。 另外一方面,軟 IP核的設計成本和設計時間一般都是大于硬 IP核。 這些是簡單的可合成 IP 模塊,供應商將通過給這些模塊添加標簽以跟蹤它們,因為它們很容易被任何人竊取

2021-10-07 21:03:56

字消息、拍照、查詢股票、預約,當然還能給世界上任何地方的人打電話。與此類似,在醫療領域,早期所謂的“便攜式”超聲系統是推車式的,且功耗較高、成本昂貴。幸運的是,超聲系統近年來也得益于芯片集成和功耗調整技術

2018-10-23 14:28:19

引言隨著應用的不斷普及和深入,在設計嵌入式系統時,往往需要同時優化眾多因素,如成本、功率、尺寸、性能、靈活性、產品上市時間、設計開發周期,以及可靠性等。Xilinx 公司推出的嵌入式處理器設計平臺

2019-07-19 07:03:19

了設計成本。核心架構提高了邏輯效率,是目前密度最高的互聯結構。硬核IP實現了高性能,提高了靈活性,而且縮短了設計時間。經過優化后的收發器具有同類最佳的信號完整性,減少了調試時間。僅使用兩種電壓軌,因此

2015-02-09 15:02:06

2023年1月13日,知名物理IP提供商 銳成芯微(Actt) 宣布在22nm工藝上推出雙模藍牙射頻IP。近年來,隨著藍牙芯片各類應用對功耗、靈敏度、計算性能、協議支持、成本的要求越來越高,22nm

2023-02-15 17:09:56

(1)門級電路的功耗優化綜述 門級電路的功耗優化(Gate Level Power Optimization,簡稱GLPO)是從已經映射的門級網表開始,對設計進行功耗的優化以滿足功耗的約束,同時

2021-11-12 06:14:26

商業領域占據了一定的市場。本文設計了一個高度集成、低功耗及低成本的微型慣性測量裝置,可精確地測算出載體的航向角、俯仰角及位置等信息,為運動軌跡跟蹤實驗打下了基礎,也可廣泛地應用于民用航空、車輛控制、機器人、工業自動化、探礦、玩具等領域。

2019-07-22 07:37:12

用接口IP實現HDMI的便攜式低功耗方案

通過使用知識產權(IP)方法,系統級芯片(SoC)設計師現在可以輕松地集成采用領先工藝技術(如90nm、65nm和40nm工藝)的HDMI接口。

2010-03-13 11:19:58 25

25 利用面向對象技術進行可配置的FFT IP 設計與實現摘要:為了縮短產品上市時間并降低設計成本,IP 復用已經成為IC設計的重要手段。以往利用RTL 代碼編寫的IP,往往是針對特定應

2010-07-04 11:42:13 8

8 IP4777CZ38/IP4778CZ38 全集成、帶有HDMI1.3接口調節功能的芯片

IP4777CZ38和IP4778CZ38在單芯片上帶來先進的HDMI接口調整功能

中國,北京2008年9月5日--恩

2008-09-09 16:31:10 1281

1281 高集成 5W 低成本支持QI無線充電芯片發射 控制器-IP6805S 一、特性 兼容WPC標準支持5W應用支持FOD異物檢測功能 高靈敏靜態異物

2024-12-19 14:35:51

英集芯IP5904是一款集成了充電管理和8位MCU功能的低功耗SOC(系統級芯片),專為小型電子設備設計。以下是該芯片的詳細介紹:一、芯片特點高集成度IP5904將充電管理與MCU功能集成于一體,僅

2025-01-18 12:05:42

英集芯IP5912是一款集成了降壓充電功能的低功耗8位POWER MCU芯片,以下是對其的詳細介紹: 一、產品概述英集芯IP5912內置了一個5V輸入的同步降壓充電DC-DC,以及內置

2025-01-21 10:37:12

優化面向超低功耗設計的微控制器功效

不論是消費、工業還是醫療應用,功耗優化一般都是通過縮短有效處理時間以及延長處理器睡眠模式時間來實現的。不過,隨著

2010-01-06 11:40:30 1188

1188 本文討論了OCP-IP的協議與特點,設計了基于AMBA總線的OCP-IP接口,提出了一種IP自動封裝的方法,為IP核的集成和管理帶來極大的方便。

2011-05-19 10:07:43 13048

13048

白皮書 :采用低成本FPGA實現高效的低功耗PCIe接口 了解一個基于DDR3存儲器控制器的真實PCI Express (PCIe) Gen1x4參考設計演示高效的Cyclone V FPGA怎樣降低系統總成本,同時實現性能和功耗

2013-02-26 10:04:25 73

73 Northwest Logic? 的 ?DMA? 內核現已支持 ?Vivado? 設計套件中的 ?IP? 集成器工具流。 IP? 集成器流可為客戶簡化將基于 ?AMBA? AXI4? 接口的 ?IP

2017-02-09 08:12:36 466

466

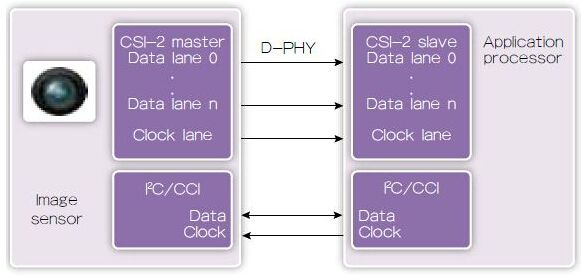

基于FPGA的低成本MIPI接口,專門針對視頻顯示器和攝像頭的。設計嵌入式系統DSI和CSI-2視頻接口的用戶現在即可采用低成本MIPI接口

2017-02-10 16:54:11 17542

17542 用戶可以使用IP集成器連接IP模塊創建復雜的系統設計。通過接口構建基于模塊的設計,一般情況下接口包含多個總線和大量的信號線。因此,為了方便在硬件上調試那些包含大量接口的設計,就需要驗證設計的接口連接。

2018-04-18 15:28:24 3578

3578

Microchip 的 RN4020 Bluetooth 低功耗模塊提供了一個

高度集成的低功耗藍牙 4.1 解決方案。高級命令接口加

速了上市時間。

2018-07-03 08:24:00 4

4 關鍵詞:SimpleLink , 藍牙低功耗 , 無線連接模塊 由于高級的集成有助于降低開發成本、減少RF設計挑戰、縮短上市時間且簡化采購和認證,無線連接模塊越來越受到工業4.0和物聯網(IoT

2018-08-20 15:36:01 594

594 查看UltraScale器件上可用的集成100G以太網MAC和CAUI-4 IP的演示。

通過軟件實現,該IP可節省高達80K的LUT和90%的功耗,簡化了設計流程并縮短了產品上市時間。

2018-11-28 06:07:00 5691

5691 連接您的服務器與架頂式交換機的方式中,與采用傳統光學連接相比,銅線兼具成本及功耗優化的優勢。您是否對采用更具成本效益的 25G 銅線連接更感興趣。

2019-08-01 14:49:04 2569

2569 與傳統ASIC相比,FPGA和結構化ASIC的優勢在于重用靈活性高、上市時間快、性能佳而成本低。FPGA和專用的IP模塊可用于現有的商用AdvancedTCA平臺,可用來開發可擴展的交換接口控制器(FIC),以加快產品開發的設計并使線卡方案具有魯棒性和成本效益。

2019-08-24 09:43:06 1336

1336

與傳統ASIC相比,FPGA和結構化ASIC的優勢在于重用靈活性高、上市時間快、性能佳而成本低。FPGA和專用的IP模塊可用于現有的商用AdvancedTCA平臺,可用來開發可擴展的交換接口控制器(FIC),以加快產品開發的設計并使線卡方案具有魯棒性和成本效益。

2020-07-23 17:58:06 1378

1378

在Blackfin處理器上使用.NET Micro Framework縮短上市時間和開發成本

2021-05-27 20:10:56 6

6 (1)門級電路的功耗優化綜述 門級電路的功耗優化(Gate Level Power Optimization,簡稱GLPO)是從已經映射的門級網表開始,對設計進行功耗的優化以滿足功耗的約束,同時

2021-11-07 11:05:59 19

19 VGA 接口集成了水平同步緩沖器、ESD 保護和終端電阻-IP4774CZ14

2023-02-21 18:42:18 0

0 帶集成緩沖器、ESD 保護和終端電阻的 VGA 接口-IP4773CZ14

2023-02-21 18:42:29 0

0 ,從而幫助開發人員減少工作量,并縮短產品上市時間。虹科針對不同的應用和領域開發了一系列以太網交換IP,因而用戶可以將不同IP的特征進行組合以獲得每種情況的最佳解決方案

2022-03-25 15:34:53 3571

3571

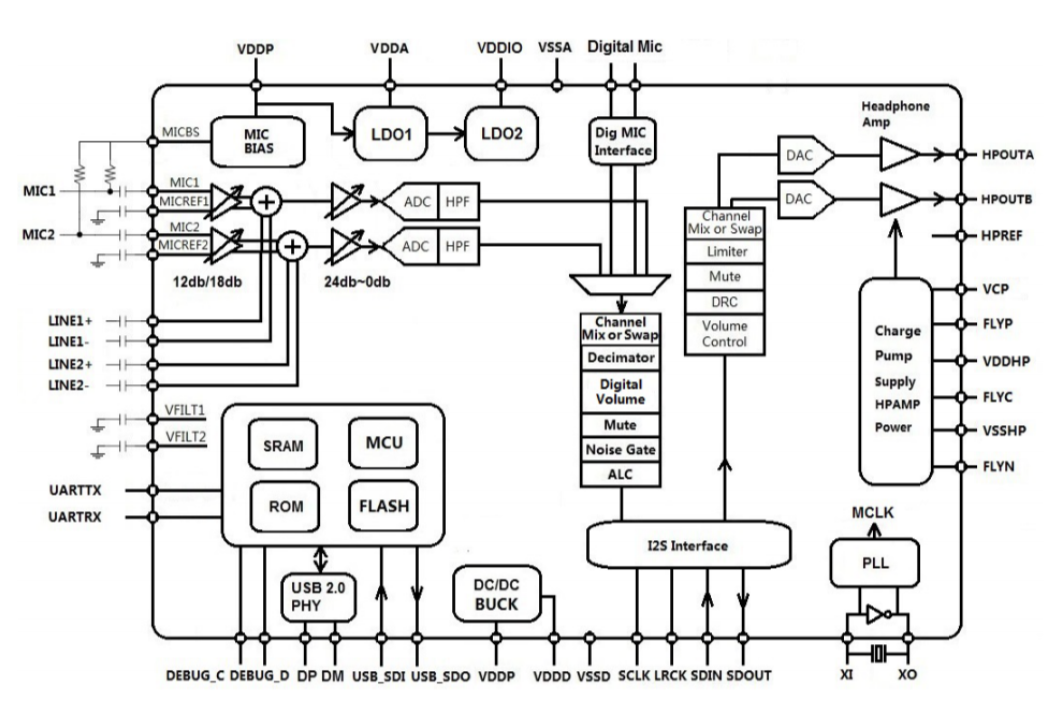

高度集成和低成本的USB aduio CODEC解決方案,為USB Type-C耳機應用程序優化;

無電容直接驅動Headphone,信號幅度高,功耗低;

2023-07-01 16:52:14 2012

2012

電子發燒友網站提供《Versal Premium ACAP:在靈活應變的平臺上突破性集成功耗優化的網絡IP.pdf》資料免費下載

2023-09-15 10:48:04 0

0 MEMS器件的功能需求和技術指標,如靈敏度、精度、穩定性、功耗等。 這些指標將指導后續的設計和優化工作。 采用模塊化設計 : 將MEMS系統劃分為多個功能模塊,如傳感模塊、執行模塊、接口模塊等。 每個模塊可以獨立進行優化和測試,提高整

2024-11-20 10:21:30 2023

2023 RakSmart服務器的成本優化需圍繞硬件配置、網絡資源、IP管理、隱性支出四大核心模塊展開,結合業務階段制定靈活方案。以下是具體策略與實操指南,主機推薦小編為您整理發布RakSmart服務器成本優化策略。

2025-04-10 10:23:04 596

596 這款名為IP6822的無線充電芯片,通過高集成度特性解決了傳統無線充電模組體積臃腫的痛點,全面支持WPC QI標準中的BPP、EPP等規范,支持0.5mm精度的空間適應性。其在消費電子、TWS耳機、工業級應用等場景的充電體驗有著顯著改善。

2025-05-17 08:58:00 455

455

在物聯網應用中,攝像頭硬件設計需兼顧成本控制與功耗優化。本文聚焦低成本、低功耗場景,從傳感器選型、電路設計到電源管理,分享實用技巧,助您解鎖高性價比攝像頭方案,滿足物聯網終端長續航、輕量化需求

2025-09-19 19:19:03 318

318

電子發燒友App

電子發燒友App

評論