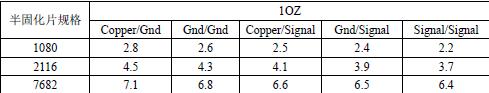

由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。

2023-07-18 09:22:31 2160

2160

隨著高速信號傳輸,對高速PCB設(shè)計提出了更高的要求,阻抗控制是高速PCB設(shè)計常規(guī)設(shè)計,PCB加工十幾道工序會存在加工誤差,當(dāng)前常規(guī)板廠阻抗控制都是在10%的誤差。理論上,這個數(shù)值是越小越好

2023-06-25 10:05:15 1725

1725

可控阻抗是由PCB跡線及其相關(guān)參考平面形成的傳輸線的特性阻抗。當(dāng)高頻信號在PCB傳輸線上傳播時,它是相關(guān)的。控制阻抗對于解決信號完整性問題,即無失真的信號傳播。

2023-09-28 10:01:01 5134

5134

的電路里,對交流電所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡單相加。阻抗的單位是歐姆。 PCB中的阻抗是指電路板上導(dǎo)線、電源、負載和其他元件之間的電阻抗。PCB阻抗控制是設(shè)計PCB電路板的重要

2024-01-03 08:40:18 2090

2090

。

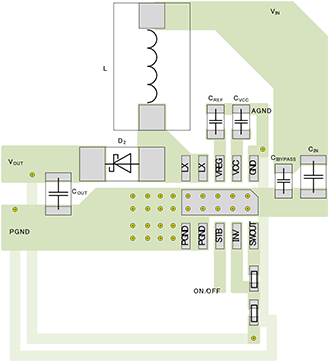

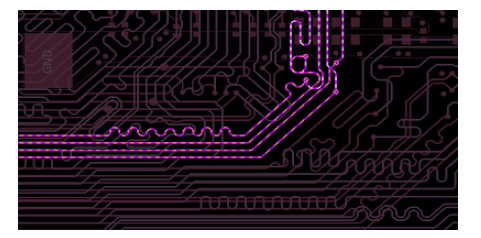

布局對于大型系統(tǒng)板上的嵌入式 DC /DC電源,電源輸出應(yīng)位于負載設(shè)備附近,以最大程度地減小互連阻抗和整個系統(tǒng)上的傳導(dǎo)電壓降 PCB走線可實現(xiàn)最佳的電壓調(diào)節(jié),負載瞬態(tài)響應(yīng)和系統(tǒng)效率。

此外,大型

2025-04-29 14:00:52

因素,并且將其降級到板上所剩的空間,那么這肯定無助于確保高效且可靠的電源設(shè)計。層的放置在多層 PCB板上,非常需要將 DC接地層或 DC輸入或輸出電壓層放置在高電流功率組件層和敏感的小信號走線層之間

2020-09-24 12:21:18

傳輸過程中的質(zhì)量且實現(xiàn)最佳的信號傳輸效果。 PCB上常用50Ω阻抗主要有以下6個原因: 1. 信號傳輸?shù)囊恢滦裕?0Ω阻抗可以匹配常用高速信號傳輸線材料的特性阻抗,并且可以保證信號在整個傳輸線上具有

2023-04-14 16:41:14

,不久以后,在象Hewlett-Packard這樣在業(yè)界占統(tǒng)治地位的公司的影響下,歐洲人也被迫改變了,所以50歐姆最終成為業(yè)界的一個標(biāo)準(zhǔn)沿襲下來,也就變成約定俗成了,而和各種線纜連接的PCB,為了阻抗的匹配,最終也是按照50歐姆阻抗標(biāo)準(zhǔn)來要求了。

2019-06-04 07:51:57

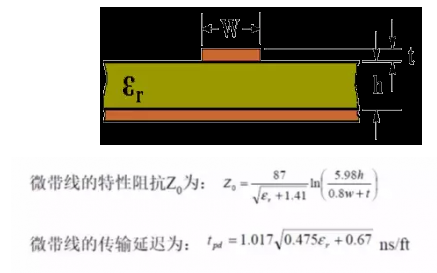

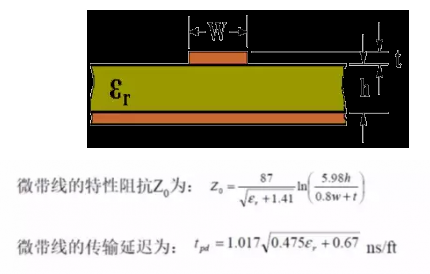

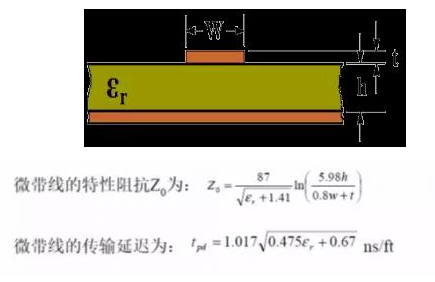

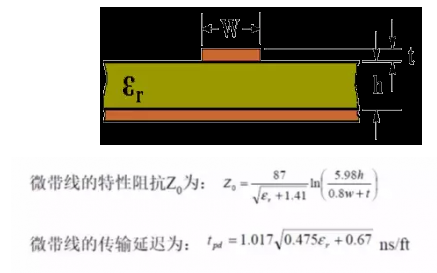

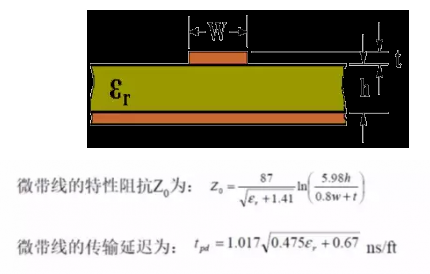

時一定要對板上走線的阻抗進行控制,才能盡可能避免信號的反射以及其他電磁干擾和信號完整性問題,保證PCB板的實際使用的穩(wěn)定性。PCB板上微帶線和帶狀線阻抗的計算方法可參照相應(yīng)的經(jīng)驗公式。 五、印制電路板

2018-09-18 15:50:04

PCB板阻抗設(shè)計:阻抗線有無參考層阻抗如何變化?生產(chǎn)PCB時少轉(zhuǎn)彎的阻抗線的阻抗更容易控制穩(wěn)定性?

2023-04-10 17:03:31

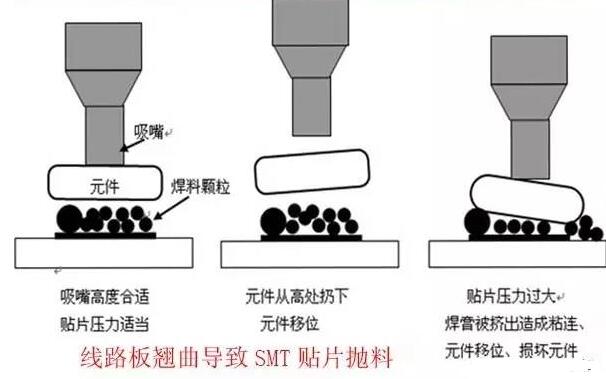

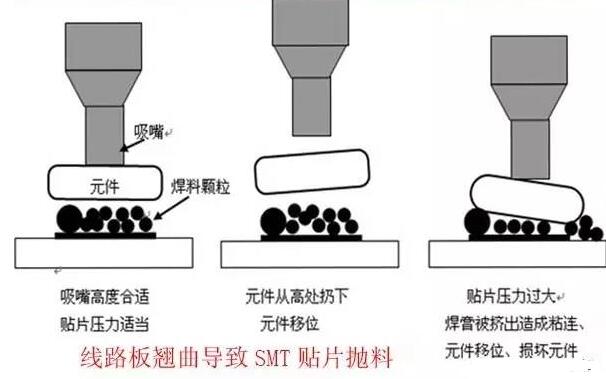

PCB板對貼裝壓力控制的要求是什么對貼裝精度及穩(wěn)定性的要求芯片裝配工藝對貼裝設(shè)備的要求對照像機和影像處理技術(shù)的要求對板支撐及定位系統(tǒng)的要求

2021-04-25 06:35:35

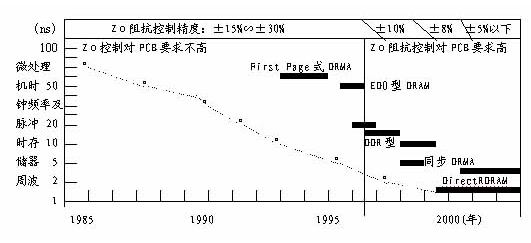

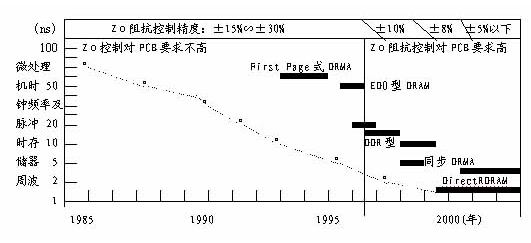

(Delay)等問題,嚴(yán)重時會傳錯信 號,死機。 3、緣由三 嚴(yán)格選擇板材和控制生產(chǎn)流程,多層板上的Z0 才能符合 客戶所要求的規(guī)格。元件的電子阻抗越高時,其傳輸速度才會越快,因而 PCB的Z0 也要隨之

2018-09-14 16:21:15

本文具體分析了PCB板的特性阻抗和特性阻抗的控制辦法。

2021-04-25 07:27:35

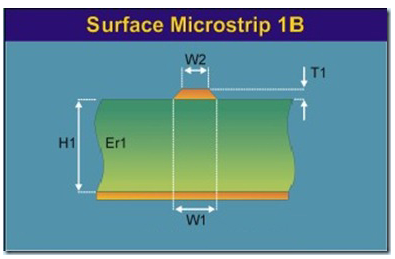

在實際情況中,需要在數(shù)字邊際速度高于1ns或模擬頻率超過300Mhz時控制跡線阻抗。PCB 跡線的關(guān)鍵參數(shù)之一是其特性阻抗(即波沿信號傳輸線路傳送時電壓與電流的比值)。印制電路板上導(dǎo)線的特性阻抗

2019-05-30 07:18:53

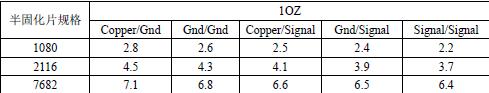

上比較難滿足:過高的阻抗又需要較細的線寬及較厚的介質(zhì)或較小的介電常數(shù),不利于EMI及串?dāng)_的抑制,同時對于多層板及從量產(chǎn)的角度來講加工的可靠性會比較差。控制50歐姆阻抗在使用常用板材(FR4等)、常用芯

2023-04-11 10:32:34

PCB做板阻抗要求計算

2015-03-02 16:46:50

,這個阻抗也要控制在公差以內(nèi),否則,只有報廢、返工。對于有阻抗控制要求的板,目前,PCB工廠比較常見的做法就是在PCB的生產(chǎn)拼版板邊適當(dāng)位置設(shè)計一些阻抗試樣,這些阻抗試樣具有與PCB相同的分層和阻抗線

2015-03-05 14:56:39

搭載RIA的計算機產(chǎn)品,而且很多的電子產(chǎn)品也需要基板上的電路能很好地與之匹配,一些客戶相應(yīng)使用的 PCB 板件的特性阻抗控制精度不在局限于原來的±15%或士10%,有的阻抗控制精度要求提高到±8%甚至

2023-09-21 06:14:35

起著阻礙作用。在PCB加工中,阻抗處理是必不可少的。

1.PCB線路板要考慮接插安裝電子元件,接插后考慮導(dǎo)電性能和信號傳輸性能等問題,所以就會要求阻抗越低越好

2.PCB線路板在生產(chǎn)過程中要經(jīng)歷沉銅

2023-06-01 14:53:32

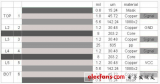

信號層直接相鄰,以減少串?dāng)_。 主電源盡可能與其對應(yīng)地相鄰,構(gòu)成平面電容,降低電源平面阻抗。 兼顧層壓結(jié)構(gòu)對稱,利于制板生產(chǎn)時的翹曲控制。 以上為層疊設(shè)計的常規(guī)原則,在實際開展層疊設(shè)計時,PCB

2023-04-12 15:12:13

越小,同時藕合線長度盡量減短。 同一層上的信號線改變方向時應(yīng)該避免直角拐彎,盡可能走斜線,且曲率半徑大些的好。導(dǎo)線的分布應(yīng)考慮均勻、美觀。 2. 走線寬度和中心距 PCB板線條的寬度要求盡量一致

2012-10-23 10:39:25

為什么說控制阻抗在對PCB線路板如此重要?

2023-04-14 15:09:13

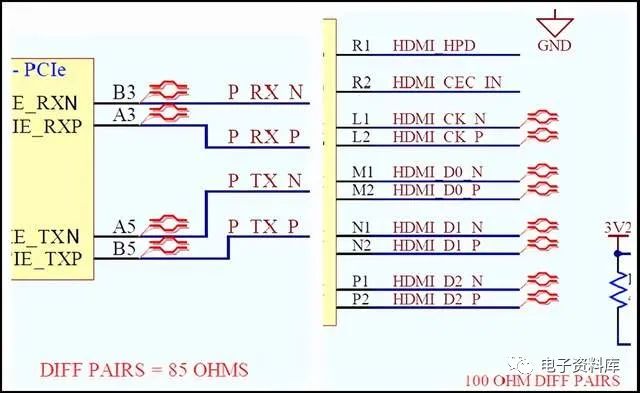

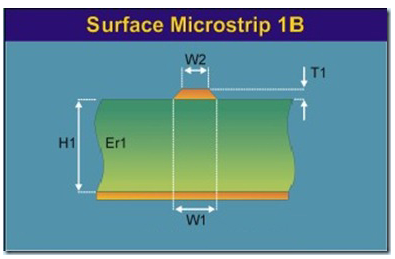

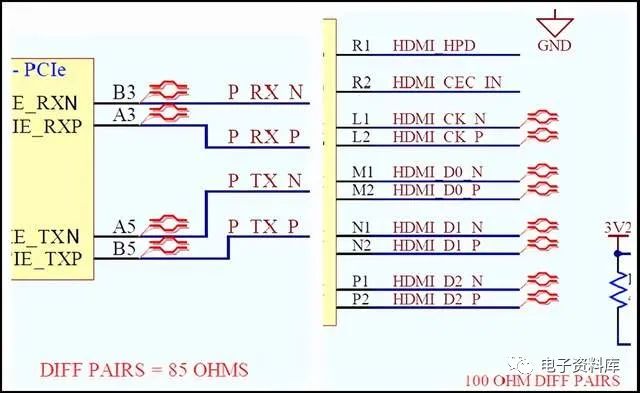

越小其特性阻抗越低(差分阻抗與差份線隊之間的間距成反比)。差分傳輸線特性阻抗通常情況下為100Ω,有時也用到75Ω。考慮到多層PCB板生產(chǎn)時PCB跡線可分布于表面或者內(nèi)層,這兩種情況下PCB跡線

2009-09-28 14:48:47

pcb線路板阻抗是指電阻和對電抗的參數(shù),對交流電所起著阻礙作用。在pcb線路板生產(chǎn)中,阻抗處理是必不可少的。原因如下: 1、PCB線路(板底)要考慮接插安裝電子元件,接插后考慮導(dǎo)電性能和信號傳輸

2023-06-26 15:38:22

如何讓PCB板上的阻抗越小?是線路越寬線的路徑越短阻抗越小嗎?

2023-04-12 15:30:12

實現(xiàn)阻抗控制的傳輸線配置方式控制阻抗 PCB 通常使用微波傳輸帶或帶狀線傳輸線路,以單端(未平衡)或差分(已平衡)配置的方式生產(chǎn)。單端配置以下為幾種常見單端微波傳輸帶和帶狀線傳輸帶的配置:注意以下各

2009-09-28 16:16:56

/接口電路PCB打板:軟件算法:通信協(xié)議:硬件和軟件可靠性分析:工業(yè)控制板開發(fā)的原因替代PLC 不可能完成的任務(wù),突破某個功能在速度或是數(shù)量上的限制,特殊的功能要求或是須要降低成本。博主在工控板方面積累了相當(dāng)?shù)慕?jīng)驗,現(xiàn)在就為新手們鋪下路吧。PCB畫板軟件:AD ( Altium Designer )硬件

2021-08-23 06:51:29

制作的線路板的銅線),相對某一參考層(也就是常說的屏蔽層、影射層或參考層),其高頻信號或電磁波在傳播過程中所受的阻力稱之為特性阻抗,它實際上是電阻抗、電感抗、電容抗等一個矢量總和。2、控制PCB

2016-10-10 14:38:27

pcb板阻抗與導(dǎo)線長度有關(guān)嗎?在對FR的天線進行阻抗計算時,對天線的長度有要求嗎?我舉個例子哦。比如說做讀卡器的天線:在板上我們畫了一圈一圈的導(dǎo)線做板載天線。這個我們要畫多少圈最合適?我知道天線

2019-01-30 03:51:45

的相對位置。特性阻抗要求的差分對間的線寬/線距則取決于選擇的PCB疊層結(jié)構(gòu)。

由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實現(xiàn)板上的所有阻抗需求,包括內(nèi)層

2023-05-26 11:30:36

影響印刷電路板(PCB板)的特性阻抗因素及對策:本文給出了印刷電路板PCB特性阻抗的定義,分析了影響特性阻抗的因素及PCB的構(gòu)造參數(shù)對特性阻抗精度的影響,最后給出了一些對

2009-03-25 15:39:37 0

0 越來越多的廠商要求指定PCB板上的DC跡線阻抗。以下從設(shè)計商的角度道出了指定和

2006-04-16 20:23:26 832

832 電鍍鎳金板不上錫原因分析,請從以下幾方面作檢查調(diào)整: 1. 電

2006-04-16 21:56:04 2802

2802 PCB跡線的阻抗控制簡介

PCB上的阻抗控制電信和計算機設(shè)備操作的速度和切換速率正在不斷增長。盡管在低頻情況下,這是一個可以

2009-09-28 14:42:44 1657

1657 傳輸線阻抗計算中的有關(guān)問題

結(jié)合目前我公司PCB板加工廠家的工藝能力,在用polar公司阻抗計算器CITS25計算PCB板上跡線特性阻抗時,

2009-09-28 14:54:20 2386

2386

PCB線路板斷線現(xiàn)象的原因分析

首先看看斷線的形式,

2009-09-30 09:32:51 6460

6460 阻抗控制最終需要通過PCB設(shè)計實現(xiàn),對PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,我對這個問題有了一些粗淺的認識,愿和大家分享。

2011-05-06 11:28:46 4711

4711

隨著PCB 信號切換速度不斷增長,當(dāng)今的PCB 設(shè)計廠商需要理解和控制PCB 跡線的阻抗。相應(yīng)于現(xiàn)代數(shù)字電路較短的信號傳輸時間和較高的時鐘速率,PCB 跡線不再是簡單的連接,而是傳輸線。

2016-03-24 14:48:57 0

0 PCB板DFX工藝性要求PCB板DFX工藝性要求

2016-07-26 16:29:36 0

0 pcb打板工藝要求

2016-12-09 15:19:10 19

19 導(dǎo)線的長度接近信號波長的1/7, 此時的導(dǎo)線便成為信號傳輸線,一般信號傳輸線均需做阻抗控制。PCB制作時,依客戶要求決定是否需管控阻抗,若客戶要求某一線寬需做阻抗控制,生產(chǎn)時則需管控該線寬的阻抗。

2017-07-27 11:20:07 0

0 隨著 PCB 信號切換速度不斷增長,當(dāng)今的 PCB 設(shè)計廠商需要理解和控制 PCB 跡線的阻抗。相應(yīng)于現(xiàn)代數(shù)字電路較短的信號傳輸時間和較高的時鐘速率,PCB 跡線不再是簡單的連接,而是傳輸線。 在

2017-11-26 14:28:01 1539

1539 阻抗對于PCB電路板的意義何在,PCB電路板為什么要做阻抗?本文首先介紹了什么是阻抗及阻抗的類型,其次介紹了PCB線路板為什么要做阻抗,最后闡述了阻抗對于PCB電路板的意義,具體的跟隨小編一起來了解一下。

2018-05-02 16:25:54 15472

15472

本文首先介紹了PCB板變形的危害,其次分析了產(chǎn)生PCB板變形的原因,最后闡述了如何改善PCB變形的措施,具體的跟隨小編一起來了解一下。

2018-05-24 18:01:04 19905

19905

PCB設(shè)計實現(xiàn),對PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號完整性要求去控制走線的阻抗。

2018-10-14 09:28:00 1929

1929 基于多層板介質(zhì)層厚度對阻抗的影響,了解其均勻性分布及掌握其控制方法對阻抗產(chǎn)品阻抗控制至關(guān)重要。本文從PCB層壓介質(zhì)層設(shè)計及層壓工藝相關(guān)控制點著手探究介質(zhì)厚度均勻性的控制方法,指出提升介質(zhì)厚度匹準(zhǔn)度以滿足阻抗設(shè)計要求的有效途徑。

2018-11-03 10:13:40 5207

5207 PCB跡線的阻抗將由其感應(yīng)和電容性電感、電阻和電導(dǎo)系數(shù)確定。影響PCB走線的阻抗的因素主要有: 銅線的寬度、銅線的厚度、介質(zhì)的介電常數(shù)、介質(zhì)的厚度、焊盤的厚度、地線的路徑、走線周邊的走線等。PCB阻抗的范圍是 25 至120 歐姆。

2019-08-08 15:23:43 5235

5235

。不僅搭載RIMM的計算機產(chǎn)品,而且很多的電子產(chǎn)品也需要基板上的電路能很好地與之匹配,一些客戶相應(yīng)使用的PCB板件的特性阻抗控制精度不在局限于原來的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,這對PCB制造廠來說確實是很大的挑戰(zhàn)。

2019-05-21 14:47:01 1444

1444

我的第一塊PCB遠離高速數(shù)字設(shè)備。它只是單層PCB上的放大器電路,控制阻抗甚至不是事后的想法。一旦我開始研究需要高采樣率的電光系統(tǒng),控制阻抗始終是一個關(guān)鍵的設(shè)計問題。電路板上的受控阻抗是PCB布局問題,我在處理PCB一段時間后感覺不太舒服。

2019-07-25 09:13:38 2686

2686 阻抗控制線是否會增加PCB板的成本?是的,會增加PCB的制造成本設(shè)計。但是,有3個主要元素可以控制PCB制造成本。

2019-07-31 11:09:56 3963

3963 、PCB供應(yīng)商反饋信息等,而最終得出此推薦設(shè)計。適用于大部分PCB供應(yīng)商的制程工藝標(biāo)準(zhǔn)和具有阻抗控制要求的PCB板設(shè)計。

2019-08-01 17:45:55 0

0 隨著 PCB 信號切換速度不斷增長,當(dāng)今的 PCB 設(shè)計廠商需要理解和控制 PCB 跡線的阻抗。

2019-08-30 08:45:40 3859

3859 印制電路板上導(dǎo)線的特性阻抗是電路設(shè)計的一個重要指標(biāo),特別是在高頻電路的PCB設(shè)計中,必須考慮導(dǎo)線的特性阻抗和器件或信號所要求的特性阻抗是否一致,是否匹配。

2019-09-02 17:04:08 3364

3364 阻抗控制最終需要通過PCB設(shè)計實現(xiàn),對PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號完整性要求去控制走線的阻抗。

2019-09-06 11:52:29 13584

13584

PCB設(shè)計實現(xiàn),對PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號完整性要求去控制走線的阻抗。

2019-10-04 17:17:00 11739

11739

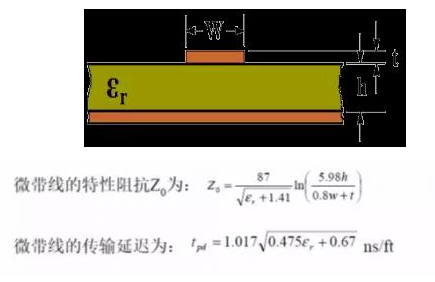

常見的信號,如PCI總線、PCI-E總線、USB、以太網(wǎng)、DDR內(nèi)存、LVDS信號等,均需要進行阻抗控制。阻抗控制最終需要通過PCB設(shè)計實現(xiàn),對PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號完整性要求去控制走線的阻抗。

2019-12-31 15:42:08 3012

3012

PCB線路板阻抗,指的是電阻和對電抗的參數(shù),對交流電所起著阻礙作用。在PCB線路板生產(chǎn)中,阻抗處理是必不可少的,PCB線路板為什么要做阻抗?

2020-02-24 11:02:21 5853

5853 設(shè)計實現(xiàn),對PCB板工藝也提出更高要求,經(jīng)過與PCB廠的溝通,并結(jié)合EDA軟件的使用,按照信號完整性要求去控制走線的阻抗。

2020-07-14 10:25:00 6

6 對于模擬或高頻數(shù)字電路,確保在PCB板上傳播的信號的完整性至關(guān)重要。實際上,高于100 MHz的信號會受到導(dǎo)體走線的 阻抗 的影響,如果不加以適當(dāng)考慮,則會導(dǎo)致不便的錯誤,并且特別難以分析。幸運

2020-09-03 19:04:58 7793

7793 還可以確保沿著互連的一致的傳播延遲,從而允許并行高速 PCB 信號(例如 PCIe 中的信號)的長度精確匹配以防止歪斜。 由于阻抗控制的布線需要精確制造 PCB 互連件,因此制造商已花費大量精力完善蝕刻工藝,以確保跡線幾何形狀與 PCB 設(shè)計軟件中使用

2020-09-25 18:59:16 2410

2410 跡線阻抗控制是正確確定跡線大小的簡單問題。當(dāng)單獨考慮一條走線時,其阻抗將具有明確定義的值。但是,當(dāng)靠近另一個走線或?qū)w時,由于意外耦合,走線的阻抗將不同于其設(shè)計值。這種令人討厭的事實會導(dǎo)致沿互連

2021-02-13 07:06:00 2057

2057

在 PCB 設(shè)計階段要注意阻抗控制,這一點很重要。阻抗控制涉及為 PCB 上的走線和傳輸線指定所需的阻抗。這對于高速信號尤其重要,并且可能會受到您的影響。基材,銅線寬度和布線。即使在布置好電路板并

2020-10-09 21:12:57 2063

2063 更高速的動作。不僅搭載 RIMM 的計算機產(chǎn)品,而且很多的電子產(chǎn)品也需要基板上的電路能很好地與之匹配,一些客戶相應(yīng)使用的 PCB 板件的特性阻抗控制精度不在局限于原來的±15%或±10%,有的阻抗控制精度要求提高到±8%甚至±5%,這對 PCB 制造廠來說確實是很大的挑戰(zhàn)。本文主要針對如何滿足客戶

2023-02-03 14:02:05 1919

1919 在PCB制造中,跡線代表導(dǎo)體,層壓板代表絕緣體,平面代表屏蔽。因此,印刷電路板的阻抗取決于制造過程中使用的尺寸和材料。

2021-02-27 10:26:01 3249

3249 最近設(shè)計了一塊四層板pcb,因為是高速電路,有阻抗匹配的要求,所以在發(fā)給pcb板廠打樣時,特定指定了哪些線要做

2020-12-07 12:08:23 23811

23811 PCB布線短是為了盡量忽略信號在傳輸過程中的反射,那為什么會產(chǎn)生反射呢?

實際上反射的原因是互連線中阻抗發(fā)生了突然變化,那什么叫做阻抗,影響阻抗的因素又是什么呢?

通俗來講:傳輸線上某一點處的電壓與電流的比值表示在這個位置信號感受到的阻抗。

2021-01-05 17:02:00 35

35 PCB工程師在設(shè)計PCB時,對于高速電路板或電路板上的關(guān)鍵信號會經(jīng)常涉及到到“做阻抗”、“阻抗匹配“的這些問題。 首先解釋下什么是阻抗匹配: 阻抗要求是為確保電路板上高速信號的完整性而提出,它對高速

2021-11-15 11:00:14 18240

18240 在 STM32 無線系列產(chǎn)品的 PCB 設(shè)計中,需要對射頻部分電路進行阻抗控制,良好的阻抗控制可以減少信號衰減、反射和 EMC 輻射。本篇 LAT 主要介紹印制電路板(PCB)上射頻走線阻抗仿真計算

2022-06-16 16:36:21 8873

8873 起來看看 PCB 板之所以會變形的原因。 關(guān)于 PCB 板的變形,可以從設(shè)計、材料、生產(chǎn)過程等幾方面來進行分析,這里簡單地闡述下,供大家參考。? 設(shè)計方面: (1)漲縮系數(shù)匹配性? 一般電路板上都會設(shè)計有大面積的銅箔來當(dāng)作接地之用,有時候 Vcc 層也會有設(shè)計有大面積

2022-06-22 20:13:02 3464

3464 PCB板翹曲的原因或許都不太一樣,但最后應(yīng)該都可以歸咎到施加于PCB板上的應(yīng)力大過了板子材料所能承受的應(yīng)力,當(dāng)板子所承受的應(yīng)力不均勻或是板子上每個地方抵抗應(yīng)力的能力不均勻時,就會出現(xiàn)PCB板翹曲的結(jié)果。

2022-09-07 16:24:06 3898

3898 想要制作出一塊完整的PCB板,需要經(jīng)過多個繁瑣復(fù)雜的工序,在PCB板生產(chǎn)過程中若是出現(xiàn)一些操作失誤,就會導(dǎo)致最終生產(chǎn)出的成品板子出現(xiàn)質(zhì)量問題,不符合產(chǎn)品要求。一般常見的PCB板斷線問題,就會

2022-10-07 09:44:51 1779

1779

、PCB供應(yīng)商反饋信息等,而最終得出此推薦設(shè)計。適用于大部分PCB供應(yīng)商的制程工藝標(biāo)準(zhǔn)和具有阻抗控制要求的PCB板設(shè)計。

2022-10-12 10:23:17 8176

8176 上一篇文章中,我們介紹了在進行升壓型DC/DC轉(zhuǎn)換器的安裝PCB板布局時的基本思路,即與開關(guān)相關(guān)的電流路徑。本文將在分別進行升壓型DC/DC轉(zhuǎn)換器的PCB板布局的解說之前,先介紹升壓型DC/DC轉(zhuǎn)換器的PCB板布局的整體步驟和要點。

2023-02-22 18:13:42 2453

2453

一站式PCBA智造廠家今天為大家講講PCB制板電鍍分層是什么原因?PCB制板電鍍分層原因分析。在PCB制板過程中,會有很多意外的情況發(fā)生,比如電鍍銅、化學(xué)鍍銅、鍍金、鍍錫鉛合金等鍍層分層。那么導(dǎo)致

2023-05-25 09:36:54 2627

2627 上周推文《如何判斷PCB板是否變形?》,華秋干貨鋪為大家解析了如何判斷PCB板是否變形。那么,現(xiàn)在再一起來看看PCB板之所以會變形的原因。PCB板變形原因分析關(guān)于PCB板的變形,可以從設(shè)計、材料

2022-06-10 11:46:43 2097

2097

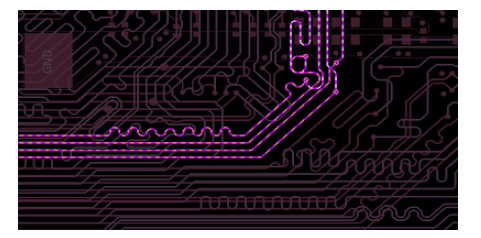

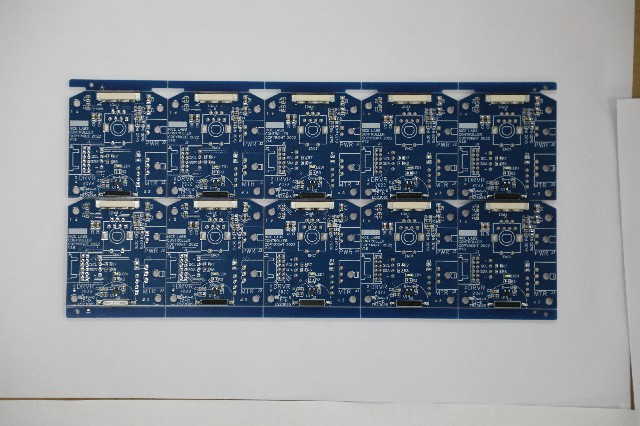

1.什么是阻抗線路板?對于PCB工廠而言,有阻抗線的板我們俗稱為阻抗板,如下圖所示,是我們常見的阻抗板的其中之一。通常高速板才會做阻抗,且阻抗線在生產(chǎn)過程中線寬公差要控制到5%-10%,非阻抗線則是

2022-06-17 09:16:28 2635

2635

隨著高速信號傳輸,對高速 PCB設(shè)計提出了更高的要求,阻抗控制是高速PCB設(shè)計常規(guī)設(shè)計,PCB加工十幾道工序會存在加工誤差,當(dāng)前常規(guī)板廠阻抗控制都是在10%的誤差。理論上,這個數(shù)值是越小越好

2023-06-22 08:10:02 2753

2753

隨著高速信號傳輸,對高速 PCB設(shè)計提出了更高的要求,阻抗控制是高速PCB設(shè)計常規(guī)設(shè)計,PCB加工十幾道工序會存在加工誤差,當(dāng)前常規(guī)板廠阻抗控制都是在10%的誤差。理論上,這個數(shù)值是越小越好

2023-06-27 08:10:03 3129

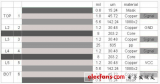

3129 決于選擇的PCB疊層結(jié)構(gòu)。由于最小線寬和最小線距是取決于PCB類型以及成本要求,受此限制,選擇的PCB疊層結(jié)構(gòu)必須能實現(xiàn)板上的所有阻抗需求,包括內(nèi)層和外層、單端和差分線等。 一、PCB疊層設(shè)計 層的定義設(shè)計原則: 1)主芯片相臨層

2023-08-01 07:45:01 3865

3865

導(dǎo)致最終生產(chǎn)出的成品板子出現(xiàn)質(zhì)量問題,不符合產(chǎn)品要求。一般常見的PCB板斷線問題,就會影響線路板功能的實現(xiàn)。 那么,PCB板斷線是什么原因造成的?接下來深圳PCB制板廠家為大家介紹下一些導(dǎo)致PCB板斷線的原因: 1、貼膜的工序:貼膜貼的不牢固,出現(xiàn)了氣

2023-08-15 09:18:56 2622

2622 現(xiàn)不良現(xiàn)象。本文將詳細介紹PCB板的常見不良現(xiàn)象及分析,以便讀者更好地理解和解決相關(guān)問題。 一、PCB板的不良現(xiàn)象 1. 短路:在電路板中,兩個或多個回路之間發(fā)生了非預(yù)期的電氣連接,導(dǎo)致短路現(xiàn)象。短路原因可能是板上布線或焊接時的接觸不良、

2023-08-29 16:35:19 6445

6445 不良,將嚴(yán)重影響電子設(shè)備整體性能,并有可能造成設(shè)備故障。本文將詳細介紹PCB板短路分析的方法。 1. 短路不良的原因 PCB的短路不良是指電路板上必須分開布線的兩個或多個信號線或信號線與地線之間出現(xiàn)了短路現(xiàn)象。造成PCB板短路的原因有以下幾點: (

2023-08-29 16:46:19 4041

4041 一站式PCBA智造廠家今天為大家講講PCB板板面起泡的原因有哪些?PCB板板面起泡的原因分析。板面起泡是PCB生產(chǎn)過程中常見的質(zhì)量缺陷之一。由于PCB生產(chǎn)工藝的復(fù)雜性,很難防止板面發(fā)泡缺陷。那么,PCB表面起泡的原因有哪些呢?接下來深圳PCB板生產(chǎn)廠家為大家介紹下。

2023-09-05 09:44:03 2408

2408 經(jīng)常測試阻抗的朋友應(yīng)該知道,當(dāng)PCB板Trace走線較長時,測試阻抗 結(jié)果會出現(xiàn)末端上飄現(xiàn)象。

2023-09-07 16:50:14 4362

4362

阻抗控制pcb

2023-09-18 10:40:37 1726

1726 電路板中的PCB阻抗CBA

2023-10-13 11:15:19 1966

1966 關(guān)于PCB板的變形,可以從設(shè)計、材料、生產(chǎn)過程等幾方面來進行分析,下載資料了解詳情。

2022-09-30 11:54:36 19

19 造成pcb板開裂原因分析

2023-11-16 11:01:24 4198

4198 pcb電路板阻抗設(shè)計,確保最佳性能

2023-12-28 10:27:22 1377

1377 ,對交流電所起的阻礙作用叫做阻抗。阻抗常用Z表示。阻抗由電阻、感抗和容抗三者組成,但不是三者簡單相加。阻抗的單位是歐姆。 PCB中的阻抗是指電路板上導(dǎo)線、電源、負載和其他元件之間的電阻抗。PCB阻抗控制是設(shè)計PCB電路板的重要環(huán)節(jié),以

2024-01-05 08:45:02 1875

1875

pcb板阻抗控制是指什么?pcb怎么做阻抗? PCB板阻抗控制是指在PCB(印刷電路板)設(shè)計和制造過程中,通過優(yōu)化電氣特性和信號完整性,確保設(shè)計滿足特定的阻抗要求。在高速數(shù)字和模擬電路中,阻抗控制

2024-01-17 16:38:04 5037

5037 一站式PCBA智造廠家今天為大家講講PCBA線路板中的阻抗特性與受控阻抗是什么?PCB阻抗特性與受控阻抗原理。在PCBA線路板中,阻抗特性和受控阻抗是重要的概念,特別在高頻和高速電路設(shè)計中。 PCB

2024-06-26 09:20:05 2252

2252

高頻阻抗PCB 板的核心特點在于其對阻抗的精確控制。阻抗是指在交流電路中,對電流的阻礙作用。在高頻信號傳輸中,阻抗的匹配與否直接影響著信號的質(zhì)量和傳輸效率。

2024-08-20 17:22:51 1123

1123 阻抗控制的主要目的是為了保證電路板信號的穩(wěn)定傳輸,提高信號傳輸質(zhì)量。阻抗是電路板傳輸信號時的主要參數(shù)之一,其取值與電路板材料、線路結(jié)構(gòu)、電信號頻率等相關(guān)。 PCB電路板的阻抗工藝中控制要點: 1.

2024-09-23 14:37:17 1402

1402 什么意思呢?本文將深入探討這一話題,幫助大家更好地理解PCB阻抗及其在電子設(shè)備設(shè)計中的重要性。 什么是阻抗? 阻抗是電路對交流電流的阻礙作用,它是一個復(fù)數(shù),包含電阻和電抗兩部分。電抗又可以分為容抗和感抗。在印制板上,阻抗主要由導(dǎo)線、絕緣介質(zhì)以及

2024-11-13 09:20:40 2541

2541

,作為影響信號傳輸質(zhì)量的關(guān)鍵因素之一,是高質(zhì)量電路板設(shè)計不可或缺的技術(shù)。 什么是PCB阻抗控制? PCB(Printed Circuit Board)阻抗控制,是指在電路板設(shè)計過程中,通過調(diào)節(jié)布線、材料等參數(shù),控制傳輸線的特性阻抗,以保證信號的完整性。所謂特性阻抗,是

2025-04-18 09:07:47 823

823

電子發(fā)燒友App

電子發(fā)燒友App

評論