高并發(fā)和響應(yīng)快對應(yīng)著性能優(yōu)化的兩個核心指標(biāo):吞吐和延時

2022-11-21 11:23:20 1068

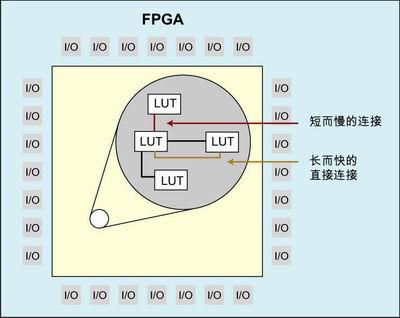

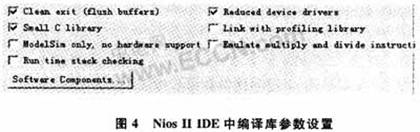

1068 綜合就是把Verilog、VHDL轉(zhuǎn)換成網(wǎng)表的過程。綜合按照是否考慮物理布局信息可分為邏輯綜合和物理綜合。

2023-08-09 09:51:15 1867

1867

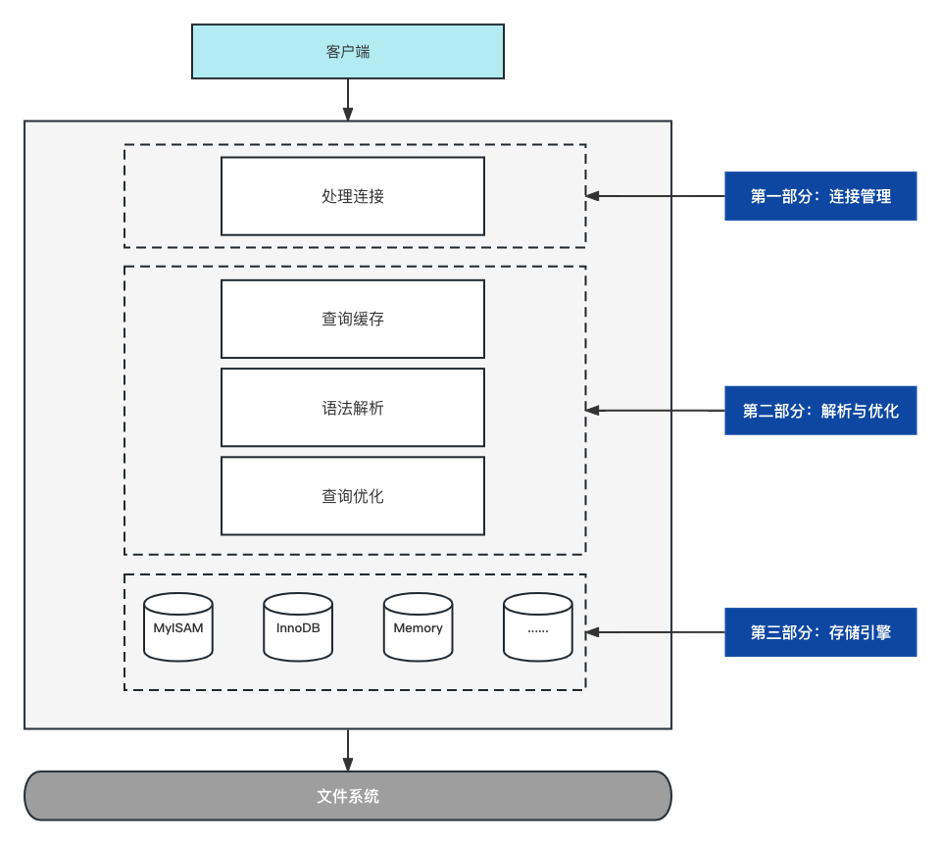

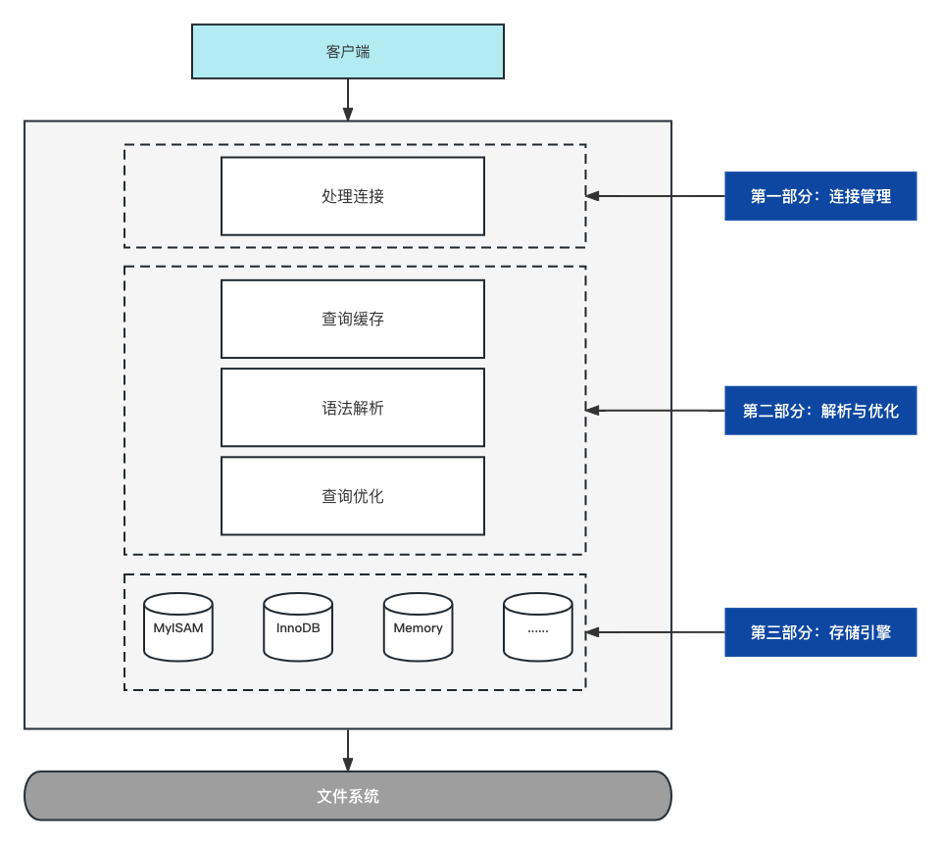

作者:京東健康 孟飛 1、 數(shù)據(jù)庫性能優(yōu)化的意義 業(yè)務(wù)發(fā)展初期,數(shù)據(jù)庫中量一般都不高,也不太容易出一些性能問題或者出的問題也不大,但是當(dāng)數(shù)據(jù)庫的量級達(dá)到一定規(guī)模之后,如果缺失有效的預(yù)警、監(jiān)控、處理等

2024-10-22 15:17:21 1349

1349

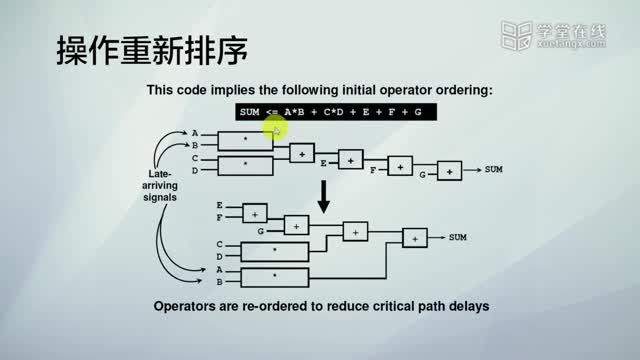

優(yōu)化 FPGA HLS 設(shè)計

用工具用 C 生成 RTL 的代碼基本不可讀。以下是如何在不更改任何 RTL 的情況下提高設(shè)計性能。

介紹

高級設(shè)計能夠以簡潔的方式捕獲設(shè)計,從而

2024-08-16 19:56:07

優(yōu)化電動汽車的結(jié)構(gòu)性能以提高效率和安全性迅速增長的全球電動汽車(EV)市場預(yù)計到2027年將達(dá)到8028億美元。在電池和高壓電子設(shè)備的驅(qū)動下,電動汽車的運行和維護(hù)成本往往低于傳統(tǒng)汽車,幾乎不會產(chǎn)生

2021-09-17 08:10:07

物理綜合與優(yōu)化的優(yōu)點有哪些物理綜合與優(yōu)化流程看了就知道物理綜合與優(yōu)化示例

2021-04-08 06:18:15

):Xilinx_ISE_DS_Update_13.1_O.40e.2.1Linux平臺:CentOS 5.6(RHEL 5.6克隆)運行物理綜合......FATAL_ERROR:1 :: 78:1.3- 物理綜合失敗。流程將終止。 有關(guān)此問題的技術(shù)支持

2018-10-12 14:28:14

本帖最后由 貪玩 于 2022-2-16 21:42 編輯

AN0004—AT32 性能優(yōu)化這篇應(yīng)用筆記描述了如何通過軟件方法提高AT32的運行效能。AT32 性能優(yōu)化概述性能提升是多方面調(diào)優(yōu)

2020-08-15 14:38:22

Arm AMBA協(xié)議集中,協(xié)議的實現(xiàn)是直接物理綜合而成的嗎?還會有其自身的固件嗎?

2022-09-19 14:52:16

主要由資深HPC工程師(高性能計算優(yōu)化工程師)進(jìn)行開發(fā),為了加快開發(fā)進(jìn)程,縮短深度學(xué)習(xí)應(yīng)用落地周期,自動化算子優(yōu)化是一個趨勢。AutoKernel是由OPEN AI LAB提出的高性能算子自動優(yōu)化工具,可以.

2021-12-14 06:18:21

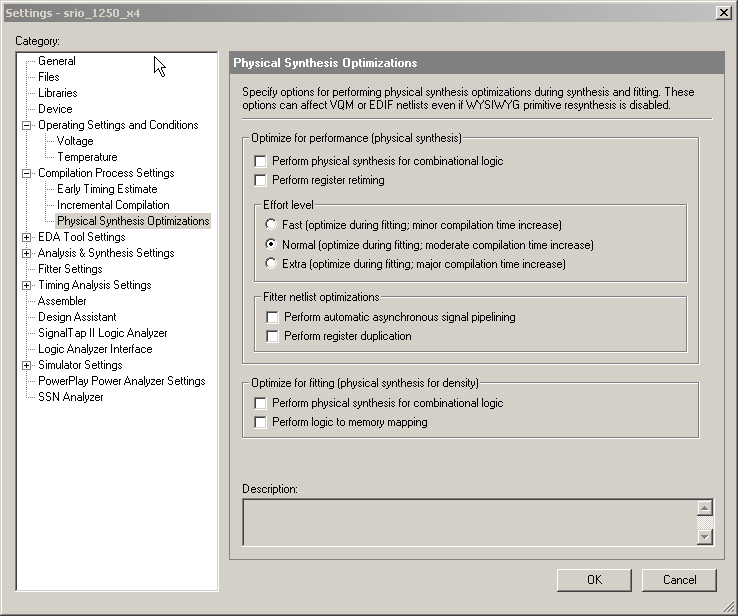

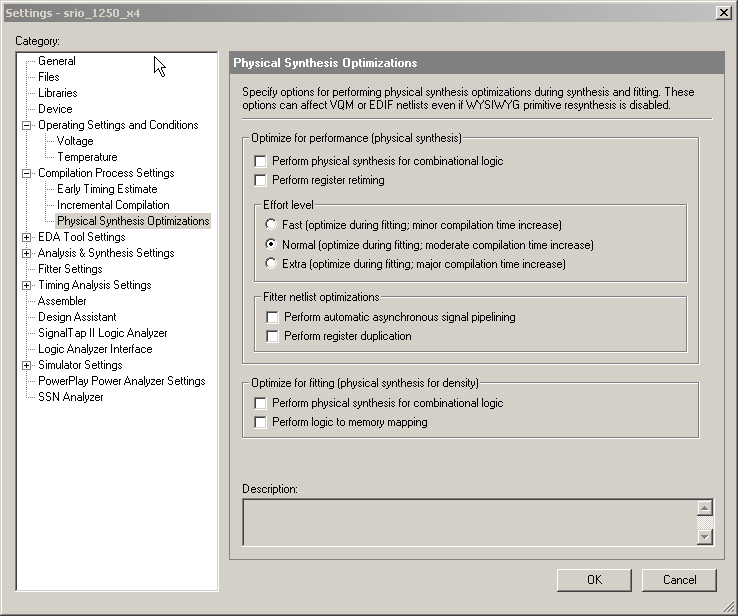

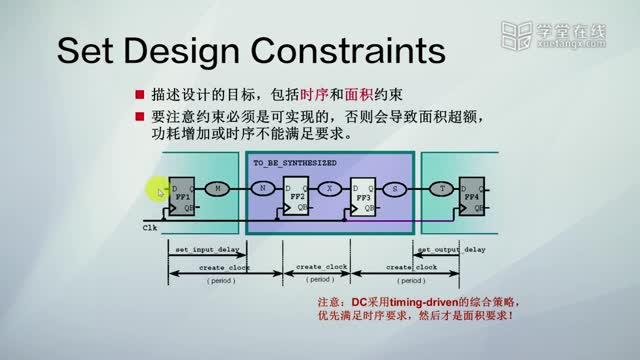

邏輯優(yōu)化、邏輯布局和最小化互連延遲都是實現(xiàn)最大性能的重要工作。1. 定義時序要求:進(jìn)行有效物理綜合的最重要一步是建立準(zhǔn)確全面的時序約束。 有了這些約束,實現(xiàn)工具就基于可靠信息做出決策,從而改善總體

2012-02-24 10:51:12

HBase是Hadoop生態(tài)系統(tǒng)中的一個組件,是一個分布式、面向列的開源數(shù)據(jù)庫,可以支持?jǐn)?shù)百萬列、超過10億行的數(shù)據(jù)存儲,因此,對HBase性能提出了一定的要求,那么如何進(jìn)行HBase性能優(yōu)化呢

2018-04-20 17:16:47

流程概覽

在開發(fā)應(yīng)用時,開發(fā)者會對應(yīng)用的運行情況有一個預(yù)期的指標(biāo),當(dāng)應(yīng)用在某些方面不能滿足預(yù)期的指標(biāo)或者表現(xiàn)不佳時,意味著您的應(yīng)用可能存在性能問題,需要對應(yīng)用進(jìn)行性能優(yōu)化以達(dá)到您的預(yù)期。應(yīng)用的性能

2025-02-19 15:28:10

MySQL優(yōu)化三:查詢性能優(yōu)化之查詢優(yōu)化器的局限性與提示

2020-06-02 06:34:40

Spark SQL(九):工作原理和性能優(yōu)化

2019-06-12 16:21:34

對進(jìn)行時序路徑、工作環(huán)境、設(shè)計規(guī)則等進(jìn)行約束完成之后,DC就可以進(jìn)行綜合、優(yōu)化時序了,DC的優(yōu)化步驟將在下面進(jìn)行講解。然而,當(dāng)普通模式下不能進(jìn)行優(yōu)化的,就需要我們進(jìn)行編寫腳本來改進(jìn)DC的優(yōu)化來達(dá)到

2021-07-30 06:18:54

總的來說,UFS3.0的綜合性能,特別是持續(xù)讀寫速度有著秒殺UFS2.1前輩的表現(xiàn),只是在隨機(jī)讀寫和SQLite性能上,卻依舊和雙通道的UFS2.1持平,有些小遺憾。最后,咱們再來科普一下eMMC

2021-07-22 07:17:09

網(wǎng)站前端性能優(yōu)化之javascript和css

2019-10-21 09:12:27

web常用性能優(yōu)化

2020-06-13 10:57:53

《現(xiàn)代CPU性能分析與優(yōu)化》是一本非常實用的書籍,對于從事性能關(guān)鍵型應(yīng)用程序開發(fā)和進(jìn)行系統(tǒng)底層優(yōu)化的技術(shù)人員來說是不可或缺的。這本書也很適合任何想更好地了解應(yīng)用程序性能并探索其診斷和改進(jìn)方法的開發(fā)者

2023-04-18 16:03:36

很榮幸拿到這本<<現(xiàn)代CPU性能分析與優(yōu)化>>,花了幾天的時間瀏覽了一遍,書比較單薄,正文只有不到200頁,但是里面的內(nèi)容確是非常豐富的,一般

2023-04-24 15:31:26

的負(fù)載條件、補償方式、瞬態(tài)響應(yīng)和效率進(jìn)行綜合考慮,并通過實際測試來驗證調(diào)試結(jié)果。通過這種方法,ASP3605可以被優(yōu)化以滿足各種高性能電源應(yīng)用的需求。

2024-08-23 14:34:46

我們以Imagination新發(fā)布的兩款內(nèi)核產(chǎn)品為例,來分析不同應(yīng)用市場對嵌入式AI的綜合性能指標(biāo)。

2021-01-14 06:53:15

全球出現(xiàn)的能源短缺問題使各國***都開始大力推行節(jié)能新政。電子產(chǎn)品的能耗標(biāo)準(zhǔn)越來越嚴(yán)格,對于電源設(shè)計工程師,如何設(shè)計更高效率、更高性能的電源是一個永恒的挑戰(zhàn)。本文從電源PCB的布局出發(fā),介紹了優(yōu)化

2021-12-28 07:07:59

前端性能優(yōu)化常見方式

2020-03-27 11:42:41

可重構(gòu)平臺下AES算法的流水線性能怎么優(yōu)化?

2021-04-28 06:46:52

ADI公司提供基于單硅芯片的電池化成控制系統(tǒng)綜合解決方案 AD8452。憑借準(zhǔn)確的化成工藝性能,可優(yōu)化每個電池的化成時間。高效的能量回收特性能夠明顯節(jié)省大規(guī)模電池制造的能耗。

2021-01-21 06:27:38

各位高手,我用767做tcp server端,接收PC機(jī)發(fā)過來的數(shù)據(jù)。目前測試大約可以達(dá)到1MB/s,我看網(wǎng)上有人說可以達(dá)到4MB/s。有人測試過嗎?可以在哪里優(yōu)化提高lwip的tcp接收性能?

2019-09-03 23:05:28

物理綜合技術(shù)是數(shù)字電路設(shè)計工程師必須要掌握的一項技能,是RTL到物理實現(xiàn)的起點,而物理綜合是一個很復(fù)雜的過程,環(huán)境、工藝庫設(shè)定、時序約束編寫、綜合時序問題分析等等均需要綜合時具有專門的知識和技能,一

2021-06-23 06:59:32

如何使用MLD優(yōu)化MIMO接收器的性能?

2021-05-24 06:16:55

DC的綜合優(yōu)化階段包括哪幾部分?如何使用compile命令使DC進(jìn)行綜合優(yōu)化設(shè)計呢?

2021-11-03 06:16:04

如何使用基于圖形的物理綜合加快FPGA設(shè)計時序收斂?

2021-05-06 09:19:08

如何在電源轉(zhuǎn)換應(yīng)用中實現(xiàn)高性能、成本優(yōu)化型實時控制設(shè)計

2021-03-16 07:56:20

的使用。下面就來分享構(gòu)建差動放大器及其性能優(yōu)化方法!儀表放大器可能不具備用戶要求的帶寬、直流精度或功耗。因而,在這種情況下,用戶可通過一個單放大器和外部電阻自行構(gòu)建差分放大器,以替代儀表放大器。不過,除非

2019-07-24 06:36:28

新型處理技術(shù)及其系統(tǒng)優(yōu)勢是還說呢么廢印制電路板的物理回收及綜合利用技術(shù)面臨的難點是什么?

2021-04-25 06:25:17

電磁波等能量。微波天線是微波通信系統(tǒng)收發(fā)設(shè)備的“出入口”,天線性能直接影響整個系統(tǒng)的運行。目前關(guān)于微波天線優(yōu)化的研究成果雖然很多,但多數(shù)均是從單一因素進(jìn)行考慮,優(yōu)化效果并不是非常理想,本文通過綜合考慮多種因素并優(yōu)化微波天線選擇參數(shù)來尋找更合理的選擇方法。

2019-06-11 07:25:18

微電網(wǎng)儲能優(yōu)化研究有何意義?微電網(wǎng)有哪些性能?如何去選取一種微電網(wǎng)優(yōu)化算法?什么是粒子群算法?

2021-07-06 06:34:20

怎么借助物理綜合提高FPGA設(shè)計效能?

2021-05-07 06:21:18

用Conformal做RTL和netlist的形式驗證,對比結(jié)果有很多報不等的是DC綜合被優(yōu)化掉的,conformal沒有識別出來這種優(yōu)化,請問需要設(shè)置什么可以解決這個問題?

2022-08-09 17:31:22

。由于主頻是芯片性能的重要指標(biāo)之一,如果希望關(guān)鍵路徑的延遲滿足芯片設(shè)計的周期時間,不但需要RTL 代碼描述滿足要求,更要講究綜合中對關(guān)鍵路徑的處理方法。關(guān)鍵字:邏輯綜合;后端設(shè)計(一)邏輯綜合的主要過程

2013-05-16 20:02:50

天線在移動通信系統(tǒng)中的作用好比人的眼睛和耳朵,好比足球隊的臨門一腳,其性能的好壞直接影響網(wǎng)絡(luò)覆蓋的效果,其可靠性屬于單點失效,會直接導(dǎo)致本扇區(qū)覆蓋失效。而如何準(zhǔn)確的測試及評估天線性能,目前仍存在一些問題需要探討及優(yōu)化。

2019-06-12 07:46:33

請問一下Arm Cortex-M85性能的提升是對總線進(jìn)行了優(yōu)化嗎?

2022-09-21 11:28:05

物理綜合與優(yōu)化的優(yōu)點是什么?物理綜合與優(yōu)化有哪些流程?物理綜合與優(yōu)化有哪些示例?為什么要通過物理綜合與優(yōu)化去提升設(shè)計性能?如何通過物理綜合與優(yōu)化去提升設(shè)計性能?

2021-04-14 06:52:32

如何通過LabVIEW優(yōu)化多核環(huán)境下的信號處理性能?

2021-04-09 06:49:51

通過誤差向量分析優(yōu)化接收機(jī)性能是什么?

2021-06-02 06:24:09

和性能。但是,在使用過程中,驅(qū)動器一旦出現(xiàn)故障,將影響整個控制系統(tǒng)的正常工作,因此,有必要設(shè)計研發(fā)出一種驅(qū)動器綜合性能測試系統(tǒng),來快速排除故障,確保控制系統(tǒng)性能品質(zhì)。

2019-09-20 07:29:21

需要開發(fā)者提供大致的優(yōu)化方針,甚至是明確的優(yōu)化仿真。 因此Xilinx的高層綜合工具提供了一系列性能評估的功能和向編譯器指向優(yōu)化方式的途徑。針對行為描述進(jìn)行行為綜合,可以獲取如下多種性能

2021-01-06 17:52:14

鴻蒙性能優(yōu)化寶藏指南:實戰(zhàn)工具與代碼案例解析

大家好呀!今天在翻鴻蒙開發(fā)者文檔時,意外挖到一個 性能優(yōu)化寶藏庫 ——原來官方早就提供了超多實用工具和案例,但很多小伙伴可能沒發(fā)現(xiàn)!這篇就帶大家手把手

2025-06-12 16:36:33

(視頻)使用NI Mu優(yōu)化電路設(shè)計性能PCB打樣找華強(qiáng) http://www.hqpcb.com/3 樣板2天出貨

2012-10-18 08:39:51

一:簡介4路E1+32路電話+2路千兆物理隔離網(wǎng)絡(luò)+4路百兆物理隔離網(wǎng)絡(luò)HY-4E132P2GL4FL-V雙光口1+1保護(hù)綜合業(yè)務(wù)光接入設(shè)備是漢源高科(北京)科技有限公司采用自主知識產(chǎn)權(quán)

2022-06-24 17:40:12

一:簡介8路E1+32路電話+2路千兆物理隔離網(wǎng)絡(luò)+4路百兆物理隔離網(wǎng)絡(luò)HY-8E132P2GL4FL-V雙光口1+1保護(hù)綜合業(yè)務(wù)光接入設(shè)備是漢源高科(北京)科技有限公司采用自主知識產(chǎn)權(quán)

2022-06-24 17:41:39

針對寬帶任意陣列天線的方向圖綜合問題,提出了基于凸優(yōu)化及其求解軟件的方向圖綜合方法。其中針對寬帶最低旁瓣方向圖綜合問題的特殊性,利用了凸優(yōu)化的優(yōu)良數(shù)值求解特

2009-07-30 15:01:22 15

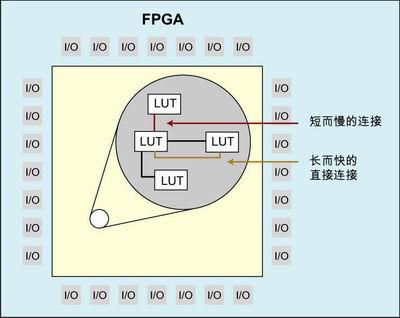

15 曾經(jīng)只能使用 ASIC 來實現(xiàn)的設(shè)計現(xiàn)在可以在可編程器件中實現(xiàn)了。最新的 90 nm Virtex-4 器件提供了超過200,000 個邏輯單元、6 MB 的塊 RAM 和接近 100 個 DSP 塊。創(chuàng)建能夠有效利用這些器件

2009-11-27 15:03:59 6

6 摘要:綜合(Synthesis)的主要功能是在FPGA設(shè)計過程中對設(shè)計輸入進(jìn)行分析和優(yōu)化。隨著FPGA技術(shù)的進(jìn)步,綜合技術(shù)也在不斷發(fā)展,不斷使用新技術(shù)的綜合工具軟件得到重視和使用,Pre

2010-06-07 10:42:50 16

16 磷酸亞鐵鋰的物理性能有哪些?

2009-10-29 10:27:44 573

573 借助物理綜合提高FPGA設(shè)計效能

隨著FPGA密度的增加,系統(tǒng)設(shè)計人員能夠開發(fā)規(guī)模更大、更復(fù)雜的設(shè)計,從而將密度優(yōu)勢發(fā)揮到最大。這些大規(guī)模設(shè)計基于這樣的設(shè)計需

2010-01-04 17:00:46 1450

1450

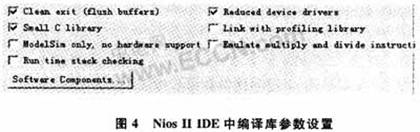

為了提高設(shè)計性能(有時甚至只是為了達(dá)到設(shè)計要求),對所設(shè)計的SOPC系統(tǒng)進(jìn)行綜合優(yōu)化是非常必要的。論文結(jié)合具體工程,以Altera公司的FPGA EP2S60為例,探討了SOPC系統(tǒng)設(shè)計的綜合優(yōu)

2010-06-01 08:10:23 885

885

綜合能源微網(wǎng)運行優(yōu)化調(diào)度方法研究_肖浩

2017-01-05 15:24:15 2

2 傳統(tǒng)的綜合技術(shù)越來越不能滿足當(dāng)今采用 90 納米及以下工藝節(jié)點實現(xiàn)的非常大且復(fù)雜的 FPGA 設(shè)計的需求了。問題是傳統(tǒng)的 FPGA 綜合引擎是基于源自 ASIC 的方法,如底層規(guī)劃、區(qū)域內(nèi)優(yōu)化

2018-11-28 08:12:00 1998

1998

物理優(yōu)化是Vivado實現(xiàn)流程中更快時序收斂的重要組成部分。

了解如何在Vivado中應(yīng)用此功能以交換運行時以獲得更好的設(shè)計性能。

2018-11-23 06:06:00 4544

4544 為了幫助全世界的現(xiàn)金中心安全地清分與處理紙幣,德國捷德貨幣技術(shù)公司的工程師與物理學(xué)家使用多物理場仿真開發(fā)了磁性、光學(xué)與超聲傳感器,從而對采用模塊化設(shè)計的高性能紙幣處理系統(tǒng)進(jìn)行了優(yōu)化。

2019-02-23 10:57:42 4013

4013 隨著傳統(tǒng)能源枯竭,為提高倛能經(jīng)濟(jì)性和效率,區(qū)琙綜合能源系統(tǒng)應(yīng)運而生,區(qū)堿綜合能源系統(tǒng)的優(yōu)化調(diào)度成為關(guān)鍵問題。由于多種能源之間存在耦合,多種能源的綜合需求響應(yīng)為區(qū)琙綜合能源系統(tǒng)的優(yōu)仳調(diào)度提供新的手段

2021-05-06 15:28:21 14

14 研究綜合能源系統(tǒng)的配置和優(yōu)化策略對于保障區(qū)域用能平衡、降低系統(tǒng)投資成本、提髙運行的經(jīng)濟(jì)性具有重要的意義和價值。提岀了含儲能裝置的園區(qū)型綜合能源系統(tǒng)的三級協(xié)同規(guī)劃方法,首先將綜合能源系統(tǒng)的設(shè)計過程劃分

2021-05-07 16:48:23 4

4 研究綜合能源系統(tǒng)的配置和優(yōu)化策略對于保障區(qū)域用能平衡、降低系統(tǒng)投資成本、提髙運行的經(jīng)濟(jì)性具有重要的意義和價值。提岀了含儲能裝置的園區(qū)型綜合能源系統(tǒng)的三級協(xié)同規(guī)劃方法,首先將綜合能源系統(tǒng)的設(shè)計過程劃分

2021-05-07 16:48:23 7

7 性能一直是華為非常專注的一個領(lǐng)域,華為通過HarmonyOS全棧的系統(tǒng)的技術(shù)加持和優(yōu)化,包括內(nèi)核層、硬件抽象層、runtime層、框架等等。各方面的努力,華為讓HarmonyOS的綜合性能比基于EMUI有了更大幅度的提升。

2021-06-03 09:08:05 3435

3435

隨著能源互聯(lián)網(wǎng)快速發(fā)展,其物理載體綜合能源系統(tǒng)成為未來能源利用的重要方弌。針對區(qū)堿綜合能源系統(tǒng)優(yōu)化調(diào)度問題,在實時電價的基礎(chǔ)上設(shè)定實時夭然氣價格策略,提岀一種基于實時定價機(jī)制的優(yōu)先級調(diào)度策略,建立

2021-06-18 11:23:59 7

7 綜合能源系統(tǒng)作為中囯建設(shè)清潔低碳、安全、髙效的現(xiàn)代能源體系的重要鉏成部分,其在系統(tǒng)模擬、優(yōu)化仿真等領(lǐng)域亟須改進(jìn)和完善,以便更好地服務(wù)于新型能源系統(tǒng)網(wǎng)絡(luò)場景應(yīng)用,攴撐中囯能源綠色發(fā)展戰(zhàn)略。因此

2021-06-18 16:19:07 21

21 基于綜合需求側(cè)響應(yīng)的多能存儲系統(tǒng)優(yōu)化

2021-07-05 15:50:39 18

18 利用工具將RTL代碼轉(zhuǎn)化為門級網(wǎng)表的過程稱為邏輯綜合。綜合一個設(shè)計的過程,從讀取RTL代碼開始,通過時序約束關(guān)系,映射產(chǎn)生一個門級網(wǎng)表。

2022-11-28 16:02:11 3757

3757 Vivado綜合默認(rèn)是timing driven模式,除了IO管腳等物理約束,建議添加必要的時序約束,有利于綜合邏輯的優(yōu)化,同時綜合后的design里面可以評估時序。

2023-07-03 09:03:19 1425

1425 引言綜合熱分析儀是一種多功能的熱學(xué)測量儀器,能夠同時測量樣品的多種熱學(xué)性能和物理性質(zhì)。它在材料科學(xué)、化學(xué)、冶金、生物醫(yī)學(xué)等領(lǐng)域中具有廣泛的應(yīng)用,為研究材料的性能和反應(yīng)過程提供了強(qiáng)有力的支持。本文將

2023-07-14 16:02:48 1634

1634

隨著數(shù)據(jù)倉庫規(guī)模的擴(kuò)大,數(shù)據(jù)倉庫的性能問題就顯得越來越突出,如何提高數(shù)據(jù)倉庫的性能,除了在設(shè)計階段對其邏輯結(jié)構(gòu)和物理結(jié)構(gòu)進(jìn)行優(yōu)化設(shè)計外;還可以在數(shù)據(jù)倉庫運行階段,采取一些優(yōu)化措施來使系統(tǒng)性能最佳

2023-07-18 16:10:37 0

0 電子發(fā)燒友網(wǎng)站提供《GPRS的性能分析及優(yōu)化.pdf》資料免費下載

2023-11-17 16:31:08 0

0 MySQL 性能優(yōu)化是一項關(guān)鍵的任務(wù),可以提高數(shù)據(jù)庫的運行速度和效率。以下是一些優(yōu)化方法,包括具體代碼和詳細(xì)優(yōu)化方案。

2023-11-22 09:59:15 1347

1347 優(yōu)化Buck-Boost型變換器的性能是一個綜合性的任務(wù),涉及電路設(shè)計、元件選擇、控制策略、保護(hù)機(jī)制等多個方面。以下將從這些方面詳細(xì)闡述如何優(yōu)化Buck-Boost型變換器的性能。

2024-08-14 14:09:00 2048

2048 優(yōu)化Linux服務(wù)器的性能是一個綜合性的任務(wù),涉及硬件、軟件、配置、監(jiān)控等多個方面。以下是一個詳細(xì)的指南,旨在幫助系統(tǒng)管理員和運維人員提升Linux服務(wù)器的性能和穩(wěn)定性。

2024-09-29 16:50:20 1292

1292 優(yōu)化FPGA(現(xiàn)場可編程門陣列)設(shè)計的性能是一個復(fù)雜而多維的任務(wù),涉及多個方面和步驟。以下是一些關(guān)鍵的優(yōu)化策略: 一、明確性能指標(biāo) 確定需求 :首先,需要明確FPGA設(shè)計的性能指標(biāo),包括時鐘頻率

2024-10-25 09:23:38 1456

1456 優(yōu)化SOC(System on Chip,系統(tǒng)級芯片)芯片性能是一個復(fù)雜而多維的任務(wù),涉及多個方面的優(yōu)化策略。以下是一些關(guān)鍵的優(yōu)化措施: 一、架構(gòu)設(shè)計優(yōu)化 核心選擇與配置 :根據(jù)應(yīng)用需求選擇適當(dāng)

2024-10-31 15:50:19 2736

2736 優(yōu)化DCS(分布式控制系統(tǒng))系統(tǒng)的性能是確保工業(yè)自動化過程高效、穩(wěn)定運行的關(guān)鍵。以下是一些具體的優(yōu)化措施: 一、硬件優(yōu)化 設(shè)備選擇與升級 :檢查并確保DCS系統(tǒng)的硬件設(shè)備符合規(guī)格要求,并處于良好

2024-11-13 09:19:19 2112

2112 優(yōu)化MEMS(微機(jī)電系統(tǒng))設(shè)計以提高性能是一個復(fù)雜且多維的任務(wù),涉及多個學(xué)科和技術(shù)的綜合應(yīng)用。以下是一些關(guān)鍵的優(yōu)化策略和方法: 一、系統(tǒng)級設(shè)計優(yōu)化 明確功能需求和技術(shù)指標(biāo) : 在設(shè)計之初,需要明確

2024-11-20 10:21:30 2023

2023 七層模型的各個層次,可以顯著提升網(wǎng)絡(luò)性能。以下是通過OSI七層模型優(yōu)化網(wǎng)絡(luò)性能的具體方法: 一、物理層優(yōu)化 物理層是OSI模型的最底層,負(fù)責(zé)定義物理介質(zhì)傳輸數(shù)據(jù)的方式和規(guī)范。在物理層進(jìn)行優(yōu)化,可以通過改善物理介質(zhì)和傳輸設(shè)備來提高數(shù)據(jù)傳輸?shù)乃俾屎头€(wěn)定性。 使用更高帶

2024-11-24 11:14:25 1820

1820 在現(xiàn)代工業(yè)和科學(xué)研究中,仿真系統(tǒng)扮演著越來越重要的角色。它們不僅能夠幫助我們預(yù)測復(fù)雜系統(tǒng)的行為,還能在沒有實際物理原型的情況下進(jìn)行實驗和測試。然而,隨著仿真模型的復(fù)雜度增加,性能優(yōu)化成為了一個不可

2024-12-19 14:47:10 4388

4388 MPLS(多協(xié)議標(biāo)簽交換)網(wǎng)絡(luò)性能優(yōu)化是一個復(fù)雜的過程,涉及多個方面的技術(shù)和策略。以下是一些關(guān)鍵的MPLS網(wǎng)絡(luò)性能優(yōu)化技巧: 一、確保網(wǎng)絡(luò)設(shè)備支持 設(shè)備兼容性 :確保所有網(wǎng)絡(luò)設(shè)備(如路由器、交換機(jī)等

2025-02-14 17:09:18 1571

1571 理解并掌握先進(jìn)的時鐘設(shè)計策略。 下圖展示了典型的時鐘樹結(jié)構(gòu)(Clock Tree),用于平衡時鐘延遲與偏斜。 2、核心技術(shù)詳解 I. CTS 優(yōu)化:消除時序違例的第一步 時鐘樹綜合(CTS) 是物理設(shè)計中構(gòu)建平衡時鐘網(wǎng)絡(luò)的關(guān)鍵步驟,通過插入緩沖器和反相器,實現(xiàn)最

2025-10-09 10:07:29 361

361

電子發(fā)燒友App

電子發(fā)燒友App

評論