優化SOC(System on Chip,系統級芯片)芯片性能是一個復雜而多維的任務,涉及多個方面的優化策略。以下是一些關鍵的優化措施:

一、架構設計優化

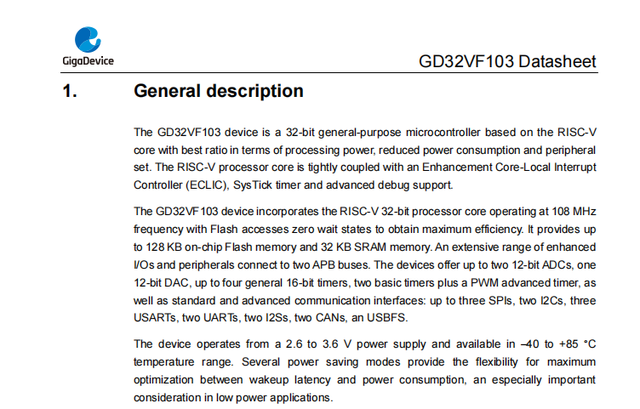

- 核心選擇與配置 :根據應用需求選擇適當的核心數量、頻率和架構。例如,對于高性能計算應用,可能需要高頻率、多核心的設計;而對于低功耗應用,則可能需要優化功耗效率的核心。

- 總線與接口優化 :優化芯片內部的總線結構和接口設計,以減少數據傳輸延遲和提高帶寬。

二、并行計算優化

- 多核心并行 :利用多核心并行計算的能力,通過合理分配任務和資源,實現更高效的計算。這可以通過使用并行編程模型(如OpenMP、CUDA等)來實現。

- 數據并行與任務并行 :根據應用特點選擇合適的并行策略,如數據并行或任務并行,以充分利用多核心的優勢。

三、算法與數據優化

- 算法優化 :針對特定應用對算法進行優化,以減少計算量和內存帶寬需求。這可能包括減少冗余計算、降低存儲器訪問次數、優化循環結構等。

- 數據局部性優化 :通過提高數據局部性,減少數據在內存中的訪問次數。這可以通過使用高效的數據結構和算法、數據緩存技術等來實現。

四、內存帶寬優化

- 內存對齊與向量化 :確保數據在內存中的地址對齊,并使用SIMD(Single Instruction Multiple Data)指令集進行并行處理。

- 緩存優化 :增加緩存容量或改進緩存替換策略,以提高緩存命中率。同時,合理分配片上內存(如SRAM),以減少對外部DRAM的訪問。

- 內存訪問模式優化 :采用批量訪問、交錯訪問等模式,減少內存帶寬瓶頸。

五、能耗管理優化

- 動態功耗調整 :通過動態調整核心頻率和電壓、使用休眠/喚醒機制等策略,根據實際需求在保證性能的同時降低能耗。

- 低功耗技術 :應用多閾值電壓、門控時鐘、多電壓設計、門控電源等低功耗技術,進一步降低芯片的靜態和動態功耗。

六、物理布局與布線優化

- 物理布局設計 :合理的物理布局設計可以減少信號傳輸延遲和功耗。這包括優化芯片的布線結構、位置規劃、供電網絡設計等。

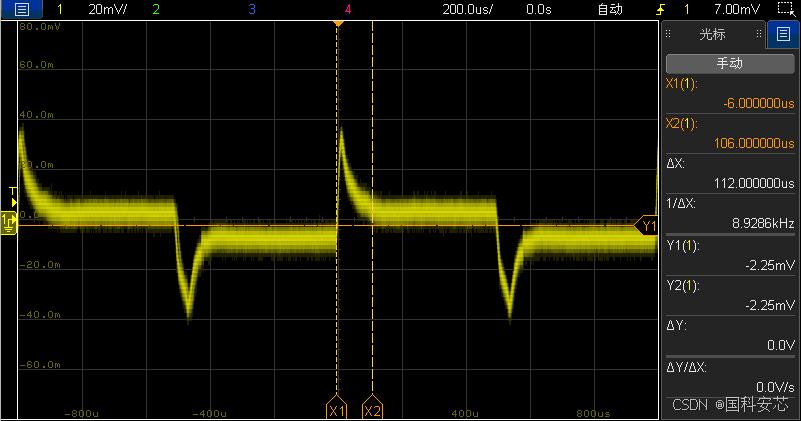

- 信號完整性優化 :確保信號在傳輸過程中的完整性和穩定性,以減少信號失真和噪聲干擾。

七、軟件與編譯器優化

- 編譯器優化 :使用支持自動向量化和循環展開的編譯器,以提高代碼的執行效率。

- 軟件算法優化 :在軟件層面針對特定應用進行算法優化,以減少計算量和內存訪問次數。

綜上所述,優化SOC芯片性能需要從架構設計、并行計算、算法與數據、內存帶寬、能耗管理、物理布局與布線以及軟件與編譯器等多個方面進行綜合考慮和優化。這些優化措施的選擇和實施應根據具體的應用場景和需求進行,以實現最佳的性能和功耗表現。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

接口

+關注

關注

33文章

9521瀏覽量

157044 -

數據

+關注

關注

8文章

7335瀏覽量

94777 -

頻率

+關注

關注

4文章

1585瀏覽量

62072 -

SoC芯片

+關注

關注

2文章

669瀏覽量

37166

發布評論請先 登錄

相關推薦

熱點推薦

Altera Agilex 3 FPGA和SoC產品家族的性能分析

本文采用嚴謹的基準測試方法,對全新推出的 Agilex 3 FPGA 和 SoC 產品家族進行性能分析。該系列專為成本優化型應用設計,兼具高性能、高集成度與高可靠性。

AT6558--北斗定位芯片 一款高性能 BDS/GNSS 多模衛星導航接收機 SOC 單芯片

一、AT6558的由來:

AT6558 是一款高性能 BDS/GNSS 多模衛星導航接收機 SOC 單芯片,采用 55nm CMOS工藝,片上集成射頻前端,數字基帶處理器,32位的 RISC CPU

發表于 09-29 09:54

AUDIO SoC的解決方案

SoC(片上系統)是一種系統級集成電路。新唐科技的單芯片音頻系統音頻 SoC采用皮質-M0/M4內核,并采用Arm 皮質-M系列處理器的基本創新技術,包括∑△ADC、CODEC、OP、Class D

發表于 09-05 08:26

mcu芯片和soc芯片的區別解析

MCU(微控制器單元)和SoC(系統級芯片)是兩種常見的芯片類型,它們在設計目標、應用場景和功能集成上有顯著區別。以下是主要差異的總結: 1. 核心結構與功能 MCU(Microcontroller

基于 ASP3605 電源芯片的性能優化與 ITH 調試策略

摘要: 在電源設計領域,電源轉換器的穩定性與高效性對于其性能表現具有決定性意義。ASP3605 作為一款高效同步降壓轉換器,具備多種調節功能,為電源性能優化提供了廣闊空間。本文聚焦于 ASP3605

鴻蒙5開發寶藏案例分享---Grid性能優化案例

發現鴻蒙寶藏:優化Grid組件性能的實戰技巧!

大家好呀!最近在鴻蒙開發者社區挖到一個超實用的性能優化案例—— 解決Grid組件加載慢、滾動卡頓的問題 。官方其實藏了不少寶藏案例,但很

發表于 06-12 17:47

鴻蒙5開發寶藏案例分享---性能優化案例解析

鴻蒙性能優化寶藏指南:實戰工具與代碼案例解析

大家好呀!今天在翻鴻蒙開發者文檔時,意外挖到一個 性能優化寶藏庫 ——原來官方早就提供了超多實用工具和案例,但很多小伙伴可能沒發現!這篇就

發表于 06-12 16:36

主流物聯網(IoT)SoC芯片廠商與產品盤點(2025年5)

主流物聯網(IoT)SoC芯片廠商與產品盤點(2025年) 一、國際巨頭:技術引領與生態壟斷 高通(Qualcomm) 核心產品 :驍龍8 Elite、驍龍X平臺 采用臺積電3nm制程,集成

HarmonyOS優化應用內存占用問題性能優化一

應用開發過程中注重內存管理,積極采取措施來減少內存占用,以優化應用程序的性能和用戶體驗。

HarmonyOS提供了一些內存管理的工具和接口,幫助開發者有效地管理內存資源:

onMemoryLevel接口

發表于 05-21 11:27

新品發布!國民技術推出高性能多協議快充協議SoC芯片

近日,國民技術電源管理產品再添新成員,正式發布高性能多協議快充協議SoC芯片(NP11/NP12/NP21系列),采用Arm內核,基于Flash工藝設計,產品可支持PD/QC/UFCS/APPPLE

AI眼鏡的未來:SoC芯片與SD NAND的協同優化

AI眼鏡正以驚人的速度從概念走向現實。據行業預測,全球AI眼鏡出貨量將在2026年突破1000萬副,2030年更將飆升至8000萬副,市場規模超百億美元。這一變革的背后,是兩大核心技術——MK米客方德SD NAND存儲芯片與紳聚高性能S

如何優化SOC芯片性能

如何優化SOC芯片性能

評論